中断屏蔽实现方法-ARM内核

文章目录

- 前言

- 寄存器定义

- SHPR-System Handler Priority Registers

- BASEPRI-Base Priority Mask Register

- PRIMASK-Priority Mask Register

- FAULTMASK-Fault Mask Register

- 总结

前言

之前一直搞不清OS中屏蔽中断和开中断是如何实现的,导致部分中断没有在OS中配置而引发了一些临界区的问题,本文介绍ARM内核手册中的相关寄存器的定义

寄存器定义

先来认识下几个相关的寄存器

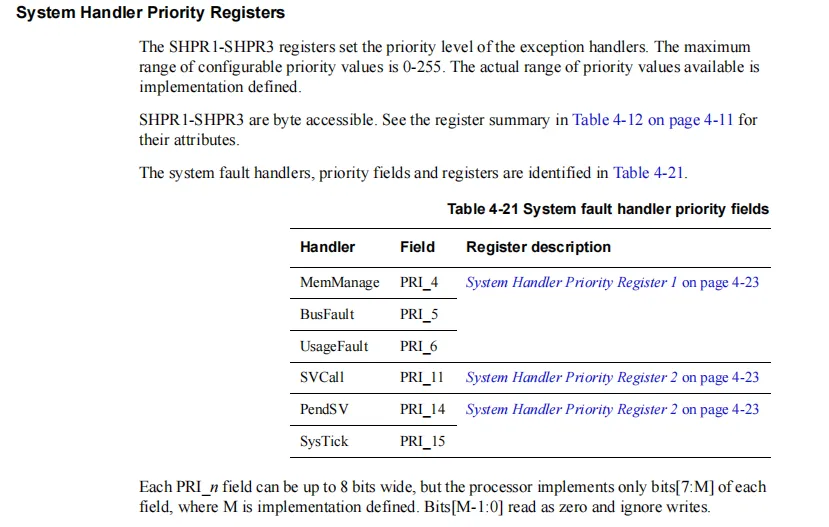

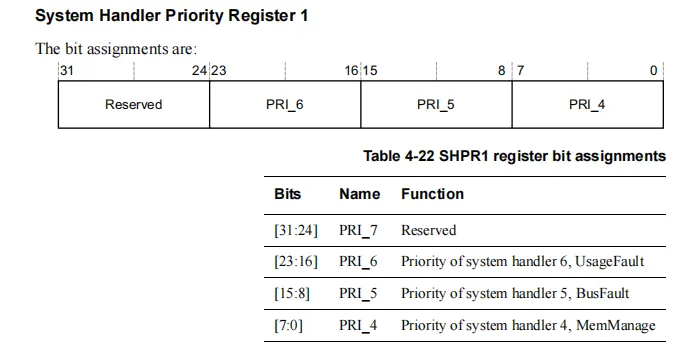

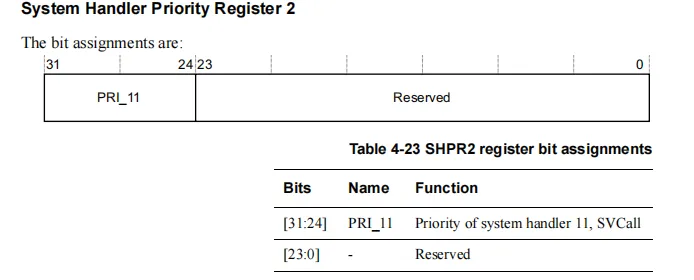

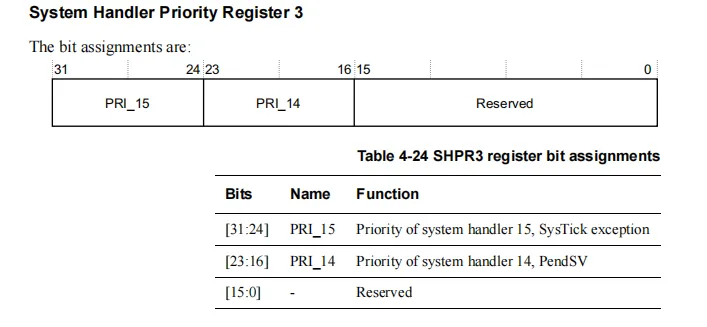

SHPR-System Handler Priority Registers

对应系统中断的优先级设置,有三个寄存器

此处的优先级值越小,优先级越高,需要注意的是,如果只有0-15个优先级,则取的是高4位,低四位一直为0且写值是无效的

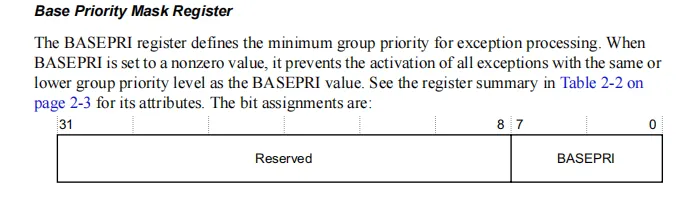

BASEPRI-Base Priority Mask Register

该寄存器用来屏蔽优先级等于或低于设置值的中断

例如,配置为0x30时,则0x30-0xff优先级的中断会被屏蔽

如果只用了高4位,则屏蔽优先级0x3-0xf的中断

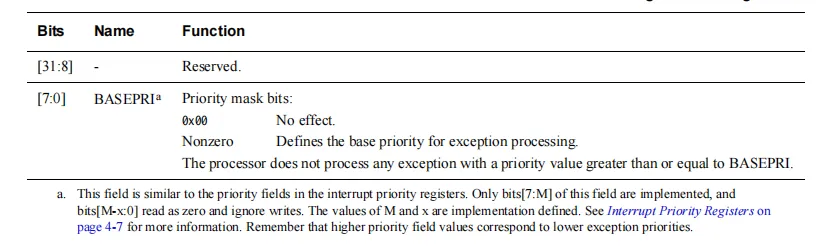

PRIMASK-Priority Mask Register

当设置为1时,屏蔽所有可配置中断(除了NMI和Hardfault)

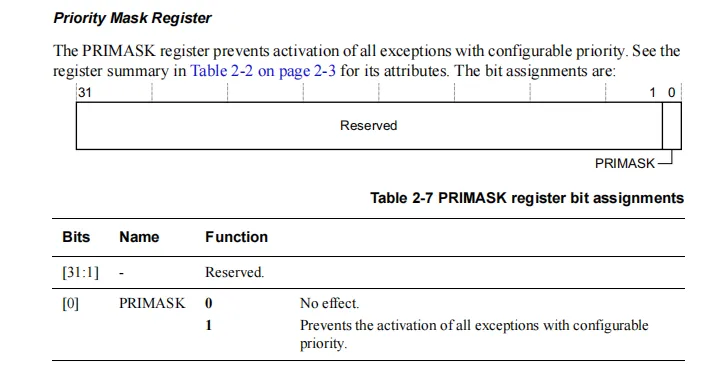

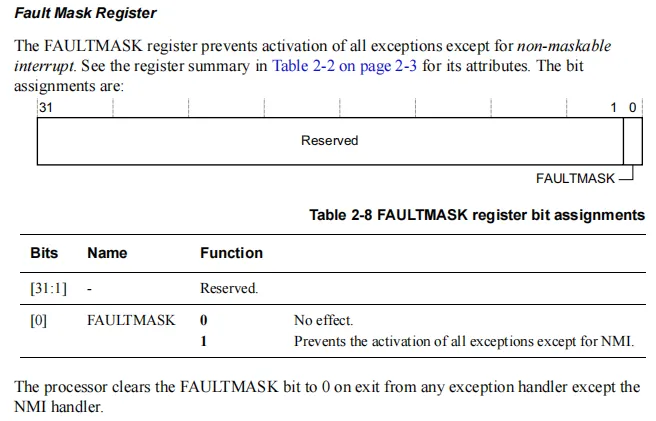

FAULTMASK-Fault Mask Register

当设置为1时,屏蔽除了NMI之外的所有中断

总结

在ARM汇编语言中,经常会看到cpsid和cpsie,其实cpsid对应的就是关中断,cpsie对应的是开中断,其后一般会跟i或者f或者if,i表示的就是PRIMASK,f表示的是FAULTMASK,cpsid if实际就是将PRIMASK和FAULTMASK都置1,cpsie if则是将他俩都置0,不过这两种方式都是比较粗暴的,OS中一般不这么使用