【硬件-笔试面试题-92】硬件/电子工程师,笔试面试题(知识点:米勒效应,米勒平台)

题目汇总版--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客

【硬件-笔试面试题-92】硬件/电子工程师,笔试面试题(知识点:米勒效应,米勒平台)

1、题目

米勒效应,米勒平台

2、知识点

米勒效应(Miller Effect)是高频电子电路中一种重要的寄生电容影响现象,由美国工程师约翰・米尔顿・米勒(John Milton Miller)于 1920 年提出。它描述了放大器中输入电容因电压放大作用而等效增大的现象,会显著影响电路的高频性能,是高频设计中必须考虑的关键问题。

一、米勒效应的本质

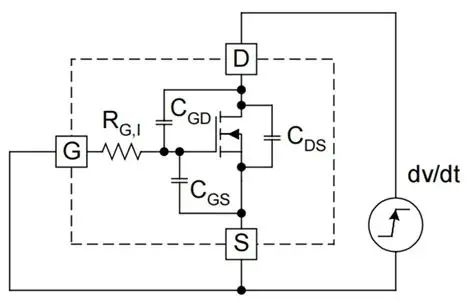

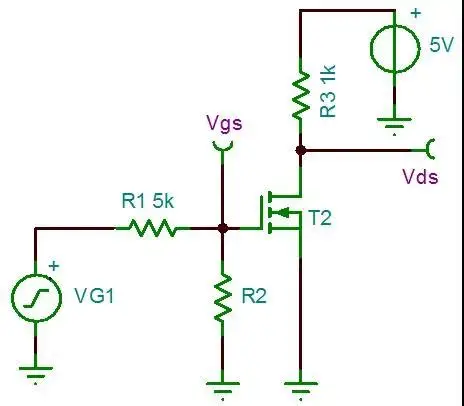

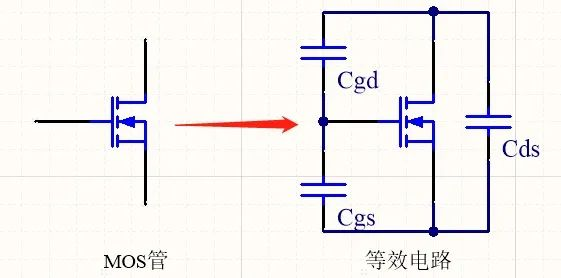

在共射(或共源)放大电路中,晶体管(BJT 或 MOS 管)的输出端与输入端之间存在寄生电容(如 BJT 的集电结电容\(C_{bc}\),MOS 管的栅漏电容\(C_{gd}\))。当电路工作在高频时,这一电容会因输出与输入之间的电压放大作用,在输入端呈现出等效电容增大的现象,即米勒效应。

核心原理:

设晶体管的输入输出间寄生电容为C,电压放大倍数为\(A_v\)(输出电压与输入电压的比值,通常为负值,因共射电路反相),则输入端的等效米勒电容\(C_{M}\)为:\(C_M = C \times (1 - A_v)\)

- 对于共射放大器,\(A_v\)为负值(如\(A_v = -100\)),则\(C_M = C \times (1 + |A_v|)\),即等效电容是原电容的\((1 + |A_v|)\)倍。

- 例如:若\(C = 1pF\),\(|A_v| = 100\),则\(C_M = 101pF\),寄生电容被放大了 100 倍。

二、米勒效应的产生条件

米勒效应的产生需要两个关键条件:

- 存在跨接于输入与输出之间的电容(可以是器件寄生电容,也可以是分布电容);

- 电路具有电压放大作用(输入与输出之间存在电压增益\(A_v \neq 0\))。

这两个条件在大多数放大器(如共射、共源放大电路)中天然存在,因此米勒效应是高频放大电路中的普遍现象。

三、对电路性能的影响

米勒效应的核心危害是增大输入端等效电容,进而影响电路的高频响应:

-

降低带宽: 输入端的等效米勒电容\(C_M\)会与信号源内阻\(R_s\)形成 RC 低通滤波网络(时间常数\(\tau = R_s \times C_M\)),导致高频信号衰减,使放大器的带宽(截止频率)降低。 截止频率计算公式:\(f_H \approx \frac{1}{2\pi R_s C_M}\),\(C_M\)越大,\(f_H\)越低。

-

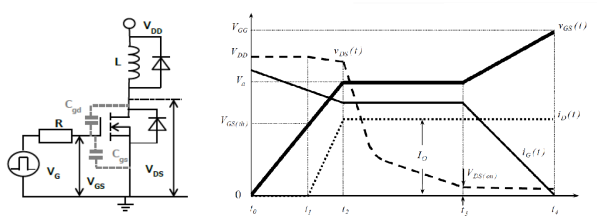

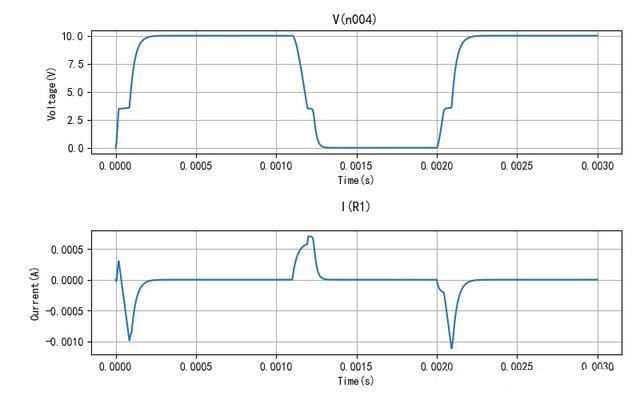

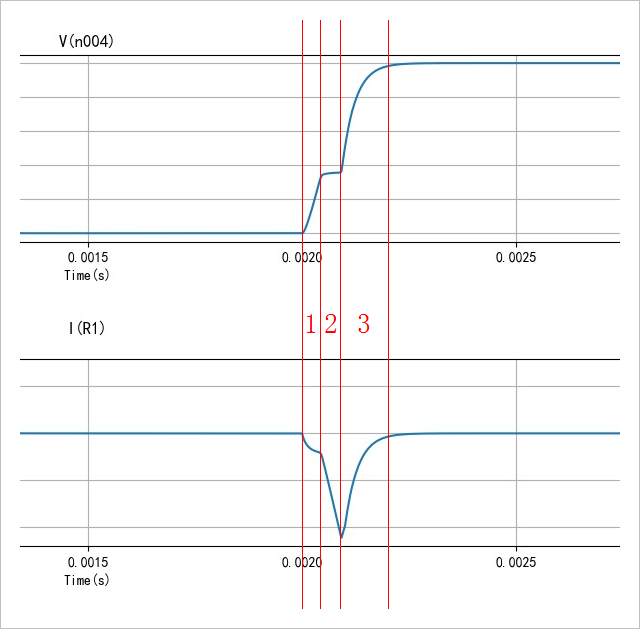

增加信号延迟: 米勒电容的充放电需要时间,会导致输入信号的相位延迟,尤其在高速开关电路(如数字逻辑门、高频脉冲放大)中,可能引发信号失真。

-

降低输入阻抗: 高频时,电容的容抗\(X_C = \frac{1}{2\pi f C_M}\)随频率升高而减小,导致放大器的输入阻抗下降,加重信号源的负载。

四、抑制米勒效应的方法

在高频电路设计中,需通过以下手段减小米勒效应的影响:

-

采用共基极(或共栅极)组态: 共基极电路中,晶体管的基极(或栅极)接地,输入信号加在发射极(或源极),输出信号从集电极(或漏极)取出。此时,输入与输出之间的寄生电容跨接于低阻抗节点(发射极)和高阻抗节点(集电极),电压增益\(A_v \approx 1\)(无电压放大),米勒效应几乎可以忽略。

- 优势:共基极电路带宽远高于共射电路,适合高频放大(如射频电路)。

-

使用屏蔽和隔离技术: 减少输入与输出端之间的分布电容(如 PCB 布线时避免输入线与输出线平行,增加间距或加接地屏蔽层),从源头降低跨接电容C。

-

采用负反馈补偿: 通过外部电路引入负反馈,降低输入输出之间的有效电压增益\(A_v\),从而减小米勒电容\(C_M = C(1 - A_v)\)。

-

拆分电容(米勒分裂技术): 在高频功率放大电路中,通过在晶体管的输入输出端之间串联电阻,将寄生电容 “分裂” 为两个较小的电容,分别等效到输入和输出端,降低对输入端的影响。

-

选用高频特性好的器件: 选择寄生电容(如\(C_{bc}\)、\(C_{gd}\))小的高频晶体管(如射频 BJT、GaN MOS 管),从器件层面减小米勒效应的基础。

五、典型应用场景与案例

-

高频放大器设计: 共射放大器在低频时增益高,但高频因米勒效应带宽受限;而共基放大器无米勒效应,适合作为高频信号的缓冲或放大(如电视机的高频头电路)。

-

数字逻辑门: CMOS 反相器中,栅漏电容\(C_{gd}\)会产生米勒效应,导致开关速度下降。因此,高速数字电路(如 GHz 级 CPU)需通过优化器件结构(减小\(C_{gd}\))和布线来抑制米勒效应。

-

射频电路: 在射频功率放大器中,米勒效应会导致输入阻抗随频率变化,影响阻抗匹配,需通过上述米勒分裂技术或共基组态优化。

总结

米勒效应是高频电路中因寄生电容和电压放大共同作用导致的输入电容等效增大现象,主要危害是降低带宽、增加延迟。理解其原理后,可通过选择合适的电路组态(如共基极)、优化器件和布线、采用补偿技术等方式抑制其影响,这对高频电子设计(如通信、雷达、高速数字电路)至关重要。

题目汇总--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客