基于FPGA的图像中值滤波算法Verilog开发与开发板硬件测试

目录

1.前言

2.算法硬件测试效果图预览

3.算法运行软件版本

4.部分核心程序

5.算法仿真参数

6.硬件测试说明

7.算法理论概述

8.参考文献

9.算法完整程序工程

1.前言

基于FPGA的图像中值滤波是一种在图像处理中常用的滤波技术,其原理是通过一定的算法将图像中的噪声平滑掉,同时尽量保留图像的细节信息。该技术主要应用于图像降噪、图像增强等领域。中值滤波是一种非线性信号处理技术,其原理是将图像中每个像素点的值设置为该点周围邻居像素值的中值。具体来说,对于一个像素点,其滤波后的值等于该点周围邻居像素值排序后的中间值。这种滤波方法可以有效去除图像中的椒盐噪声、孤立点等,同时能够保留图像的边缘信息。

————————————————

本课题为之前博客中写的文章的硬件调试:

https://blog.csdn.net/aycd1234/article/details/132654299?spm=1011.2415.3001.5331

在仿真版本的基础上,我们增加了图像存储模块,HDMI接口模块,图像时序处理模块,rgb转dvi模块等。

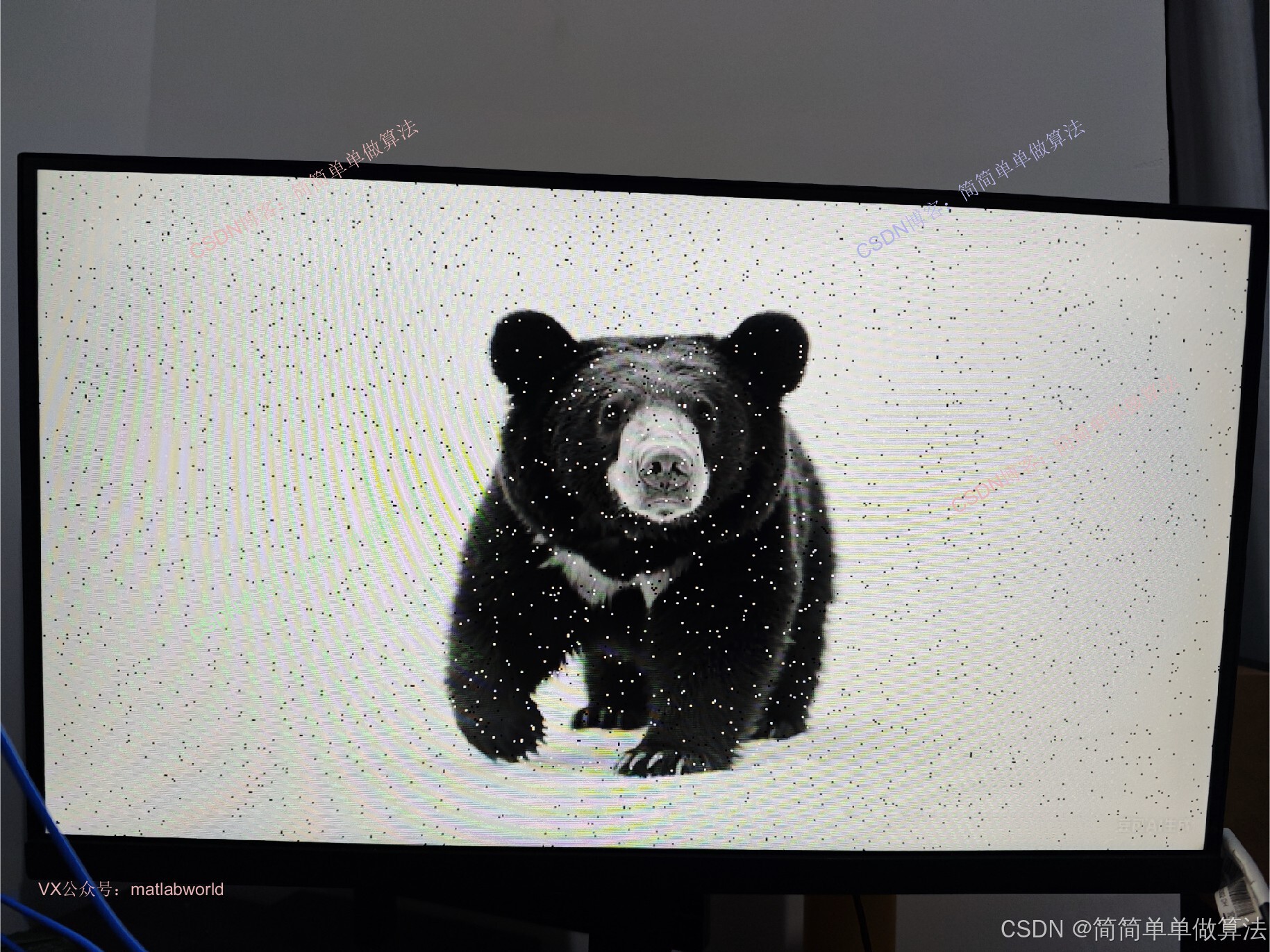

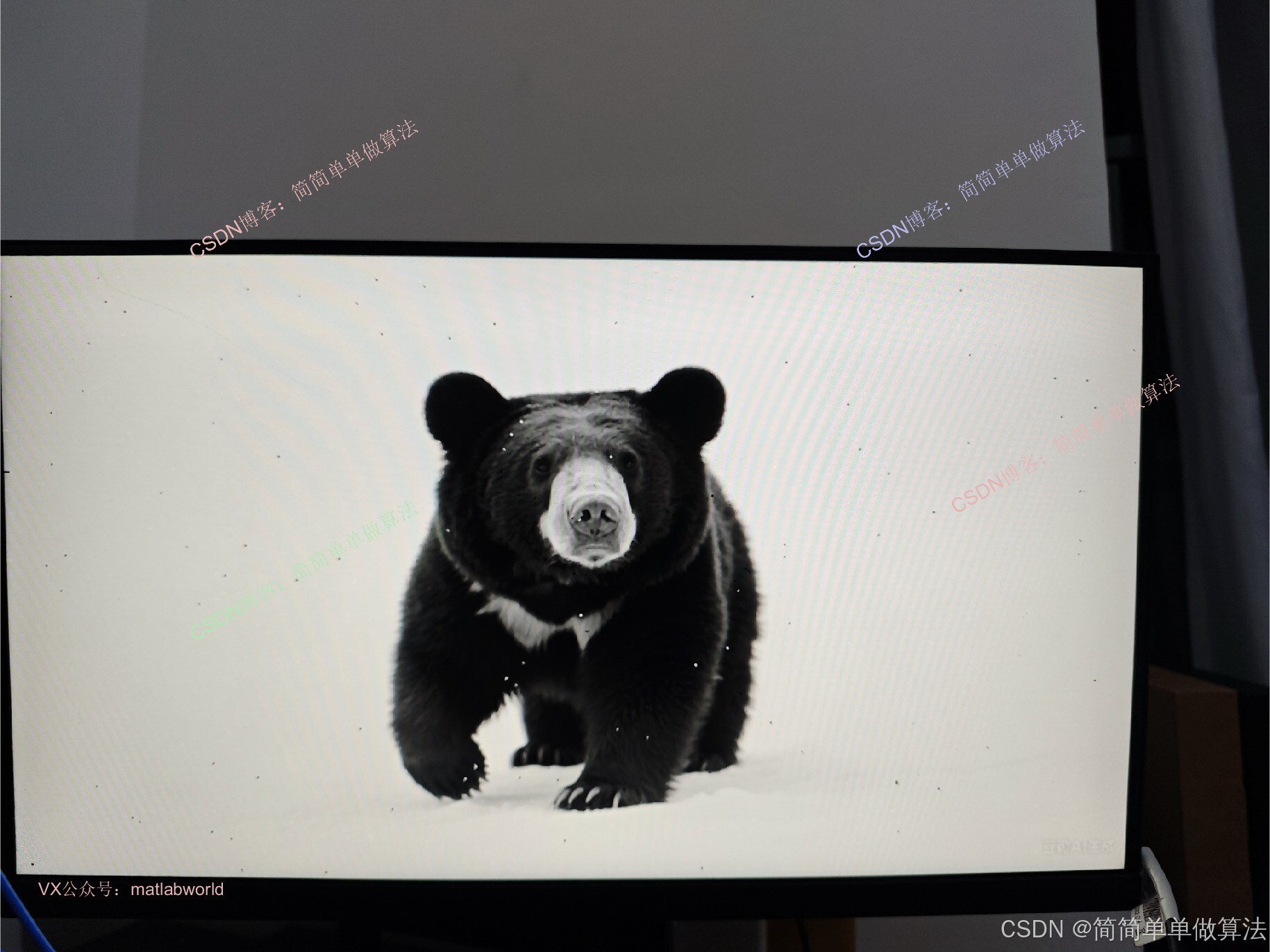

2.算法硬件测试效果图预览

滤波前

滤波后

3.算法运行软件版本

vivado2022.2

Matlab2022a/matlab2024b

4.部分核心程序

(完整版代码包含中文注释和操作步骤视频)

color_bar hdmi_color_bar(.clk(video_clk),.rst(1'b0),.key(key),.hs(video_hs),.vs(video_vs),.de(video_de),.rgb_r(video_r),.rgb_g(video_g),.rgb_b(video_b)

);video_clock video_clock_m0

(// Clock in ports.clk_in1(sys_clk),// Clock out ports.clk_out1(video_clk),.clk_out2(video_clk_5x),// Status and control signals.reset(1'b0),.locked());rgb2dvi_0 rgb2dvi_m0 (// DVI 1.0 TMDS video interface.TMDS_Clk_p(TMDS_clk_p),.TMDS_Clk_n(TMDS_clk_n),.TMDS_Data_p(TMDS_data_p),.TMDS_Data_n(TMDS_data_n),.oen(hdmi_oen),//Auxiliary signals .aRst_n(1'b1), //-asynchronous reset; must be reset when RefClk is not within spec// Video in.vid_pData({video_r,video_g,video_b}),.vid_pVDE(video_de),.vid_pHSync(video_hs),.vid_pVSync(video_vs),.PixelClk(video_clk),.SerialClk(video_clk_5x)// 5x PixelClk

); endmodule

0X2_002m5.算法仿真参数

parameter H_ACTIVE = 16'd1280; //horizontal active time (pixels)

parameter H_FP = 16'd110; //horizontal front porch (pixels)

parameter H_SYNC = 16'd40; //horizontal sync time(pixels)

parameter H_BP = 16'd220; //horizontal back porch (pixels)

parameter V_ACTIVE = 16'd720; //vertical active Time (lines)

parameter V_FP = 16'd5; //vertical front porch (lines)

parameter V_SYNC = 16'd5; //vertical sync time (lines)

parameter V_BP = 16'd20; //vertical back porch (lines)

parameter HS_POL = 1'b1; //horizontal sync polarity, 1 : POSITIVE,0 : NEGATIVE;

parameter VS_POL = 1'b1; //vertical sync polarity, 1 : POSITIVE,0 : NEGATIVE;6.硬件测试说明

具体的硬件操作步骤,可以参考作品中提供的视频步骤

如果不同开发板,系统的移植可以参考如下文章

不同FPGA开发板系统移植步骤-CSDN博客

7.算法理论概述

基于FPGA的图像中值滤波是一种在图像处理中常用的滤波技术,其原理是通过一定的算法将图像中的噪声平滑掉,同时尽量保留图像的细节信息。该技术主要应用于图像降噪、图像增强等领域。中值滤波是一种非线性信号处理技术,其原理是将图像中每个像素点的值设置为该点周围邻居像素值的中值。具体来说,对于一个像素点,其滤波后的值等于该点周围邻居像素值排序后的中间值。这种滤波方法可以有效去除图像中的椒盐噪声、孤立点等,同时能够保留图像的边缘信息。

在基于FPGA的图像中值滤波中,FPGA作为硬件平台,可以实现高速的并行计算,从而提高滤波效率。通常,FPGA上会设计一个专门的中值滤波器模块,该模块包含了用于排序的比较器和存储器。中值滤波的数学表达式为:

Median(f(x,y)) = median(g(x-i,y-j) for all i,j around (x,y)

其中,f(x,y)表示原始图像,g(x-i,y-j)表示滤波后的图像,i和j表示像素坐标。在实际应用中,通常采用滑动窗口的方式来实现中值滤波,窗口大小和步长可以根据实际需求进行调整。基于FPGA的图像中值滤波开发主要包括以下几个步骤:

1.算法设计:根据需求选择合适的中值滤波算法,并根据FPGA的特点进行算法优化。

2.硬件设计:根据算法设计,使用硬件描述语言(如VHDL或Verilog)设计FPGA的硬件结构。

3.硬件仿真与验证:使用仿真工具对设计的硬件结构进行仿真验证,以确保其正确性和性能满足要求。

4.硬件实现:将设计的硬件结构下载到FPGA上,并进行实际测试和调试。

5.系统集成:将FPGA中实现的图像中值滤波模块集成到整个图像处理系统中,并进行系统测试和优化。

总的来说,基于FPGA的图像中值滤波开发需要具备一定的硬件设计和图像处理知识,以及对FPGA开发流程的熟悉。在实际开发过程中,还需要根据具体需求进行算法优化和硬件设计优化,以提高系统的性能和稳定性。

8.参考文献

[1]吴少群,栗加顺,王竹,等.中值滤波的FPGA实现[J].首都师范大学学报:自然科学版, 2007, 28(6):3.DOI:10.3969/j.issn.1004-9398.2007.06.007.

[2]李雷鸣,张焕春,张波.一种基于FPGA的图像中值滤波器的硬件实现[J].信息化研究, 2004, 30(2):48-50.DOI:10.3969/j.issn.1674-4888.2004.02.015.

[3]李元帅,张勇,周国忠,等.图像中值滤波硬件算法及其在FPGA中的实现[J].计算机应用, 2006, 26(B06):3.DOI:JournalArticle/5ae97ef3c095d713d88e6625.

9.算法完整程序工程

OOOOO

OOO

O