STM32F103C8T6_IIC协议详解

STM32F103C8T6 IIC协议详解:从原理到实战应用

IIC协议基础原理

图5:I2C通信正常(左)与断开(右)状态的示波器波形对比,蓝色为数据线(SDA),青色为时钟线(SCL)。

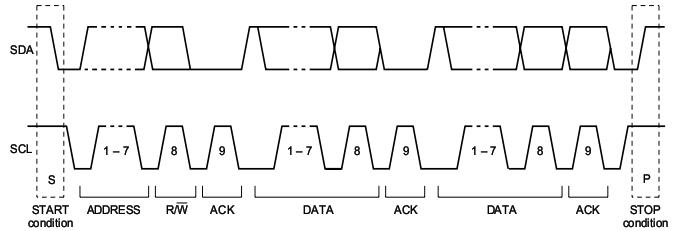

图1:I2C协议完整时序波形,标注了起始条件(S)、地址传输(ADDRESS)、读/写控制位(R/W)、应答位(ACK)、数据传输(DATA)及停止条件§。

I2C(Inter-Integrated Circuit)通信协议是一种多主机、多从机的串行通信总线,仅通过两条信号线——串行数据线(SDA)和串行时钟线(SCL)实现数据传输,其核心优势在于简化硬件连接的同时支持多设备挂载1。该协议的底层原理可通过物理层、协议层和时序逻辑三层结构进行系统解析。

物理层:开漏输出与总线拓扑

物理层采用开漏输出和上拉电阻的设计确保总线电气特性稳定。所有设备的SCL和SDA引脚均配置为开漏输出模式,这意味着任何设备都只能将线路拉低至低电平(逻辑0),而高电平状态(逻辑1)需通过上拉电阻维持12。典型的上拉电阻阻值为4.7kΩ,当无设备驱动总线时,电阻将SDA和SCL线拉高至空闲状态23。这种设计天然避免了总线冲突:多个设备同时输出时,"线与"逻辑确保只有低电平状态会被传递,高电平输出将被其他设备的低电平覆盖4。物理拓扑上,所有设备的SCL和SDA线分别并联,形成多主多从的总线结构,为主机与从机间的灵活通信奠定硬件基础25。

关键问题:为什么需要上拉电阻?

开漏输出的MOS管仅能提供下拉电流,无法主动输出高电平。上拉电阻的作用是:

维持总线空闲时的高电平状态

确保多个设备同时驱动时的逻辑正确性

限制总线电流,保护芯片引脚

协议层:地址机制与应答交互

协议层通过地址寻址和应答机制实现可靠数据传输。I2C支持7位或10位地址格式,其中7位地址最为常用,可理论支持128个设备(实际保留部分地址用于特殊功能)46。地址字节的最高位(第8位)定义读写方向:0表示写操作,1表示读操作17。通信过程中,主机发送地址后,总线上所有从机将接收到的地址与自身地址比对,匹配者通过应答信号(ACK)确认响应8。应答信号是数据完整性的关键保障:接收方在每个字节传输后,需在第9个时钟周期将SDA拉低(ACK),若未拉低(NACK)则表示接收失败,主机需终止传输89。

数据帧格式遵循"起始信号-地址字节-数据字节-应答位-停止信号"的结构。以写操作为例,主机先发送起始信号,随后传输从机地址+写位(8位),待从机应答后连续发送数据字节,每个字节均需从机应答,最后以停止信号结束传输8。读操作流程类似,但地址字节后跟随的是从机向主机的数据发送,主机通过发送NACK信号终止读取8。

时序逻辑:信号定义与速率分级

图1:I2C协议完整时序波形,标注了起始条件(S)、地址传输(ADDRESS)、读/写控制位(R/W)、应答位(ACK)、数据传输(DATA)及停止条件§。

I2C协议支持多种传输速率,最常用的包括标准模式(100kbps)和快速模式(400kbps),部分高级器件还支持3.4Mbps高速模式和5Mbps超快速模式45。不同模式的主要差异体现在时钟周期和信号建立/保持时间上:标准模式下SCL周期为10μs,而快速模式压缩至2.5μs,但需更严格的信号时序控制。

时序关键参数

起始信号:SCL高电平期间SDA从高→低跳变

停止信号:SCL高电平期间SDA从低→高跳变

数据采样:SCL上升沿前SDA需稳定至少250ns(标准模式)

应答窗口:第9个SCL周期内SDA需保持低电平(ACK)

应答机制如何保证数据完整性?每个字节传输后,接收方必须反馈ACK信号,这相当于实时的"数据包确认"。若传输过程中出现干扰导致数据错误,接收方可通过NACK通知主机重传,避免无效数据累积。这种逐字节校验机制使I2C在噪声环境下仍能保持较高的通信可靠性58。

综上所述,I2C协议通过物理层的开漏设计实现总线共享,协议层的地址与应答机制保障通信秩序,时序逻辑的严格定义确保数据准确传输,三者共同构成了该协议在嵌入式系统中广泛应用的技术基础。

STM32F103C8T6 IIC硬件配置

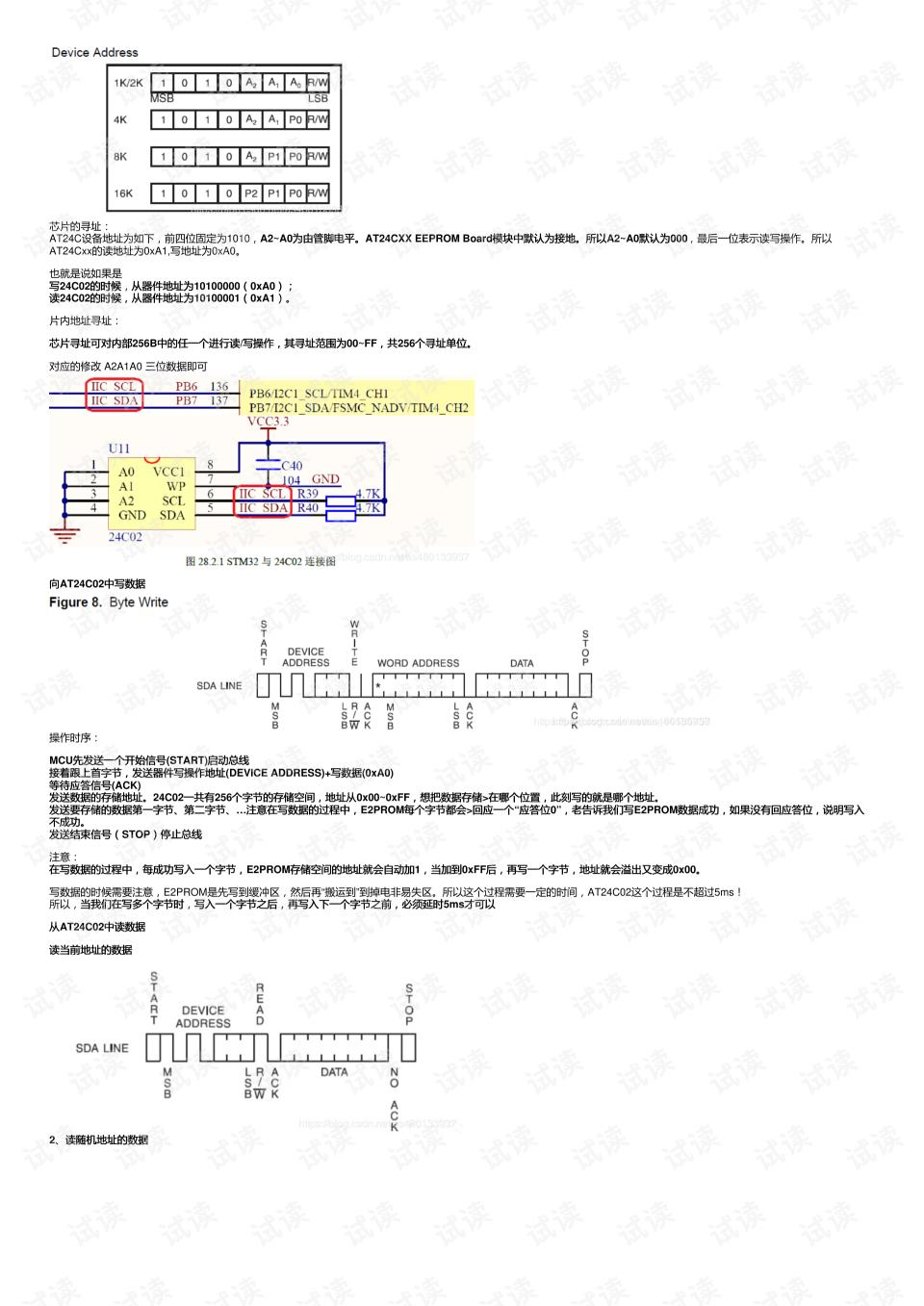

图4:AT24C02 EEPROM与STM32的I2C接线图,包含地址引脚(A0-A2接地)、WP引脚配置及上拉电阻参数。

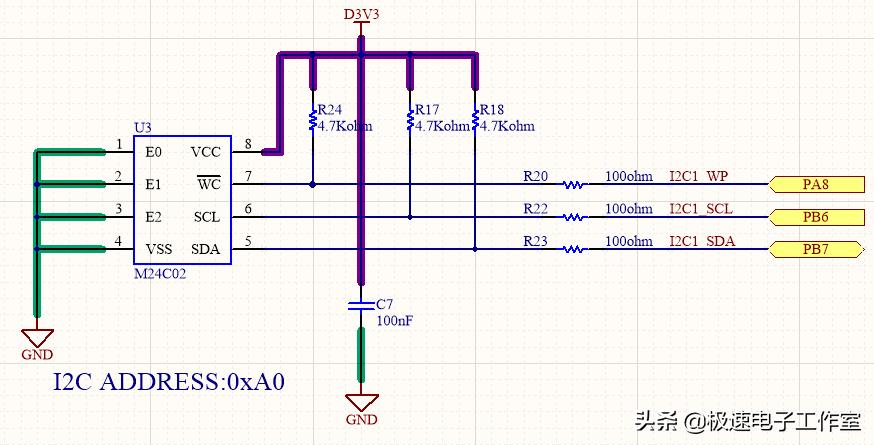

图2:STM32F103C8T6与I2C设备的硬件接线原理图,包含PB6(SCL)/PB7(SDA)引脚连接、4.7kΩ上拉电阻及100nF滤波电容。

STM32F103C8T6 微控制器集成两个独立的 I2C 接口(I2C1 和 I2C2),均挂载于 APB1 总线,支持标准模式(100 kHz)与快速模式(400 kHz)通信11。I2C1 默认引脚映射为 PB6(SCL)和 PB7(SDA),可通过引脚重映射功能切换至 PB8/PB9;I2C2 固定使用 PB10(SCL)和 PB11(SDA)714。典型硬件连接如 OLED 屏通信:STM32 的 I2C1_SCL(PB6)连接 OLED 的 SCL 引脚,I2C1_SDA(PB7)连接 OLED 的 SDA 引脚,同时需共地并确保电源电压匹配15。

外设时钟与 GPIO 配置

硬件 I2C 配置需完成两级时钟使能:首先通过 RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB, ENABLE) 开启 GPIOB 端口时钟,再通过 __HAL_RCC_I2C1_CLK_ENABLE() 激活 I2C1 外设时钟216。GPIO 引脚需配置为复用开漏模式(GPIO_MODE_AF_OD),速度设置为 50 MHz(标准库 GPIO_Speed_50MHz 或 HAL 库 GPIO_SPEED_FREQ_HIGH)2。以下为 HAL 库初始化示例代码:

void HAL_I2C_MspInit(I2C_HandleTypeDef* hi2c) {GPIO_InitTypeDef GPIO_InitStruct = {0};if(hi2c->Instance == I2C1) {__HAL_RCC_GPIOB_CLK_ENABLE(); // 使能 GPIOB 时钟__HAL_RCC_I2C1_CLK_ENABLE(); // 使能 I2C1 时钟// 配置 PB6(SCL) 和 PB7(SDA) 为复用开漏模式GPIO_InitStruct.Pin = GPIO_PIN_6 | GPIO_PIN_7;GPIO_InitStruct.Mode = GPIO_MODE_AF_OD; // 复用开漏输出GPIO_InitStruct.Pull = GPIO_PULLUP; // 启用内部上拉GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH; // 高速模式HAL_GPIO_Init(GPIOB, &GPIO_InitStruct);}

}

图2:STM32F103C8T6与I2C设备的硬件接线原理图,包含PB6(SCL)/PB7(SDA)引脚连接、4.7kΩ上拉电阻及100nF滤波电容。

总线硬件设计规范

I2C 总线物理层需满足以下关键约束:SDA 和 SCL 线必须外接 4.7 kΩ 上拉电阻至 VCC(3.3 V),该配置相较 10 kΩ 电阻能降低信号上升时间,支持更高通信速率37。总线长度建议不超过 1 米,过长会导致信号完整性下降,表现为边沿畸变和传输延迟17。电气参数方面,STM32F103C8T6 的 I2C 接口要求高电平输入电压 ≥ 0.7VDD(2.31 V),低电平输入电压 ≤ 0.3VDD(0.99 V),SCL 时钟频率最高可达 400 kHz1118。

关键设计要点:选择复用开漏模式而非推挽输出,是因为开漏结构允许多设备共享总线——当多个设备同时输出低电平时不会造成短路,而高电平状态由上拉电阻维持,这是 I2C 多主机仲裁机制的硬件基础1417。

I2C 外设核心由时钟生成器、数据寄存器和控制逻辑组成。其中 SCL 频率通过 APB1 时钟分频实现,计算公式为 fSCL = fAPB1 / (2×CCR),其中 CCR 为时钟控制寄存器的分频值11。硬件自动处理起始条件生成、地址识别和应答信号,通过状态寄存器 SR1/SR2 可监控通信状态,为软件配置提供实时硬件反馈1119。

STM32 IIC软件实现方法

STM32 实现 IIC 通信主要有硬件 IIC 和软件模拟两种方式,各具特点与适用场景。硬件 IIC 利用芯片集成的 I2C 外设自动生成时序,软件模拟则通过 GPIO 引脚手动模拟协议波形20。以下从实现原理、性能对比和高级特性展开详解。

硬件 IIC 实现

硬件 IIC 需完成 GPIO 复用配置、I2C 参数初始化和外设使能三大步骤。以 I2C1 初始化为例,标准库配置代码如下:

void I2C_Config(void) {GPIO_InitTypeDef GPIO_InitStruct;I2C_InitTypeDef I2C_InitStruct;/* 1. 使能时钟 */RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB, ENABLE); // GPIOB 时钟(SCL-PB6/SDA-PB7)RCC_APB1PeriphClockCmd(RCC_APB1Periph_I2C1, ENABLE); // I2C1 外设时钟/* 2. 配置 GPIO 为复用开漏模式 */GPIO_InitStruct.GPIO_Pin = GPIO_Pin_6 | GPIO_Pin_7;GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF_OD; // 复用开漏输出(支持线与逻辑)GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz; // 高速驱动GPIO_Init(GPIOB, &GPIO_InitStruct);/* 3. I2C 参数配置 */I2C_InitStruct.I2C_Mode = I2C_Mode_I2C; // 标准 I2C 模式I2C_InitStruct.I2C_DutyCycle = I2C_DutyCycle_2; // 时钟占空比 2:1(快速模式 400kHz 时有效)I2C_InitStruct.I2C_OwnAddress1 = 0x00; // 主机模式无需设置自身地址I2C_InitStruct.I2C_Ack = I2C_Ack_Enable; // 使能应答信号I2C_InitStruct.I2C_AcknowledgedAddress = I2C_AcknowledgedAddress_7bit; // 7 位地址模式I2C_InitStruct.I2C_ClockSpeed = 400000; // 通信速率 400kHz(快速模式)I2C_Init(I2C1, &I2C_InitStruct);/* 4. 使能 I2C 外设 */I2C_Cmd(I2C1, ENABLE);

}

主发送模式通过状态机流程实现数据传输:

关键寄存器配置包括:

软件模拟 IIC 实现

软件模拟通过 GPIO 直接控制 SCL/SDA 引脚电平,实现 IIC 时序。核心在于精确控制信号延时与状态切换,典型实现如下:

基础时序函数

// 起始信号:SCL 高电平时 SDA 由高变低

void IIC_Start(void) {SDA_OUT(); // SDA 配置为输出IIC_SDA = 1; // 初始高电平IIC_SCL = 1;Delay_Us(4); // 保持 4us 确保稳定IIC_SDA = 0; // SDA 下降沿产生起始信号Delay_Us(4);IIC_SCL = 0; // 拉低 SCL 准备数据传输

}// 发送字节:高位先行,每 bit 需 SCL 脉冲同步

void IIC_SendByte(uint8_t Byte) {uint8_t i;SDA_OUT();for(i = 0; i < 8; i++) {IIC_W_SDA(Byte & (0x80 >> i)); // 输出当前 bitIIC_W_SCL(1); // SCL 高电平锁存数据Delay_Us(2);IIC_W_SCL(0); // 拉低 SCL 准备下一位Delay_Us(2);}

}// 应答检测:释放 SDA 后等待从机拉低

uint8_t IIC_WaitAck(void) {uint8_t ucErrTime = 0;SDA_IN(); // SDA 切换为输入IIC_SDA = 1; Delay_Us(1);IIC_SCL = 1; Delay_Us(1);while(READ_SDA) { // 检测 SDA 是否被拉低ucErrTime++;if(ucErrTime > 250) { // 超时判定无应答IIC_Stop();return 1;}}IIC_SCL = 0; // 拉低 SCL 结束应答检测return 0;

}

性能对比

| 指标 | 硬件 IIC | 软件模拟 IIC |

|---|---|---|

| CPU 占用 | 低(外设自动处理时序) | 高(需 CPU 循环延时) |

| 时序精度 | 高(硬件保证规范兼容) | 依赖延时函数,易受中断影响 |

| 引脚灵活性 | 固定复用引脚(如 I2C1 为 PB6/PB7) | 任意 GPIO(开漏输出模式) |

| 最高速率 | 400kHz(快速模式) | 通常 ≤ 100kHz(受 CPU 限制) |

高级特性实现

中断与 DMA 优化

硬件 IIC 支持事件中断(EVENT)和错误中断(ERROR),可显著提升数据传输效率11。典型中断配置步骤:

void I2C1_EV_IRQHandler(void) {uint32_t event = I2C_GetLastEvent(I2C1);if(event == I2C_EVENT_MASTER_BYTE_TRANSMITTED) {// 发送下一字节或触发停止信号if(--TxCount > 0) {I2C_SendData(I2C1, *TxBuffer++);} else {I2C_GenerateSTOP(I2C1, ENABLE);}}}

DMA 配置用于批量数据传输,步骤包括:

选型建议

工程选型指南

高速/多设备场景:优先硬件 IIC,如传感器阵列数据采集(需 400kHz 速率);

引脚资源紧张场景:选择软件模拟,如复用普通 GPIO 实现多总线隔离;

低功耗场景:硬件 IIC 配合 DMA 可降低 CPU 唤醒频率,延长续航。

实际应用中,硬件 IIC 适合对可靠性和效率要求高的场景(如工业传感器),软件模拟则在引脚复用受限或原型验证阶段更具灵活性20。两种方式均需严格遵循 IIC 时序规范,确保从机设备兼容(如起始信号建立时间 ≥ 4.7us,SCL 低电平宽度 ≥ 4.7us)。

IIC通信典型应用案例

OLED显示屏(SSD1306)通信实现

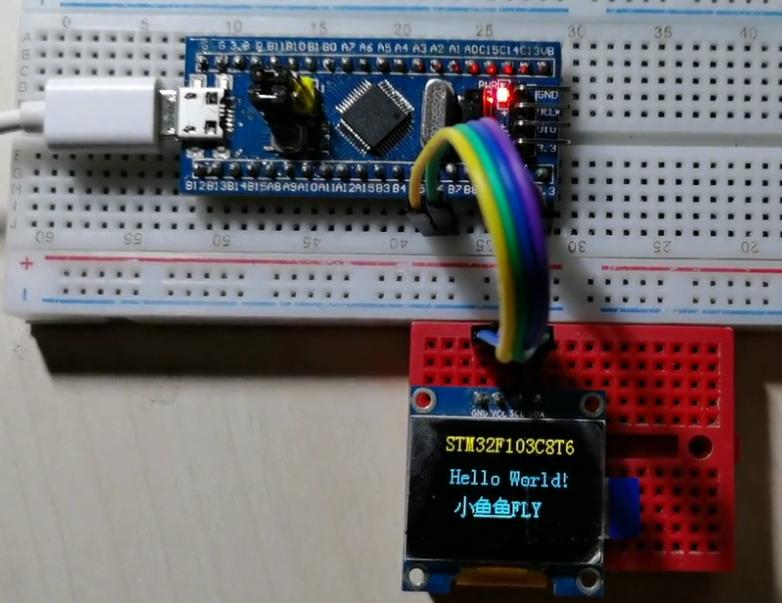

图3:STM32开发板与OLED模块的面包板连接实物,显示屏显示"STM32F103C8T6 Hello World!"测试信息。

硬件接线设计

STM32F103C8T6与SSD1306 OLED显示屏的IIC通信采用硬件I2C1接口,具体接线如下:

图3:STM32开发板与OLED模块的面包板连接实物,显示屏显示"STM32F103C8T6 Hello World!"测试信息。

协议解析与代码实现

SSD1306的7位设备地址为0x3C,在实际通信中需左移1位并添加读写位,形成0x78(写操作)和0x79(读操作)。通信过程中通过控制字节区分命令(0x00)和数据(0x40)传输,以下是基于HAL库的核心实现代码:

// OLED初始化函数

void SSD1306_Init(void) {HAL_Delay(100); // 上电延时SSD1306_WriteCommand(0xAE); // 关闭显示SSD1306_WriteCommand(0x20); // 设置内存寻址模式SSD1306_WriteCommand(0x00); // 水平寻址模式// ... 其他初始化命令省略SSD1306_WriteCommand(0xAF); // 开启显示

}// 字符显示函数

void SSD1306_Puts(uint8_t x, uint8_t y, char *str) {while(*str) {SSD1306_WriteData(Font8x16[(*str-' ')<<4]); // 高字节SSD1306_WriteData(Font8x16[((*str-' ')<<4)+1]); // 低字节x += 8;str++;}

}// 命令写入实现

void SSD1306_WriteCommand(uint8_t cmd) {uint8_t data[2] = {0x00, cmd}; // 控制字节+命令HAL_I2C_Master_Transmit(&hi2c1, 0x78, data, 2, HAL_MAX_DELAY);

}// 数据写入实现

void SSD1306_WriteData(uint8_t data) {uint8_t buf[2] = {0x40, data}; // 控制字节+数据HAL_I2C_Master_Transmit(&hi2c1, 0x78, buf, 2, HAL_MAX_DELAY);

}

关键技术点解析

EEPROM(AT24C02)存储应用

硬件连接与存储特性

AT24C02是2K位串行EEPROM,包含256个8位字节,支持16字节页写入操作。硬件连接采用I2C1接口:

图4:AT24C02 EEPROM与STM32的I2C接线图,包含地址引脚(A0-A2接地)、WP引脚配置及上拉电阻参数。

页写入与随机读取实现

AT24C02的页写入存在16字节边界限制,跨页写入需进行地址判断和分块处理。以下是完整的读写实现代码:

// 跨页写入函数

uint8_t EEPROM_Write(uint16_t addr, uint8_t *data, uint16_t len) {uint8_t bytesWritten = 0;while(len > 0) {uint8_t pageRemain = 16 - (addr % 16); // 计算页内剩余空间uint8_t writeLen = (len < pageRemain) ? len : pageRemain;// 发送设备地址+写命令+内存地址uint8_t txData[17];txData[0] = (uint8_t)addr; // 内存地址低8位memcpy(&txData[1], data + bytesWritten, writeLen);if(HAL_I2C_Master_Transmit(&hi2c1, 0xA0, txData, writeLen + 1, 100) != HAL_OK) {return bytesWritten; // 写入失败返回已写字节数}HAL_Delay(5); // 等待写入完成(EEPROM内部时序要求)addr += writeLen;bytesWritten += writeLen;len -= writeLen;}return bytesWritten;

}// 随机读取函数

uint8_t EEPROM_Read(uint16_t addr, uint8_t *data, uint16_t len) {// 先写入读取地址uint8_t txAddr = (uint8_t)addr;if(HAL_I2C_Master_Transmit(&hi2c1, 0xA0, &txAddr, 1, 100) != HAL_OK) {return 0; // 地址发送失败}// 读取数据if(HAL_I2C_Master_Receive(&hi2c1, 0xA1, data, len, 100) != HAL_OK) {return 0; // 数据接收失败}return len;

}

主函数验证流程

int main(void) {HAL_Init();SystemClock_Config();MX_GPIO_Init();MX_I2C1_Init();MX_USART1_UART_Init();uint8_t testData = 0x55;uint8_t readData;// 写入数据EEPROM_Write(0x0001, &testData, 1);HAL_Delay(10);// 读取数据EEPROM_Read(0x0001, &readData, 1);// 串口验证char msg[50];sprintf(msg, "Write: 0x%02X, Read: 0x%02X\r\n", testData, readData);HAL_UART_Transmit(&huart1, (uint8_t*)msg, strlen(msg), HAL_MAX_DELAY);while(1);

}

关键协议要点:

EEPROM的IIC通信严格遵循"起始信号-设备地址-内存地址-数据-停止信号"的时序

页写入操作需注意16字节边界,地址计算方式为addr % 16

每次写入后必须等待EEPROM内部擦写周期(通常5ms),对应IIC协议中的从机应答等待机制3

实物连接与效果验证

通过示波器可观察到完整的IIC通信波形,其中:

串口调试助手将显示"Write: 0x55, Read: 0x55",验证数据读写一致性。实际应用中需添加错误处理机制,如检测HAL库返回值判断通信状态。

IIC通信错误处理与调试

STM32F103 的 I2C 外设提供三类核心错误检测机制:ACK 故障(AF) 发生在从机未应答地址或数据时,可通过 I2C_SR1_AF 位检测,常见原因包括从机地址错误、总线线路故障或从机未就绪 1122;仲裁丢失(ARLO) 多主机竞争时,若检测到自身发送电平与总线实际电平不一致,硬件会自动将设备切换为从机模式 11;总线错误(BERR) 由非法起始/停止条件触发,需通过软件复位总线恢复 11。

错误处理流程遵循 “检测标志位→判断类型→执行恢复” 逻辑:主机发送数据后需检查状态寄存器,若发现 AF 标志可执行地址重试(如遍历 0x00 - 0xFF 地址扫描排查设备地址错误),BERR 错误需调用 I2C_DeInit() 后重新初始化外设,ARLO 事件则需等待总线空闲后重新发起传输 1122。HAL 库环境下可通过检查 HAL_I2C_Master_Transmit() 等函数返回值实现错误捕获,并在 HAL_I2C_ErrorCallback() 中执行恢复操作 2324。

实战调试案例:OLED 无显示故障排查

检测状态寄存器发现 AF 标志置位

使用地址扫描工具发送 0x78 与 0x7A 地址(OLED 常见地址)

发现 0x7A 无应答而 0x78 有应答,确认地址配置错误

修改设备地址后通信恢复正常

调试工具方面,示波器可观测 SCL/SDA 波形与理想时序对比,重点检查信号上升沿是否因上拉电阻缺失导致过缓;软件层面推荐实现 超时检测机制 防止总线死锁,并建立重试策略(如最多 3 次重试)提升可靠性 1122。

常见物理层问题包括虚焊导致的接触不良、未接 4.7 kΩ 上拉电阻、主从设备共地不良等,可通过接线排查表系统定位 1115。

// HAL 库 NACK 错误处理示例代码

if (HAL_I2C_Master_Transmit(&hi2c1, DevAddress, pData, Size, Timeout) != HAL_OK) {if (hi2c1.ErrorCode & HAL_I2C_ERROR_AF) {HAL_I2C_DeInit(&hi2c1); // 软件复位MX_I2C1_Init(); // 重新初始化retries++; // 重试计数}

}