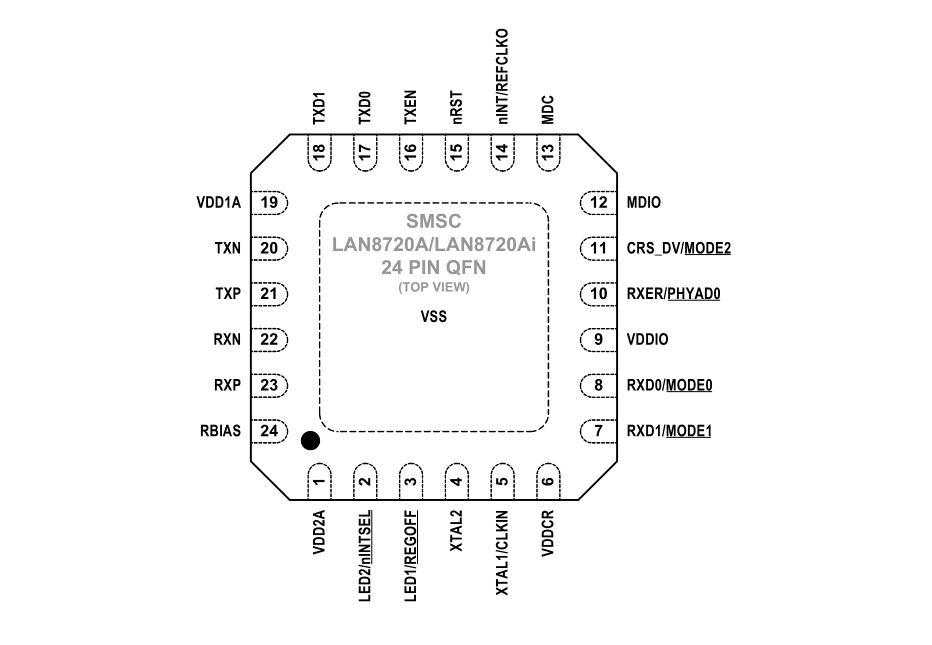

LWIP通讯之PHY芯片LAN8720引脚详解

LAN8720A和LAN8720Ai的区别是工作温度不同,前者是商业级后者是工业级,LAN8720支持的接口是RMII

关于参考文档(英文)可去我的资源中取,无积分

| 引脚编号 | 引脚名称 | 引脚作用 |

| 1 | VDD2A | 3.3V电源通道2,内部稳压器电源 |

| 2 | LED2/nINTSET | 链路速度指示灯,100Mbps时有效,10Mbps或链路隔离时无效/选择14号引脚的工作模式,悬空或上拉直VDD2A时:nINT模式,下拉至VSS时REFCLKO模式(注意外部的上拉下拉电阻会影响LED2的有效电平) |

| 3 | LED1/REGOFF | 有效链路指示灯,拉高时接到VDD2A而不是VDDIO/用于禁用内部1.2V稳压器,当禁用时需要给VDDCR输入1.2V电压,浮空或拉低时启用稳压器,拉高到VDD2A时禁用稳压器 |

| 4 | XTAL2 | 外部晶振输入端2(25MHz) |

| 5 | XTAL1/CLKIN | 外部晶振输入端1(25MHz)/单端时钟输入50Mhz(此时XTAL2应该无晶振连接) |

| 6 | VDDCR | 1.2V输入,使用内部稳压器时,接1uf去耦电容接地 |

| 7 | RXD1/MODE1 | 数据接收信号线第1位/PHY模式配置位1(硬复位时值会被锁存到寄存器,之后就是RXD的功能) |

| 8 | RXD0/MODE0 | 同上 |

| 9 | VDDIO | 1.6~3.6V可变IO电源 |

| 10 | RXER/PHYAD0 | 帧错误状态引脚/PHY地址设置,默认下拉(硬复位时)可以通过通讯修改成0,1之外的PHY地址 |

| 11 | CRS_DV/MODE2 | 载波侦听引脚(有无数据传输)/PHY模式配置位2 |

| 12 | MDIO | 串行管理接口(用于MAC配置PHY芯片寄存器用) |

| 13 | MDC | 串行管理接口时钟 |

| 14 | nINT/REFCLKO | 低电平有效中断输出/50Mhz时钟输出引脚(不是RMII规范的一部分,所以要核对时序) |

| 15 | nRST | 硬件复位,低电平复位 |

| 16 | TXEN | 发送使能 |

| 17 | TXD0 | RMII发送数据位0 |

| 18 | TXD1 | RMII发送数据位1 |

| 19 | VDD1A | 电源通道1 |

| 20 | TXN | 收发负极1(连接RJ45等接口) |

| 21 | TXP | 收发正极1 |

| 22 | RXN | 收发负极2 |

| 23 | RXP | 收发正极2 |

| 24 | RBIAS | 此引脚需要接一个12.1KΩ(1%)的电阻到地 |

模式配置列表

| 值 | 速度 | 工作模式 | 自动协商 | 说明 |

| 000 | 10Mbps | 半双工 | 禁用 | |

| 001 | 10Mbps | 全双工 | 禁用 | |

| 010 | 100Mbps | 半双工 | 禁用 | 收发时CRS激活 |

| 011 | 100Mbps | 全双工 | 禁用 | 接收时CRS激活 |

| 100 | 100Mbps | 半双工 | 启用 | 收发时CRS激活 |

| 101 | 100Mbps | 半双工 | 启用 | 接收时CRS激活 中继模式 |

| 110 | X | X | X | 低功耗模式,要退出则修改寄存器并软复位 |

| 111 | X | X | 启用 | 所有功能 |

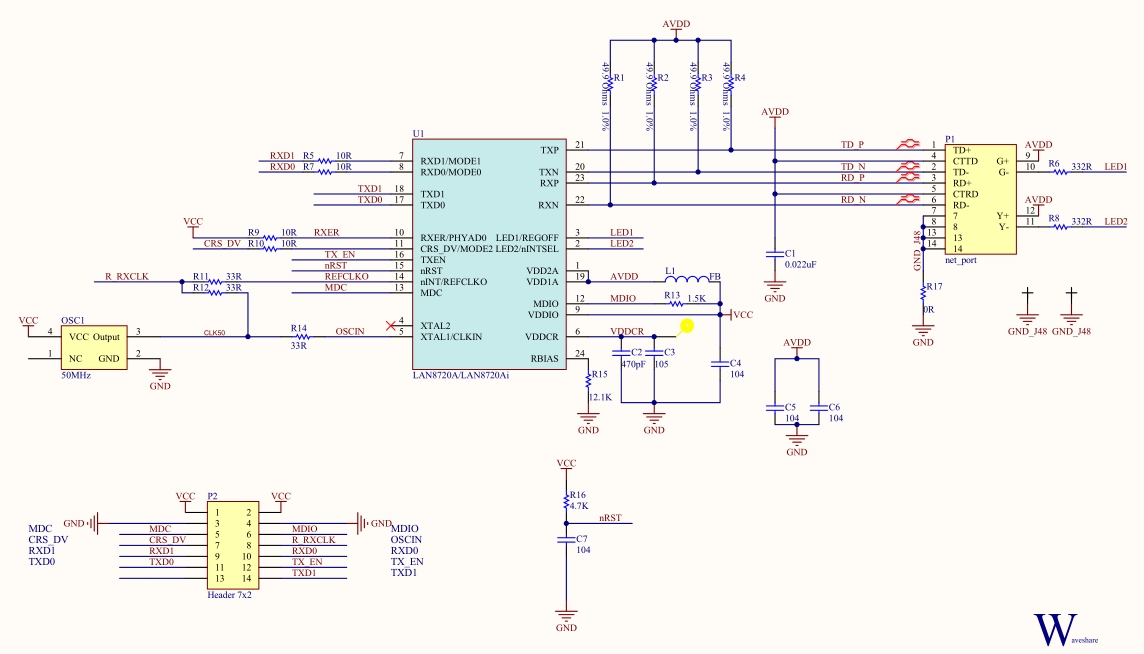

典型的原理图