FPGA内实现FIR 抽取滤波器设计

- FIR 抽取滤波器设计与分析

- Fir 抽取思路

- 为什么要进行抽取操作

- Fir 抽取思路

AD9467芯片当前的采样率为250Msps,输出数据位宽为16bit,如果直接使用250Msps进行采样,每秒产生的数据量为:250Msps * 2 Bytes = 500 MB/s。如此高的数据速率对后续处理环节是巨大的负担:

- FPGA内部存储:想要缓存1秒的数据需要500MB的BRAM,这是绝大多数FPGA无法提供的。

- 外部传输:通过千兆以太网(理论极限125MB/s)或PCIe接口传输500MB/s的数据非常困难,需要非常强力的硬件。

- 存储与处理:将这些原始数据实时存储到PC硬盘并进行处理,需要极高的PC配置

另外我们当前的输入信号要求仅为1.5M-30M,根据奈奎斯特采样定理,要无失真地恢复一个最高频率为 F_max 的信号,采样率 Fs 只需满足 Fs > 2 * F_max。当前信号最高频率为30MHz,因此理论上只需 Fs > 60Msps 即可完整保留所有信息。250Msps的采样率远高于所需的最低要求。超出的采样率(250MHz - 60MHz = 190MHz)并没有带来新的信息,反而产生了巨大的数据冗余。

抽取的目的就是消除这种冗余。降低后续处理难度:将数据率从500MB/s降低到约166.67MB/s(D=3后),对FPGA的逻辑时序、存储资源、以及对外传输接口的要求都大幅降低。

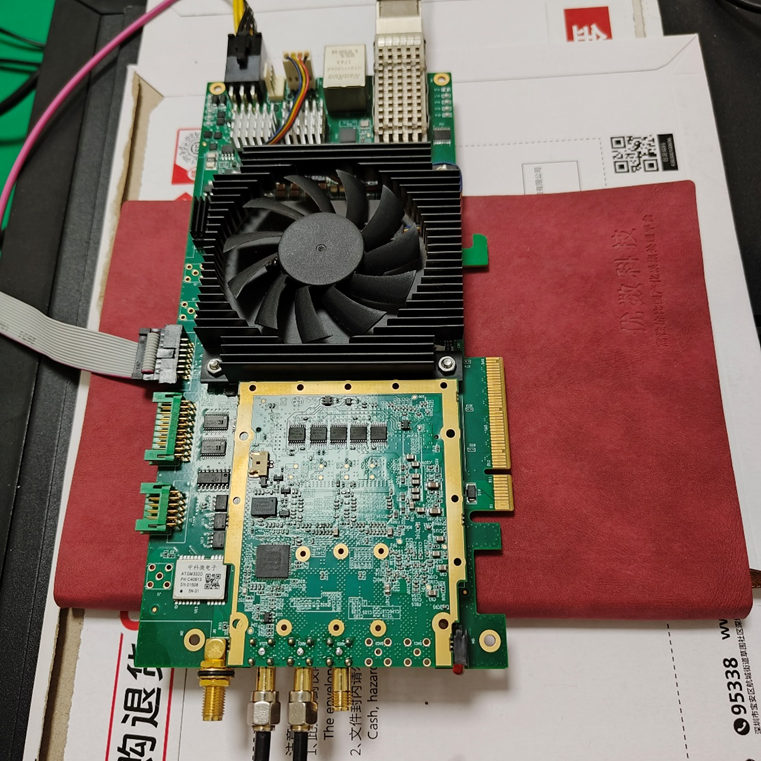

2.使用的硬件平台

本文试验是基于FMC-707采集卡和PCIe-404信号处理卡上进行。

UD FMC-707双通道接收+双通道发射FMC模块满足VITA57.1单宽、导冷规范。

模块ADC支持进口AD9467-250或国产GMS008、 SAD9467采集芯片, DAC支持

AD9171/AD9172/AD9173/AD9174/AD9175/AD9176回放芯片,输入和输出

均为交流耦合方式。 FMC子卡还支持外参考/外时钟、外触发接口等功能。模块

采用高质量的时钟和电源,具有优异的性能指标。 全部器件选用工业级和以上质量等级的元器件。

UD PCIe-404全国产化信号处理模块为标准PCIe全高的结构,对外支持PCIe3.0×8通信,也可以采用千兆以太网(RJ45连接器)、万兆以太网(或RapidIO、Aurora,QSFP+连接器)接口进行通信,支持多板级联,模块为100%国产化设计(同时也兼容进口器件)。FPGA芯片可选上海复旦微或深圳国微公司的V7-690T,两组DDR3的存储容量分别可配置为2~4GByte。板载有1个FMC+(兼容FMC子板)全互联的接口,满足VITA57.1和VITA57.4规范,可以适配大多数ADC/DAC FMC或FMC+子卡。全部器件选择工业级和以上质量等级元器件。

- 抽取操作的方案分析

抽取的核心目的是在降低数据率的同时,保证信号信息不丢失。抽取过程分为两步:

- 抗混叠滤波 (Anti-aliasing Filtering):用一个低通滤波器(LPF)滤除抽取后新采样率下会导致混叠的高频分量。

- 降采样 (Downsampling):每隔 D-1 个点保留一个点,将采样率从 Fs 降低到 Fs/D 。

最关键的原则是:抗混叠滤波器的截止频率必须小于或等于新的奈奎斯特频率,即 Fcutoff 。

- 抽取方案 : Decimate = 3

- 新采样率 Fs_new : 250 / 3 ≈ 83.33 Msps

- 新奈奎斯特频率 Fn_new : 83.33 / 2 ≈ 41.67 MHz

新的奈奎斯特频率(41.67MHz)远大于30MHz。这意味着抗混叠滤波器拥有一个非常宽的过渡带: 41.67 - 30 = 11.67MHz 。过渡带很宽,可以用一个抽头数较少的低阶FIR滤波器轻松实现,节省大量FPGA资源,时序更容易满足。

- Matlab抽取系数设置

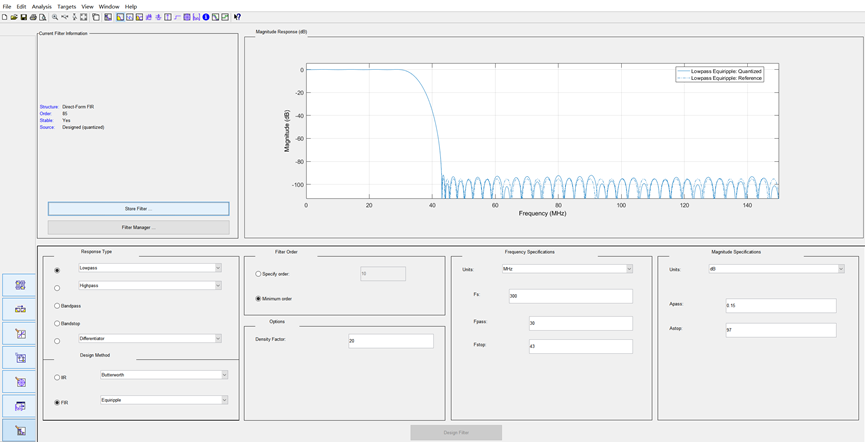

- 使用Fdatool进行抽取滤波器实际

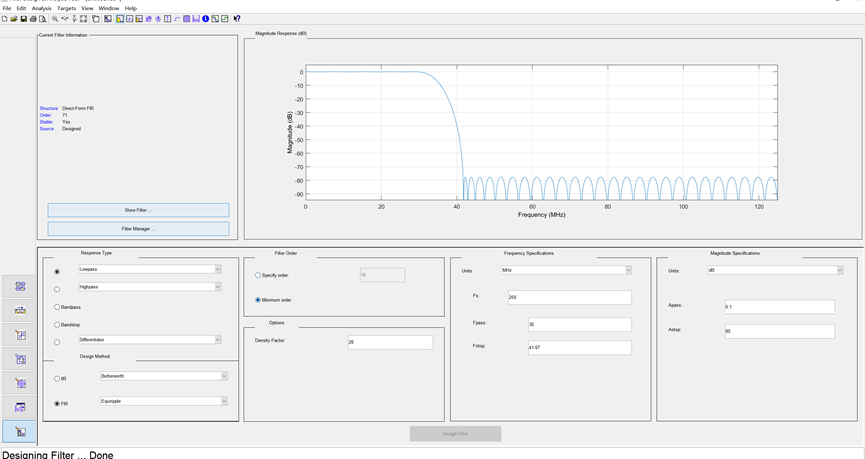

- 设计方案1

- 使用Fdatool进行抽取滤波器实际

- Matlab抽取系数设置

- 采样率 (Fs): 250 MHz - 与您的ADC采样率匹配

- 抽取因子 (D): 3 - 将采样率降低到83.33 MHz

- 通带截止频率 (Fpass): 30 MHz - 保留您的信号带宽(1.5M-30M)

- 阻带起始频率 (Fstop): 41.67 MHz - 这是新的奈奎斯特频率(250/3/2)

- 通带纹波 (Ap): 0.1 dB - 通带内信号幅度变化很小

- 阻带衰减 (Ast): 80 dB - 提供足够的阻带抑制

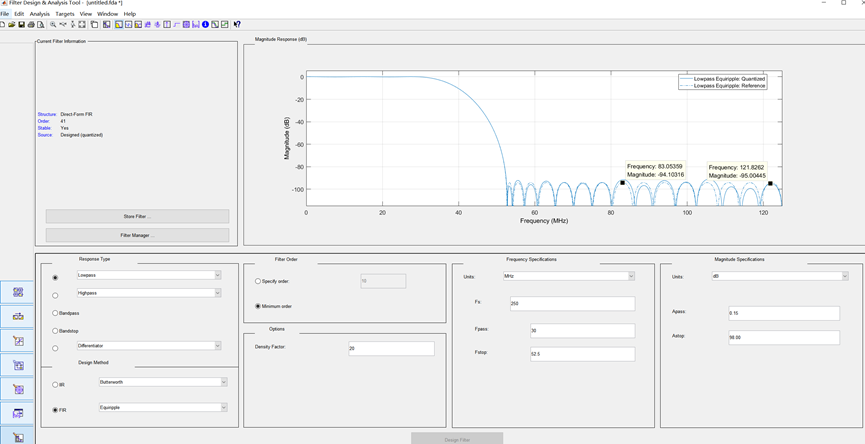

- 设计方案2

当前使用此方案

FPASS为 带通截止频率

FSTOP为阻带截止频率 计算公式:

Fstop =(250M / 3) / 2 + [ (250M / 3) / 2 – 30M ]

= 83.33M / 2 + [ 11.66667M]

= 41.66667M + 11.666667M

= 53.33333M

其中(250M / 3) 为输出采样率 ; (250M / 3) / 2为奈奎斯特带宽;

[ (250M / 3) / 2 – 30M ] 为镜像频率带宽

(250M / 3) / 2 + [ (250M / 3) / 2 – 30M ] 为实际阻带截止频率,必须小于此值,否则会引入镜像杂散。

- 导出系数与性能分析

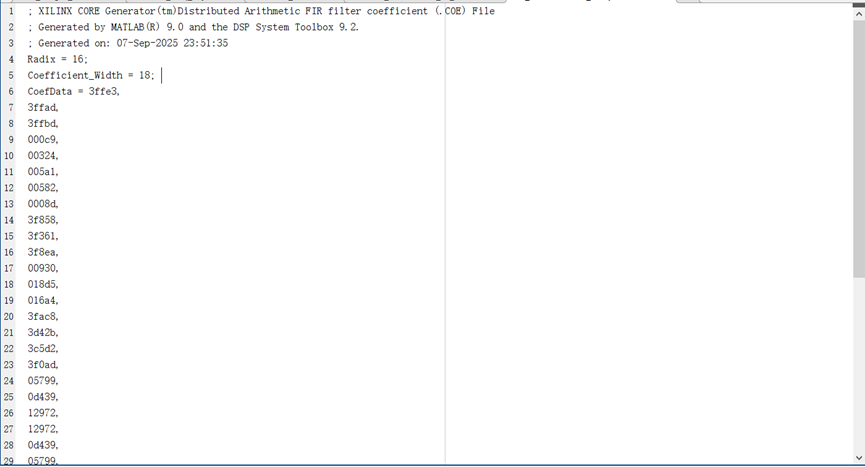

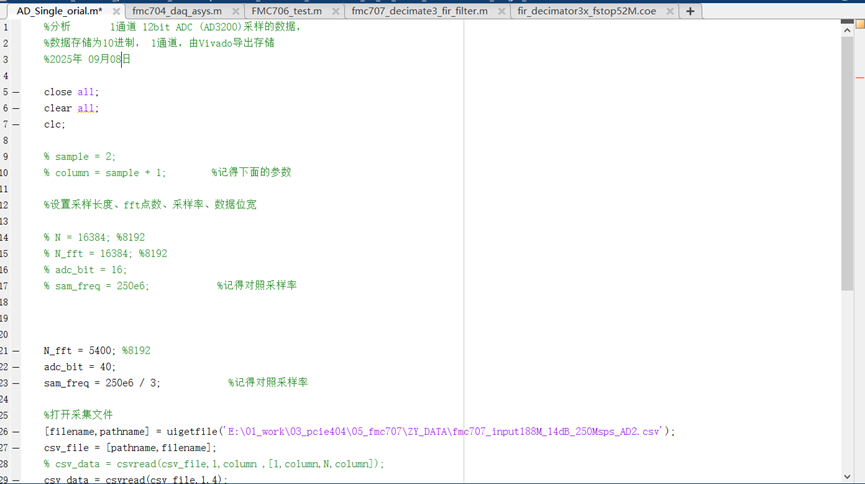

load 'cofficient_Fstop52M.mat';

N_bit = 18;

% 系数量化为16位有符号整数

max_coeff = max(abs(coefficient_Fstop52M));

coeffs_quantized = round(coefficient_Fstop52M / max_coeff * (2^(N_bit-1) - 1));

% 写入 COE 文件

fid = fopen('fir_decimator_D3.coe', 'w');

fprintf(fid, 'radix=10;\n');

fprintf(fid, 'coefdata=\n');

% 写入系数(每行一个)

for i = 1:length(coeffs_quantized)-1

fprintf(fid, '%d,\n', coeffs_quantized(i));

end

% 最后一个系数后加分号

fprintf(fid, '%d;', coeffs_quantized(end));

fclose(fid);

disp('COE文件已生成: fir_decimator_D3.coe');

disp(['系数数量: ', num2str(length(coeffs_quantized))]);

% 验证量化后滤波器性能

freqz(coeffs_quantized, 1, 1024, 250e6);

title('量化后滤波器频率响应 (D=3 抗混叠滤波器)');

grid on;

line([0 30], [0 0], 'Color', 'g', 'LineStyle', '--'); % 通带

line([41.67 125], [-80 -80], 'Color', 'r', 'LineStyle', '--'); % 阻带

legend('频率响应', '通带(0-30MHz)', '阻带衰减(>41.67MHz)');

- 生成的coe文件格式

- FPGA Fir抽取

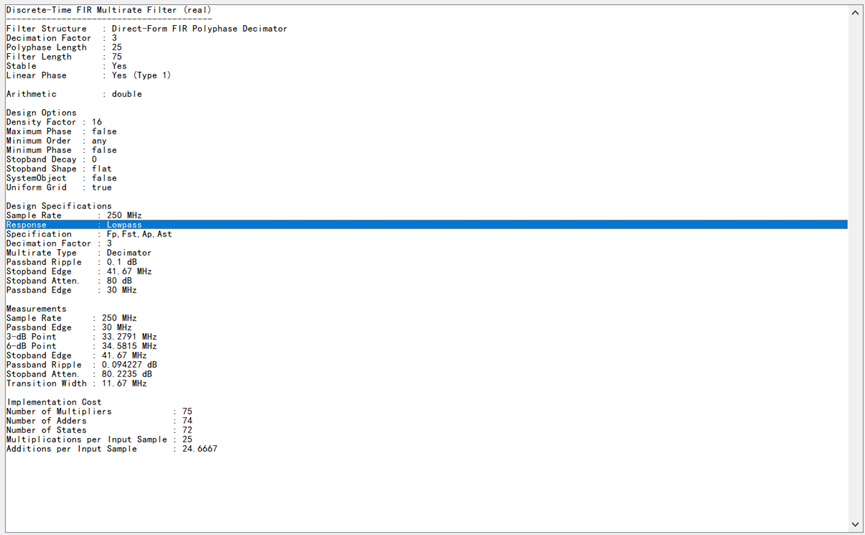

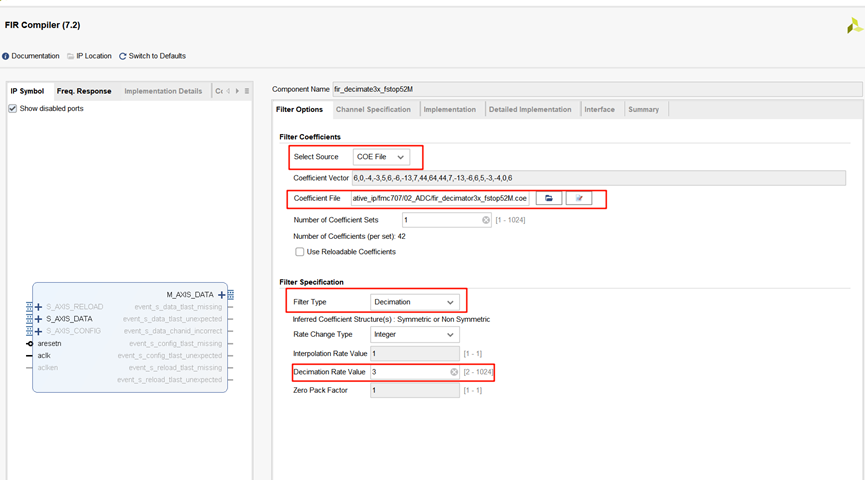

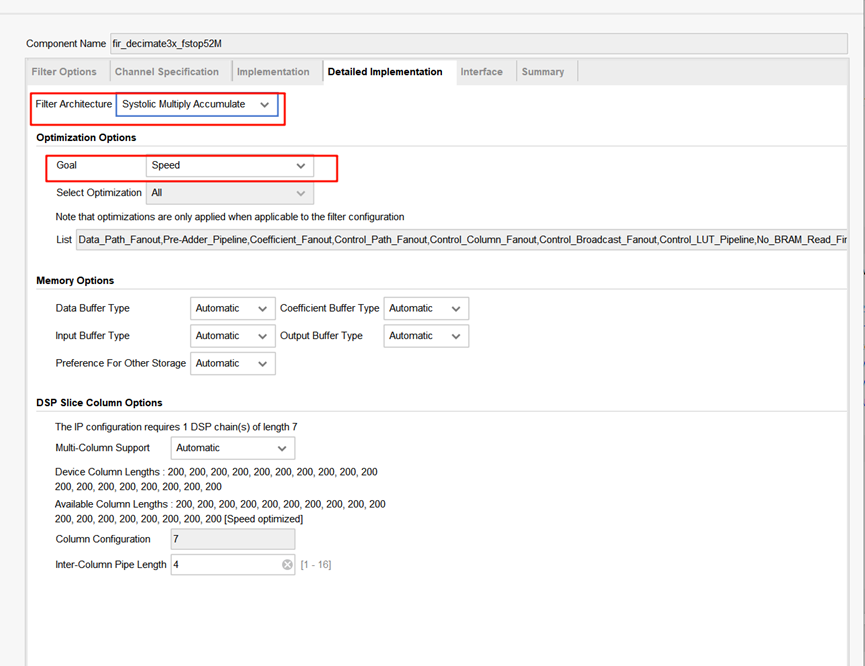

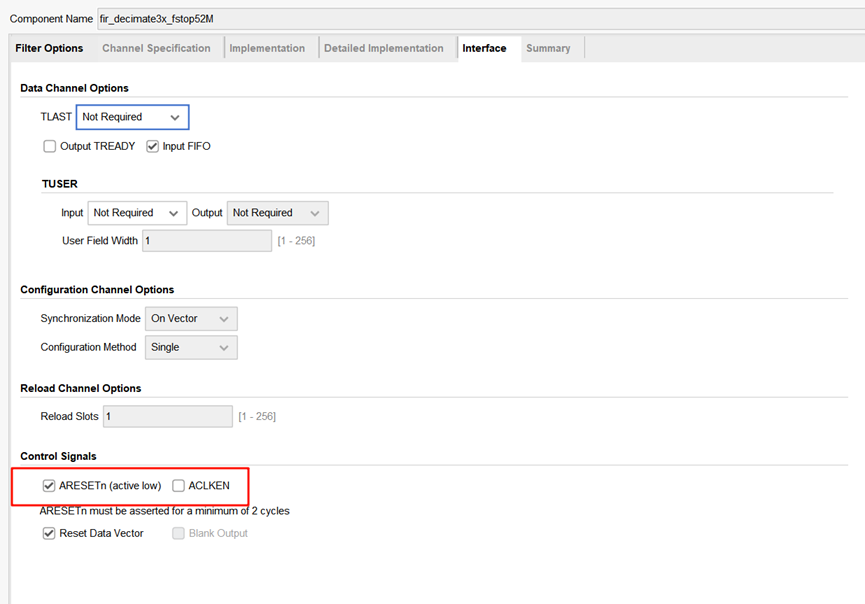

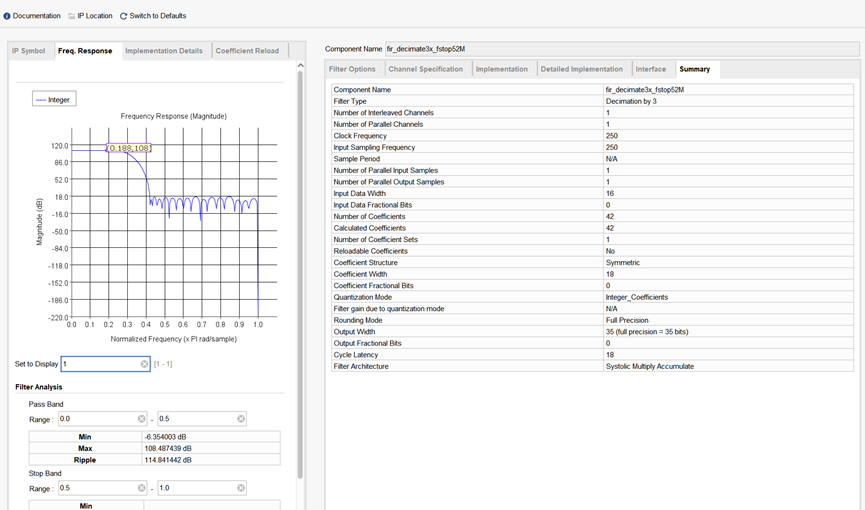

- IP核配置

- Coefficient Options → Coefficient Source: 选择 Vector

- Filter Type: 选择 Multirate Filtering (Decimation)

- Decimation Options → Decimation Factor: 设置为 3

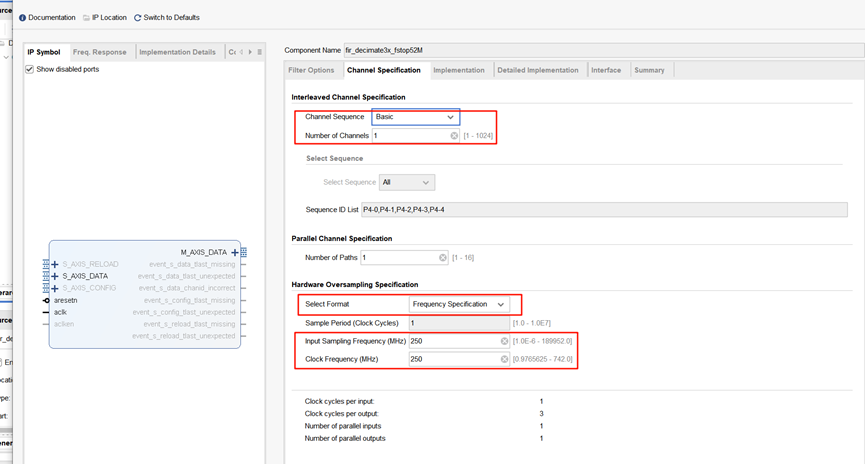

- Input Sampling Frequency (MHz): 输入 250

- Clock Frequency : 250MHz

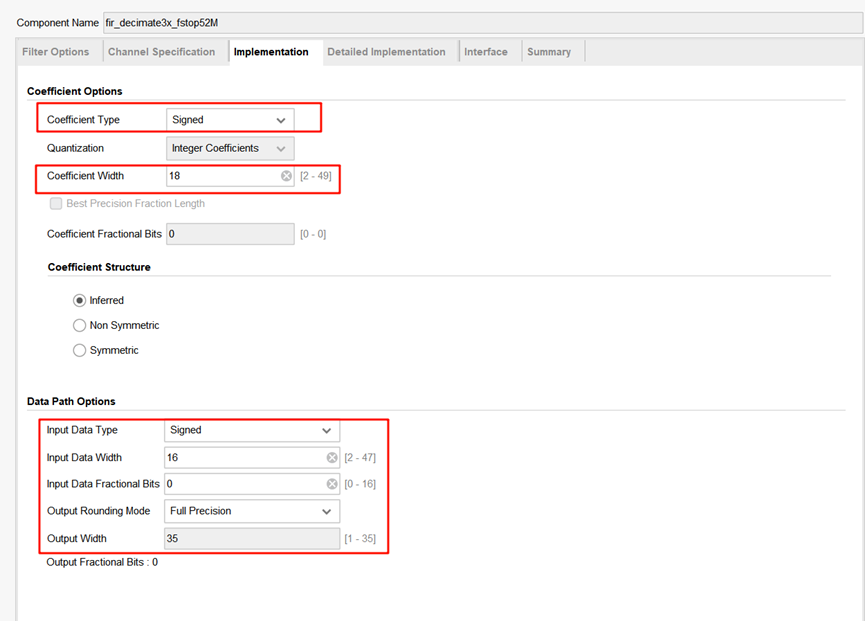

- Coefficient Sign: 选择 Signed

- Coefficient Width: 设置为 18(与量化系数匹配)

- Coefficient Fractional Bits: 设置为 0(使用的是整数系数)

- Data Type: 选择 Signed

- Input Data Width: 设置为 16(与ADC 数据宽度匹配)

- Output Rounding Mode: 选择 Full Precision

- 或者想控制输出位宽,可以选择 Truncate LSBs 并设置所需的输出宽度

在配置界面的右侧,Vivado 会实时显示资源使用估算:

- 检查 DSP48E1/2 使用量是否在 FPGA 资源范围内

- 检查 LUT 和 FF 使用量

如果资源使用过高,您可以:

- 回到 MATLAB 重新设计滤波器,减少抽头数

- 在 Implementation 选项卡中选择更节省资源的架构

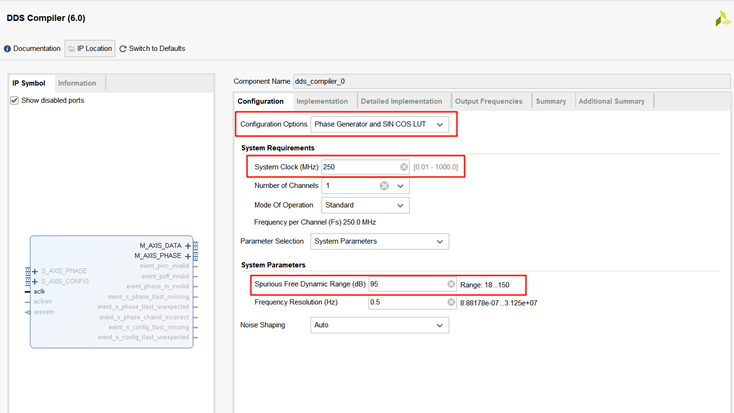

- 添加DDS-IP进行功能验证

使用vivado的DDS IP核生成一个25Mhz ,250Msps的正弦波,设置SFDR为95dBFS。

相位增量(Phase Increment)是DDS的核心参数,决定了输出信号的频率。其计算公式为:

其中:

- f_out = 25 MHz(期望输出频率)

- f_clk = 250 MHz(系统时钟频率)

- N = 相位累加器位宽(如32位)

十六进制表示约为 0x1999_999A 。

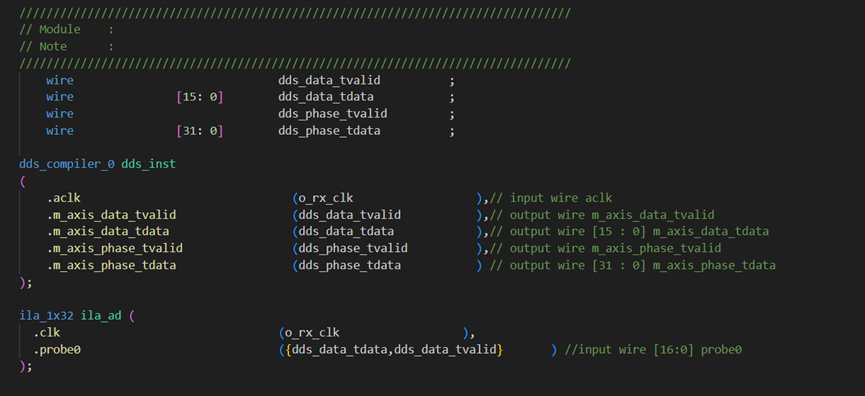

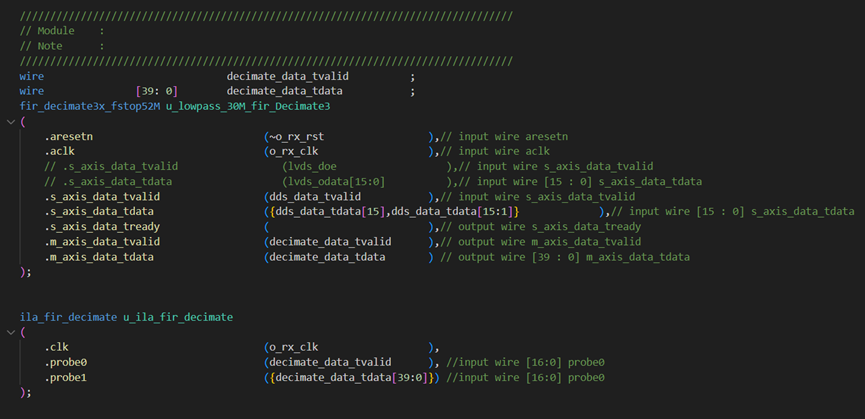

- FPGA工程例化

- 数据抓取

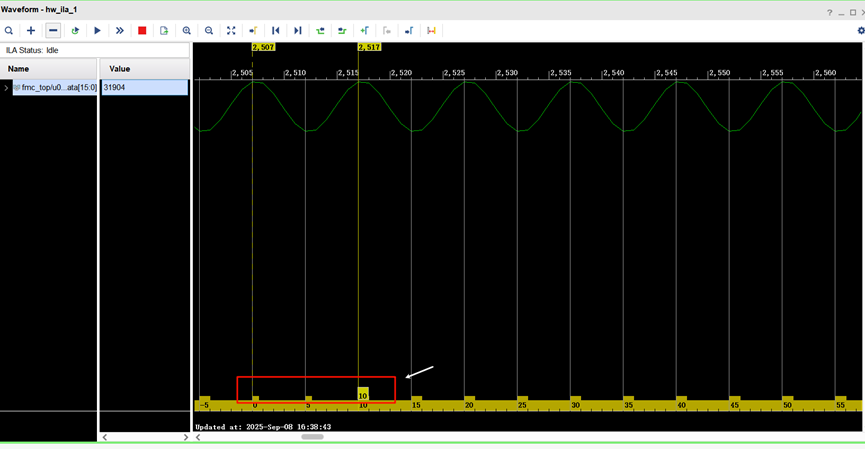

- DDS-IP生成的25M数据,采样率为250M

- 数据抓取

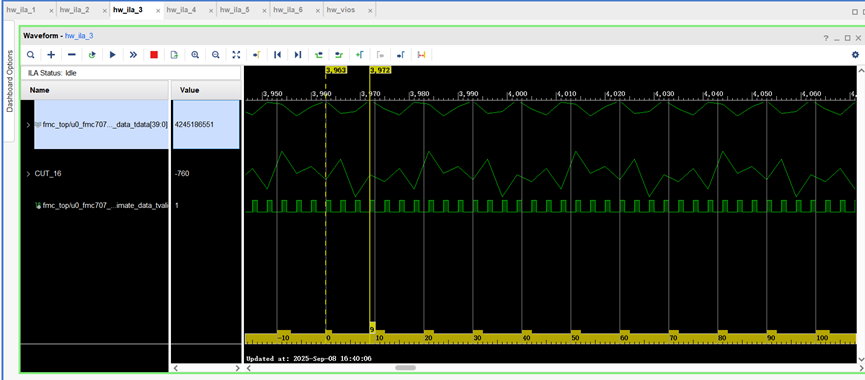

- 经过3倍抽取后的数据

- 数据分析

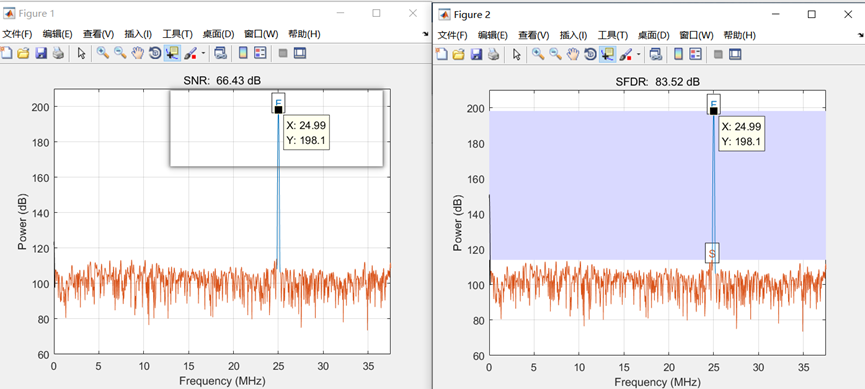

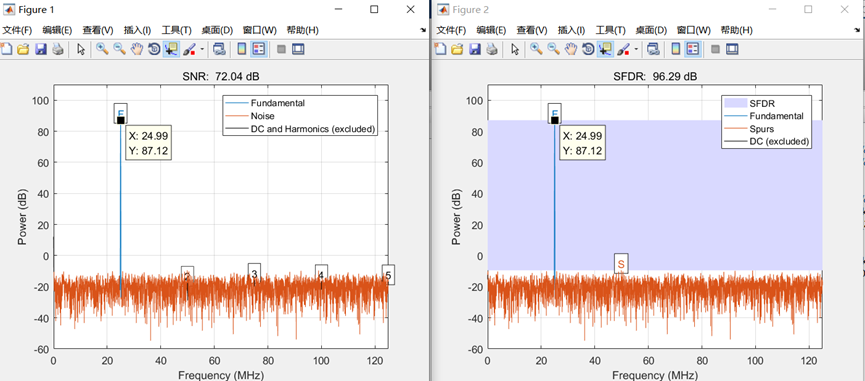

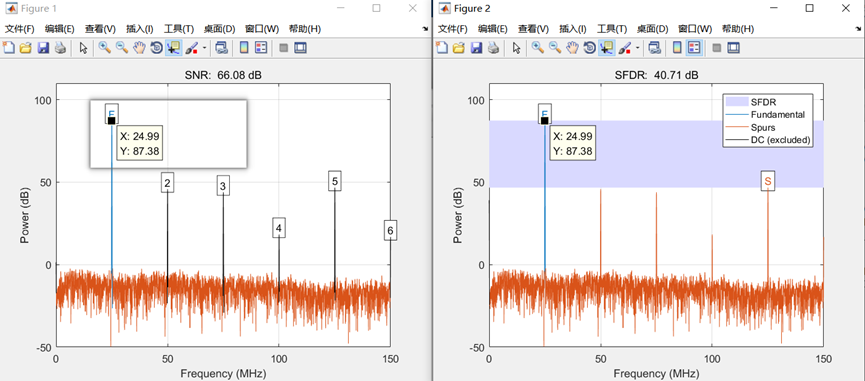

- DDS的频谱与性能

- Fir-3倍抽取后的频谱与性能

- 上板验证

- 测试环境

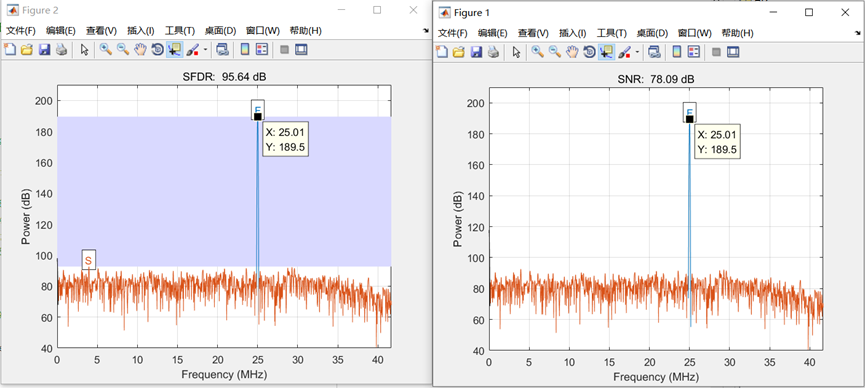

- 上板实测结果

- 参数配置

- 上板实测结果

- 输入信号300Msps直采

- Fir-4倍抽取采集