【硬件-笔试面试题-84】硬件/电子工程师,笔试面试题(知识点:MOS管是损耗有哪些)

题目汇总版--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客

【硬件-笔试面试题-84】硬件/电子工程师,笔试面试题(知识点:MOS管的损耗有哪些)

1、题目

MOS管的损耗有哪些

2、知识点

MOS 管在开关电源(如 DC-DC 转换器)等应用中,其损耗主要来自导通和开关过程中的能量消耗,具体可分为以下几类:

1. 导通损耗(Conduction Loss)

当 MOS 管处于导通状态时,电流通过其导通电阻(\(R_{DS(on)}\))产生的功率损耗。 计算公式:\(P_{cond} = I_{DS}^2 \times R_{DS(on)}\)

- 关键影响因素:

- 导通电阻\(R_{DS(on)}\):与 MOS 管的尺寸、栅极电压(\(V_{GS}\))、温度相关(温度升高,\(R_{DS(on)}\)增大)。

- 导通时的漏极电流\(I_{DS}\):与负载电流直接相关,电流越大,损耗越高。

2. 开关损耗(Switching Loss)

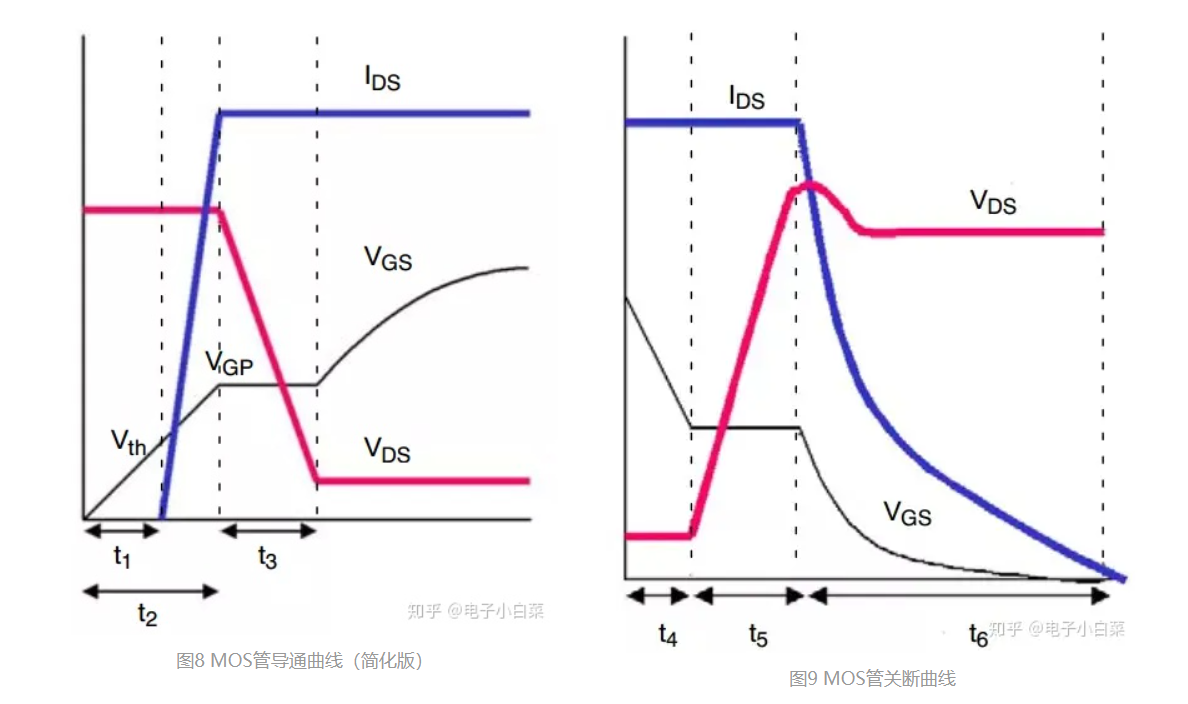

MOS 管在从导通到关断(关断损耗)或从关断到导通(开通损耗)的过渡过程中,因电压和电流存在交叠而产生的损耗。

- 开通损耗(Turn-On Loss): 开通时,漏极电压(\(V_{DS}\))尚未完全下降,漏极电流(\(I_{DS}\))已开始上升,两者交叠形成的功率损耗。

- 关断损耗(Turn-Off Loss): 关断时,漏极电流尚未完全下降,漏极电压已开始上升,两者交叠形成的功率损耗。

开关损耗与开关频率(\(f_{sw}\))直接相关,频率越高,单位时间内开关次数越多,总开关损耗越大。 近似计算公式:\(P_{sw} \approx \frac{1}{2} \times V_{DS} \times I_{DS} \times (t_{on} + t_{off}) \times f_{sw}\) (\(t_{on}\)为开通时间,\(t_{off}\)为关断时间)

3. 栅极驱动损耗(Gate Drive Loss)

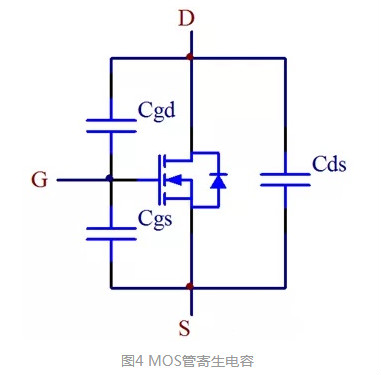

驱动电路为 MOS 管栅极充电和放电时消耗的能量(主要是对栅极电容充放电的损耗)。 计算公式:\(P_{gate} = V_{GS} \times Q_g \times f_{sw}\)

- 关键影响因素:

- 栅极总电荷\(Q_g\):MOS 管的固有参数,与栅极结构相关。

- 驱动电压\(V_{GS}\):驱动电路提供的栅极电压。

- 开关频率\(f_{sw}\):频率越高,充放电次数越多,损耗越大。

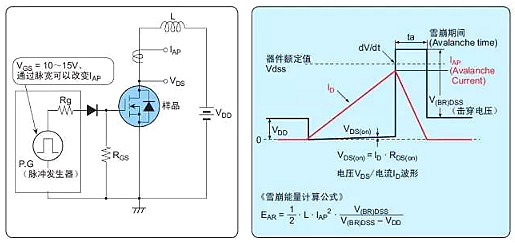

4. 反向恢复损耗(Reverse Recovery Loss)

仅存在于同步整流 MOS 管(如在 Buck 电路中作为续流管)中。当 MOS 管关断时,其体内寄生二极管(体二极管)因反向电流快速截止产生的损耗。

- 体二极管反向恢复时间(\(t_{rr}\))越长、反向恢复电荷(\(Q_{rr}\))越大,损耗越高。

- 高频应用中,此损耗尤为明显,通常需选择反向恢复特性好的 MOS 管(如肖特基势垒 MOS 管)。

5. 其他次要损耗

- 漏电流损耗:MOS 管关断时,漏极与源极之间的漏电流(\(I_{DSS}\))产生的损耗,通常极小,可忽略。

- 寄生电容损耗:漏极 - 源极电容(\(C_{DS}\))、漏极 - 栅极电容(\(C_{DG}\))在开关过程中充放电的损耗,高频下需考虑。

总结

MOS 管的总损耗是上述损耗的总和,其中导通损耗和开关损耗是主要部分(尤其在大功率、高频场景)。设计中需通过选择低\(R_{DS(on)}\)、快开关速度、低\(Q_g\)的 MOS 管,优化驱动电路和开关频率,以降低损耗,提高效率。

题目汇总--链接:

【硬件-笔试面试题】硬件/电子工程师,笔试面试题汇总版,持续更新学习,加油!!!-CSDN博客