半导体学习笔记

文章目录

- 半导体

- 与导体的区别

- 本征半导体

- 1. 本征激发现象

- 2. 复合现象

- N型半导体

- 1. 纯硅已经是半导体了,为什么还要掺杂磷呢?

- 2.为什么叫N型半导体?

- 载流子

- P型半导体

- PN结

- 伏安特性曲线

- 电源正接

- 电源反接

- 二极管

- 二极管分类

- 1. 整流二极管

- 半波整流

- 全波整流

- 2. 稳压二极管(齐纳二极管)

- 3. 发光二极管

- 应用场景

- 为什么要给LED增加限流电阻

- 三极管(Bipolar Junction Transistor)

- NPN型三极管

- PNP型三极管

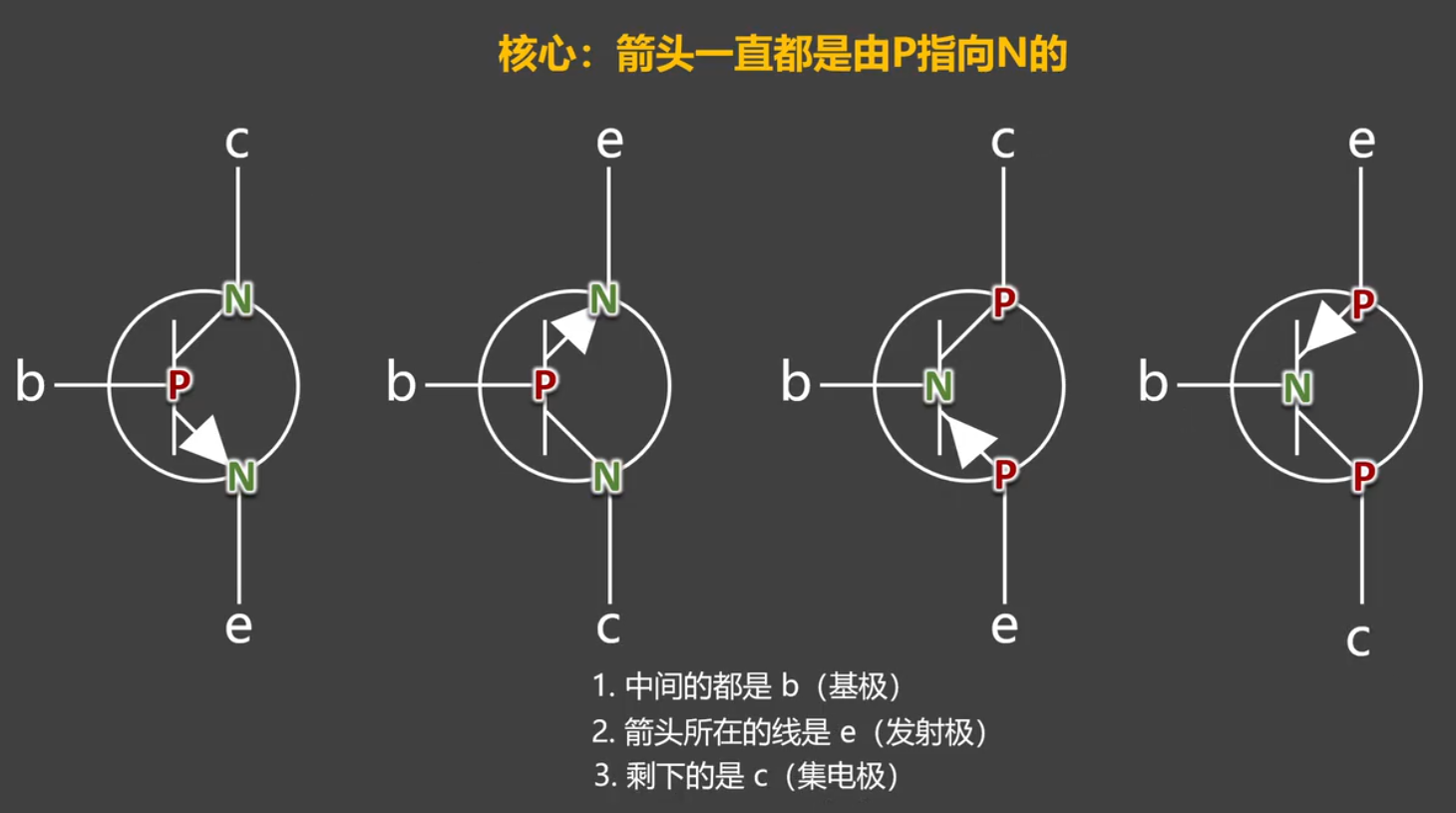

- 三极管极性

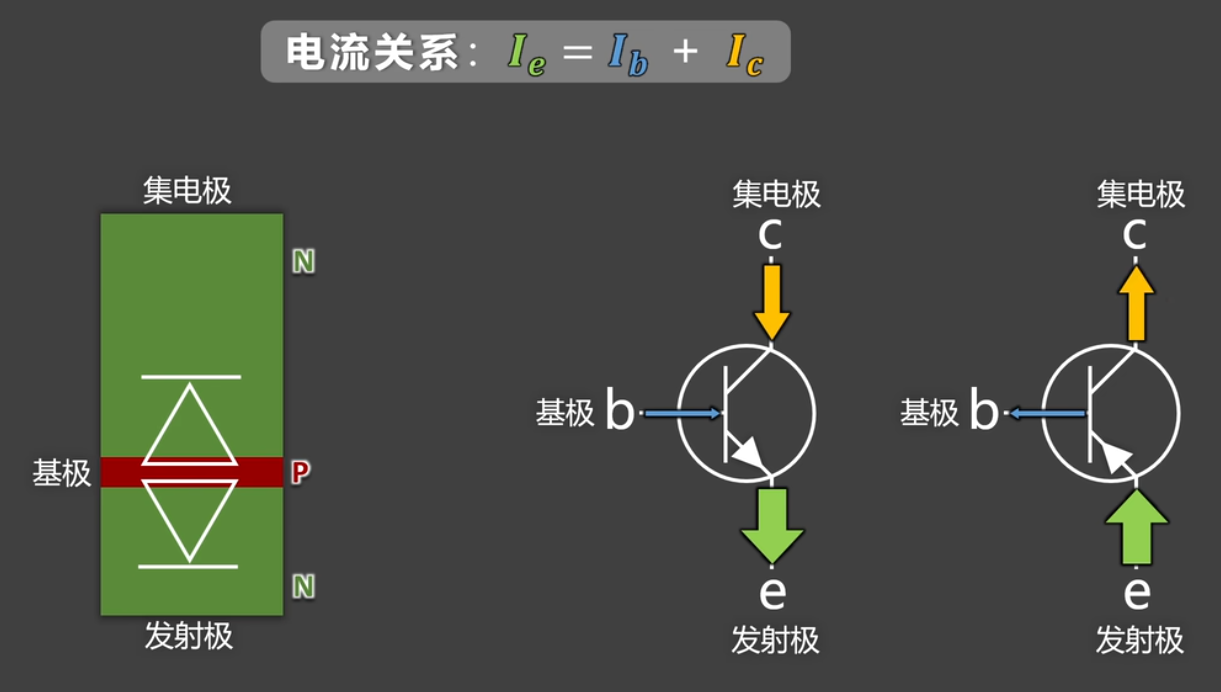

- 三极管的电流关系

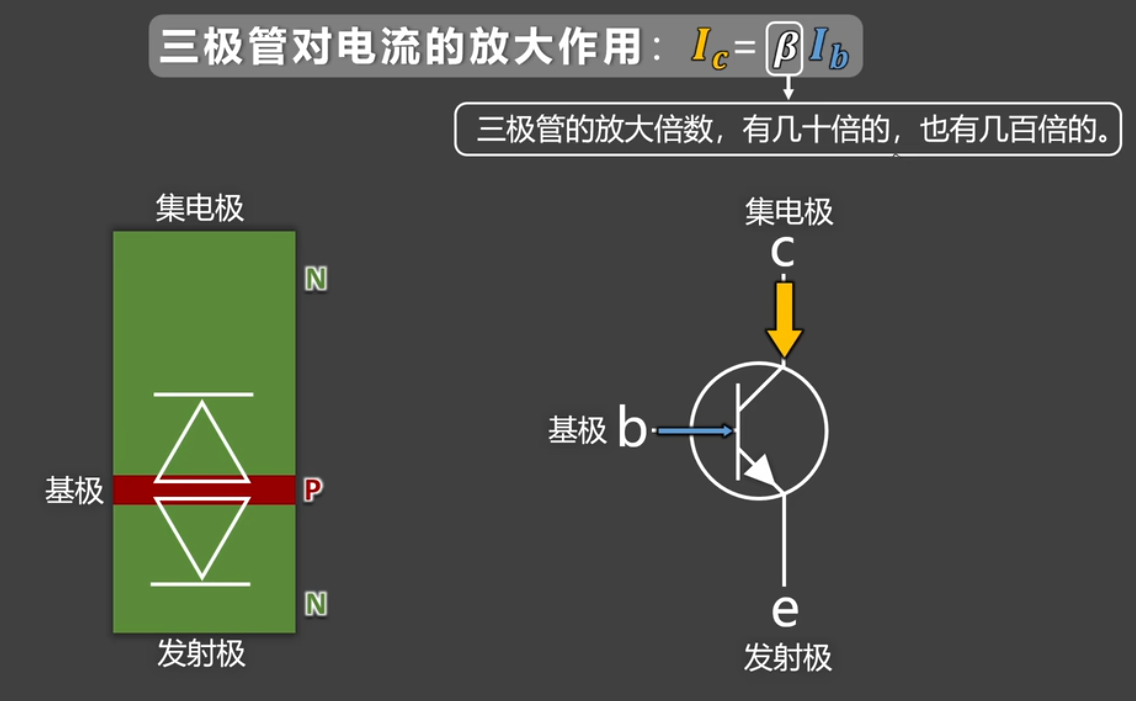

- 三极管对电流的放大作用

- 三极管的三种状态

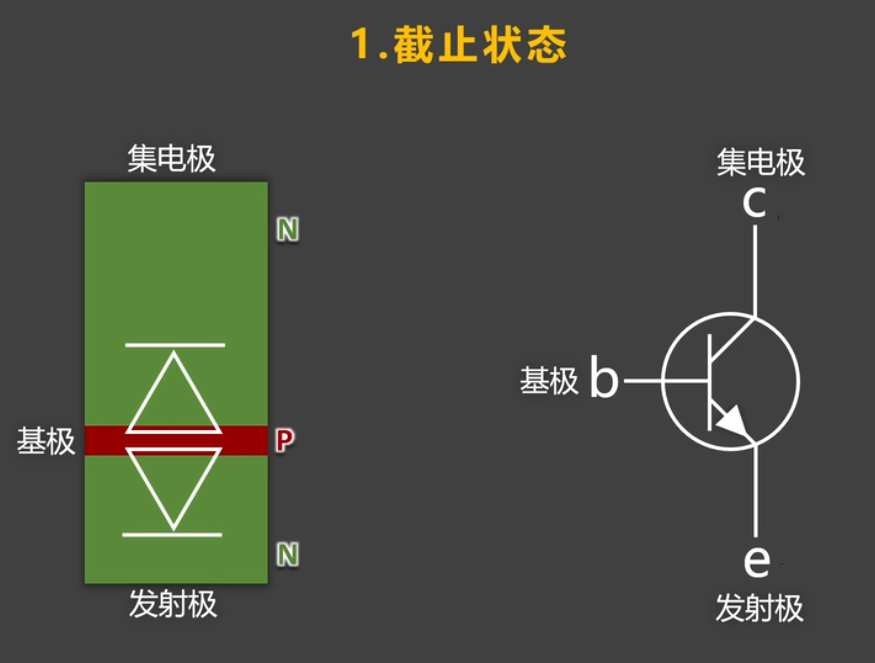

- 截至状态

- 放大状态

- 饱和状态

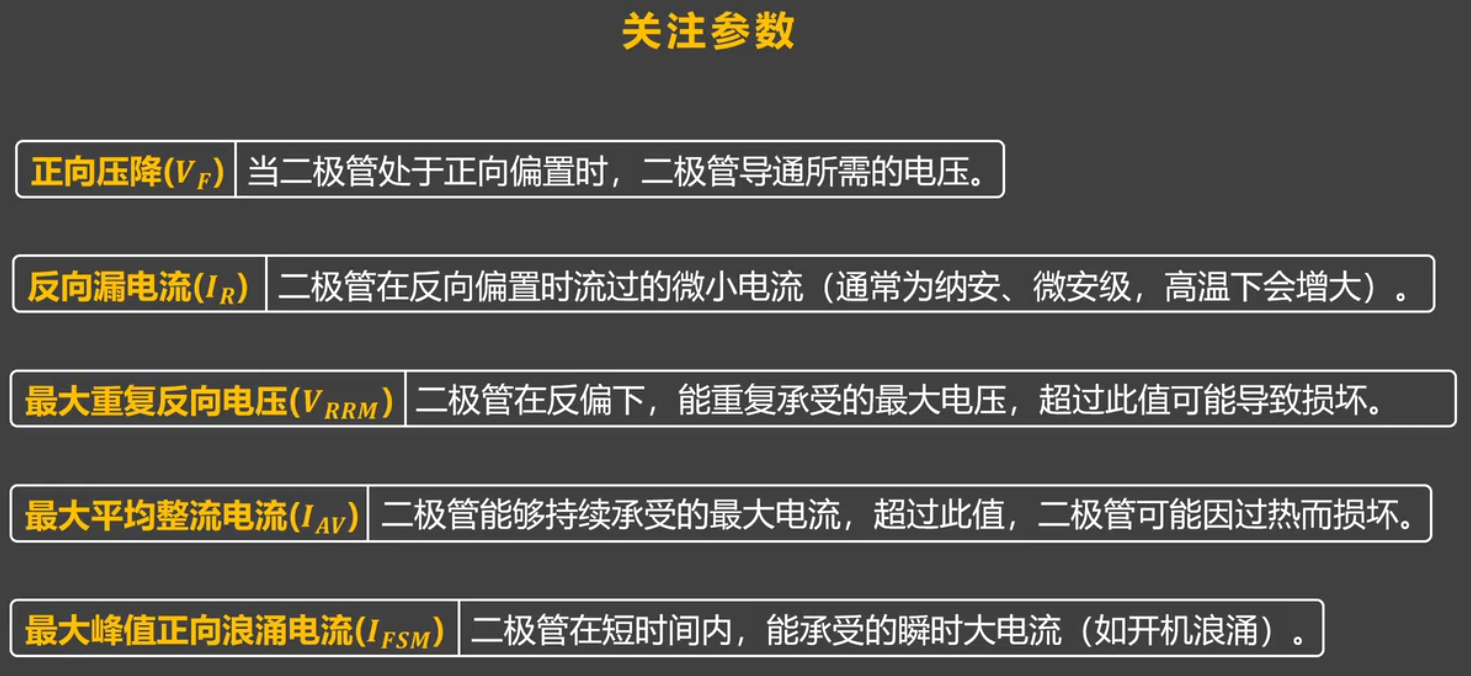

- 关注参数

- 三极管实现光感灯

- MOS管(Metal Oxide Semiconductor FIeld Effect Transistor)

- N沟道-增强型

- 可以简化为一个电源

- N沟道-耗尽型

- N沟道 增强型和耗尽型区别

- P沟道-增强型

- P沟道 增强型和耗尽型区别

- MOS管的快速判断

- MOS管实操

- 1. MOS管栅极的“电容本质”

- 2. 无下拉电阻时:电荷无法释放,MOS管持续导通

- 3. 增加下拉电阻后:提供放电回路,确保MOS管关断

- 补充:上拉/下拉电阻的共性逻辑

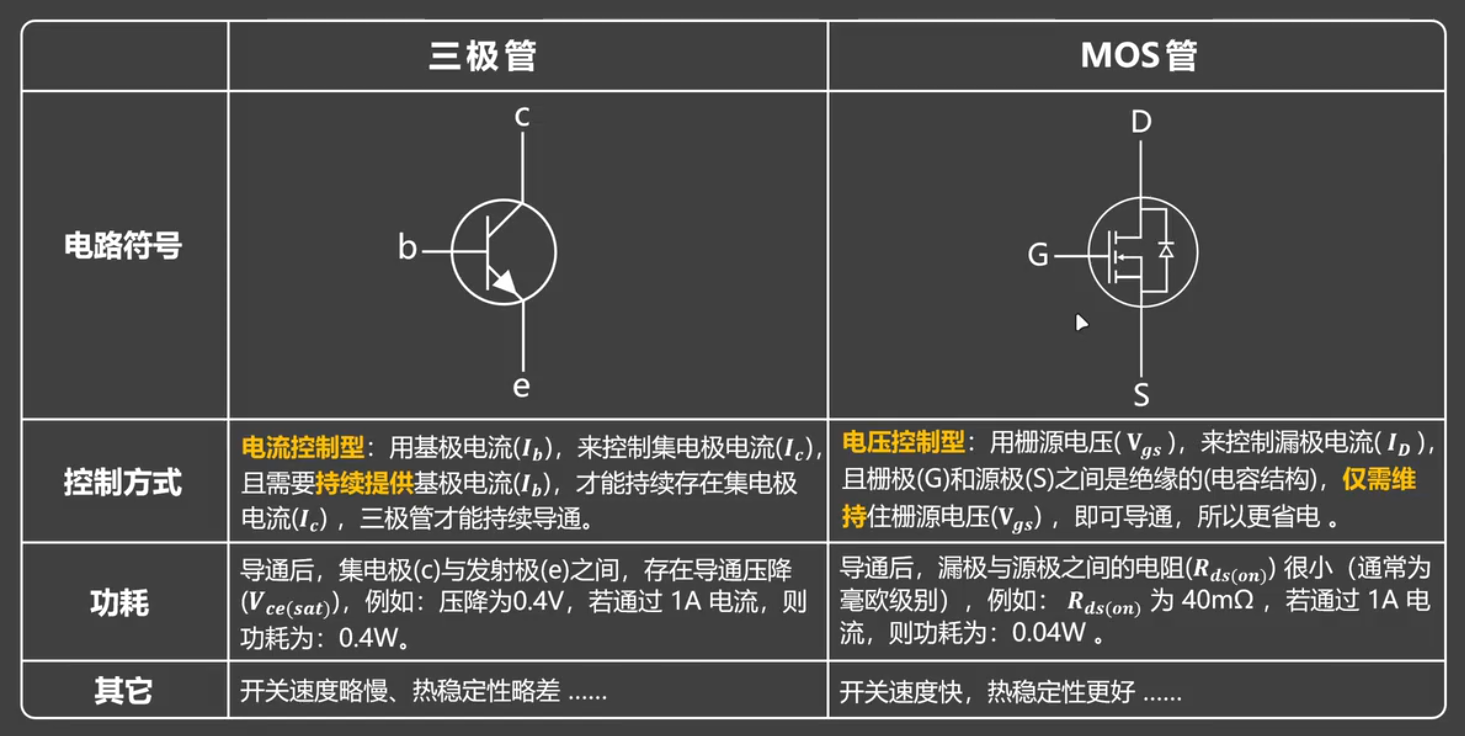

- 三极管与MOS管的区别

半导体

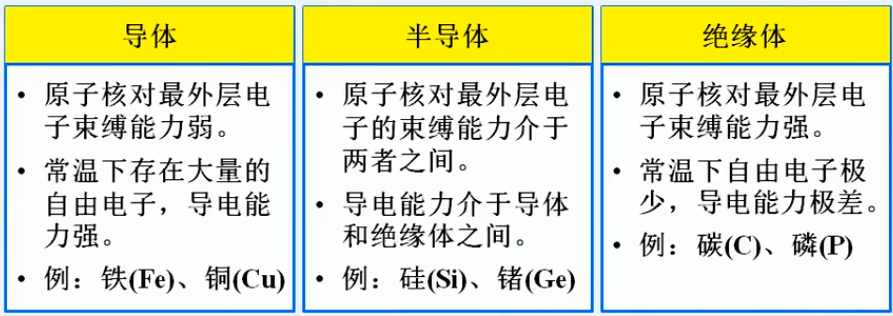

与导体的区别

- 导体只有一种载流子,只有自由电子导电。

- 半导体有两种载流子,自由电子与空穴均参与导电。

本征半导体

硅晶体在高温下,能从绝缘体变成导体,是其材料的天然物理特性,是不需要掺杂任何其他的成分。

1. 本征激发现象

指在本征半导体中,由于外部的热能、光能、电场等激励下在材料内部形成自由电子+空穴对的现象。

注意:本征半导体是电中性的!

2. 复合现象

自由电子与空穴相遇后填补空穴,使两者同时消失的现象

N型半导体

N型半导体,几乎都是搭配P型半导体一起来使用,形成PN结

向硅晶体中掺杂适量的磷原子,磷原子最外层有5个电子,它会和周围的4个硅原子组成4个共价键,这样每个磷原子都可以提供1个自由电子

1. 纯硅已经是半导体了,为什么还要掺杂磷呢?

能让半导体的导电性能更好,并且让半导体导电性更容易控制。

2.为什么叫N型半导体?

由于磷元素的加入,带来了更多的自由电子使半导体中负电荷载流子的数量大幅增加,因此这种半寻体被称为N型(Negative)半导体。

载流子

在导电过程中能够携带电荷并产生电流的粒子

- 在金属导体中,载流子是自由电子。

- 在某些盐溶液中,载流子可能是正离子或负离子

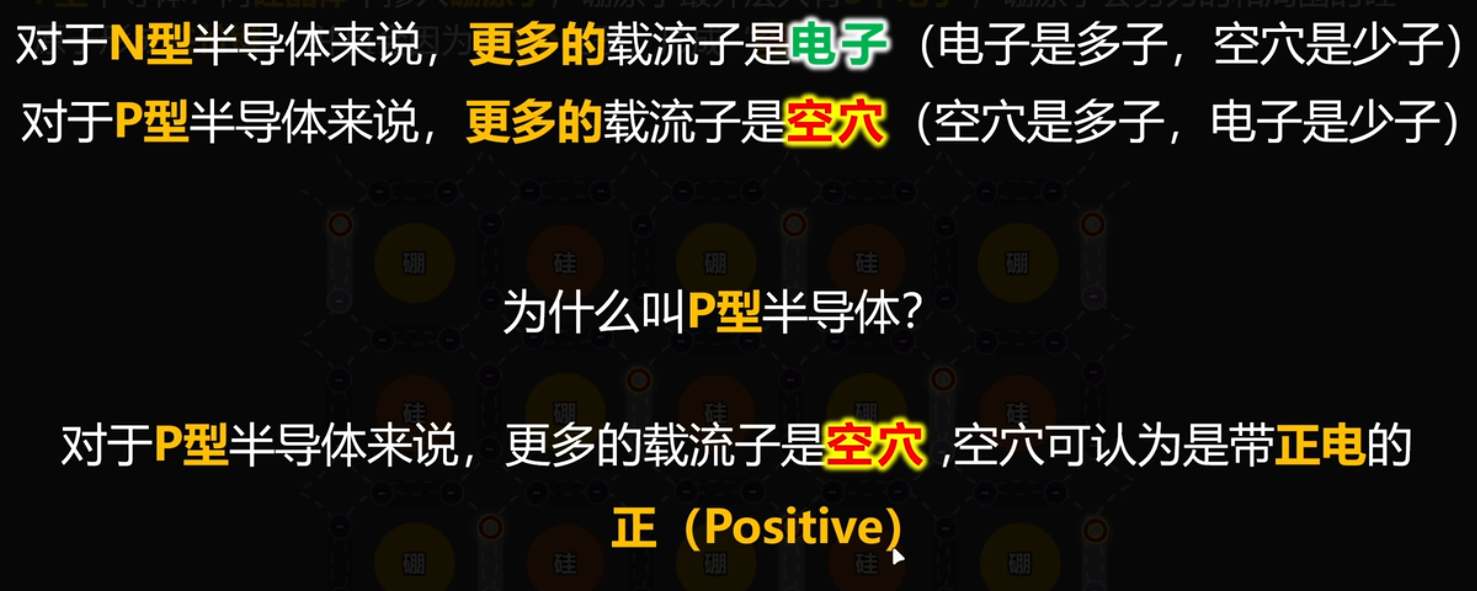

P型半导体

向硅晶体中掺入硼原子,硼原子最外层只有3个电子,硼原子会努力的和周围的硅原子形成共价键, 并且会因为缺1个电子,形成"空穴"

PN结

N型半导体的自由电子被吸引至P区导致N型半导体PN结中间区域带正电,P型半导体带负电,从而形成内建电场

由于内建电场的存在,阻止了更多的电子从N区扩散到P区

中间形成的区域叫做:耗尽区 / 空间电荷区 / 势垒区

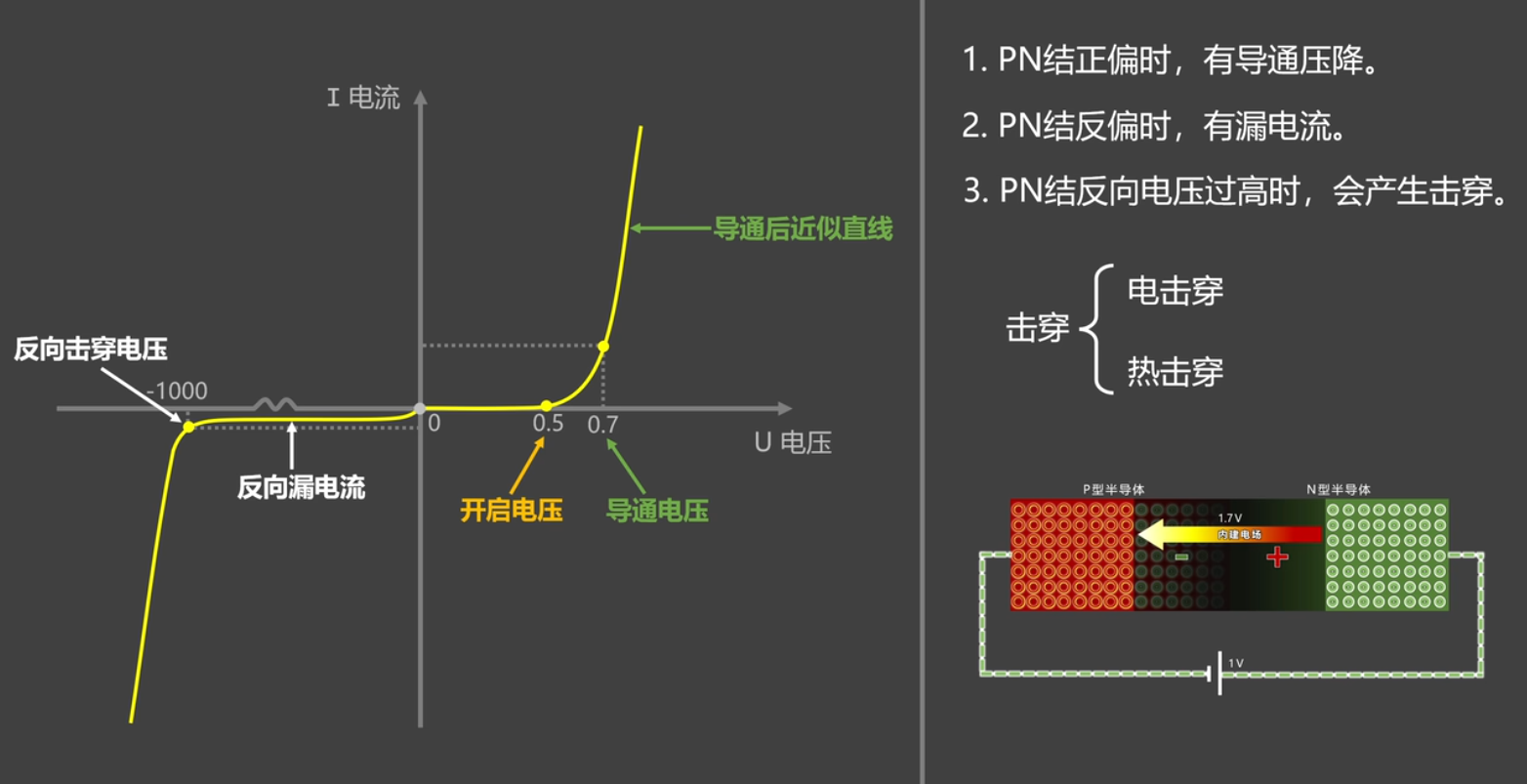

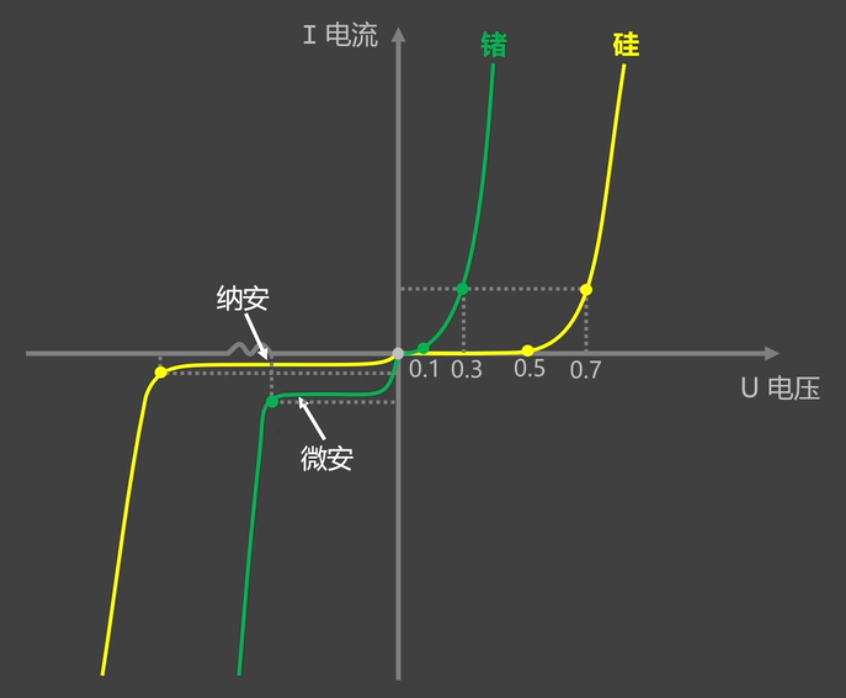

伏安特性曲线

电源正接

电源反接

二极管

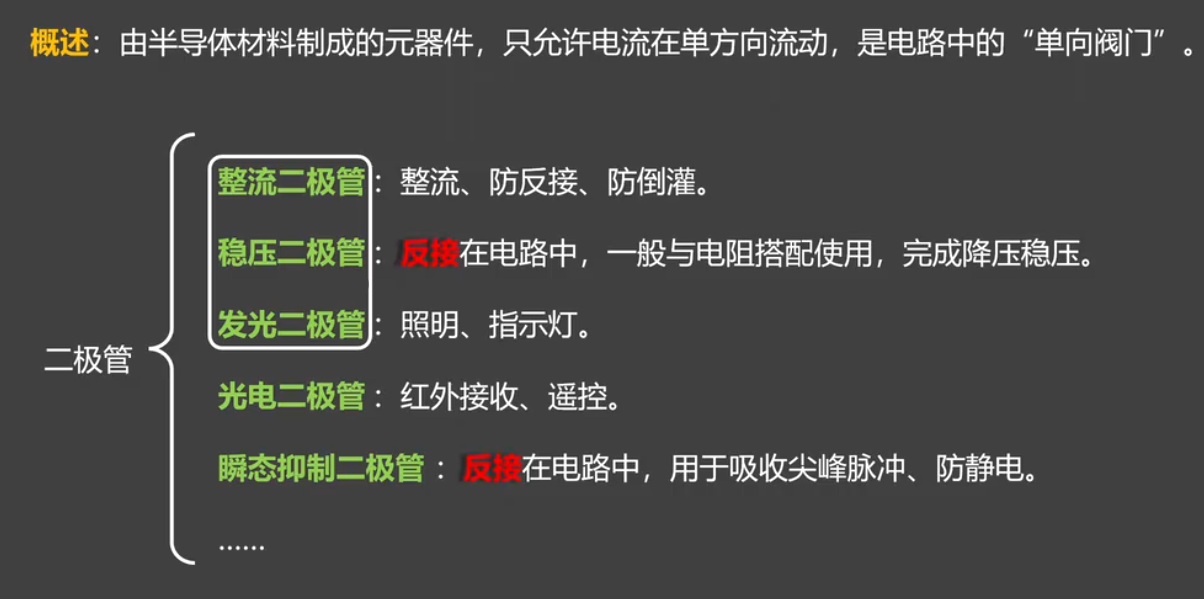

二极管分类

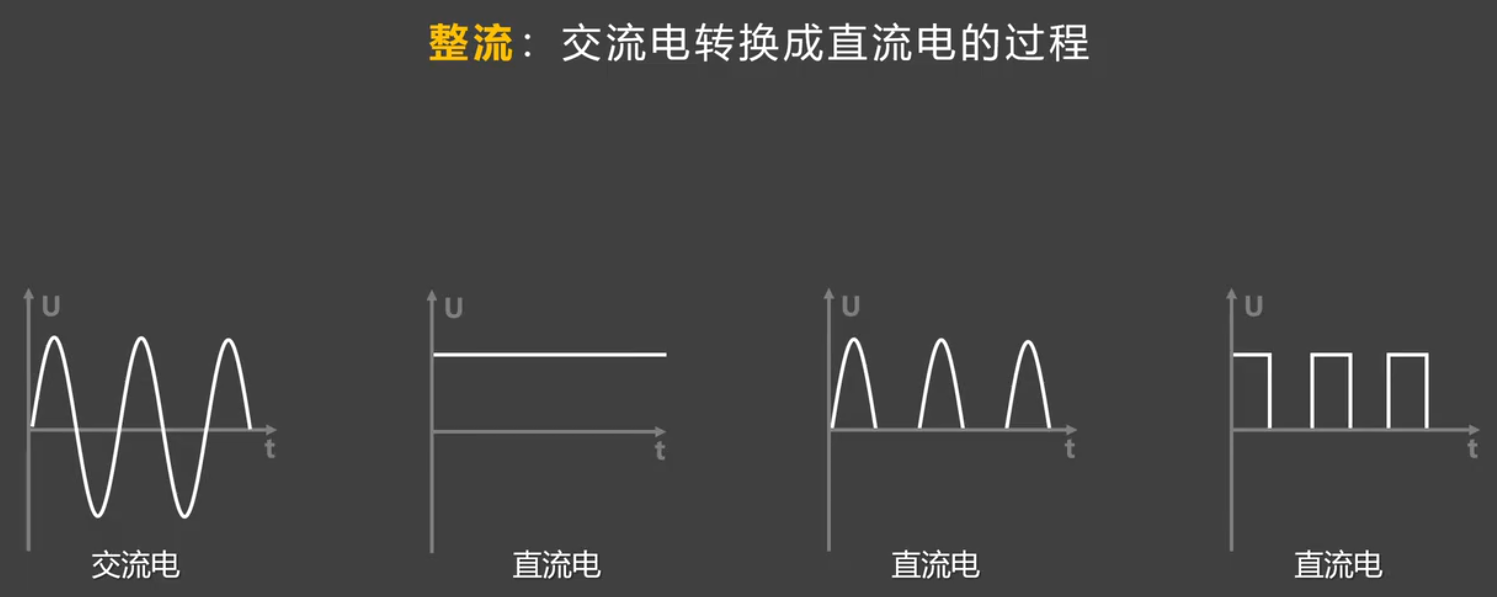

1. 整流二极管

作用:整流、防反接、防倒灌

半波整流

全波整流

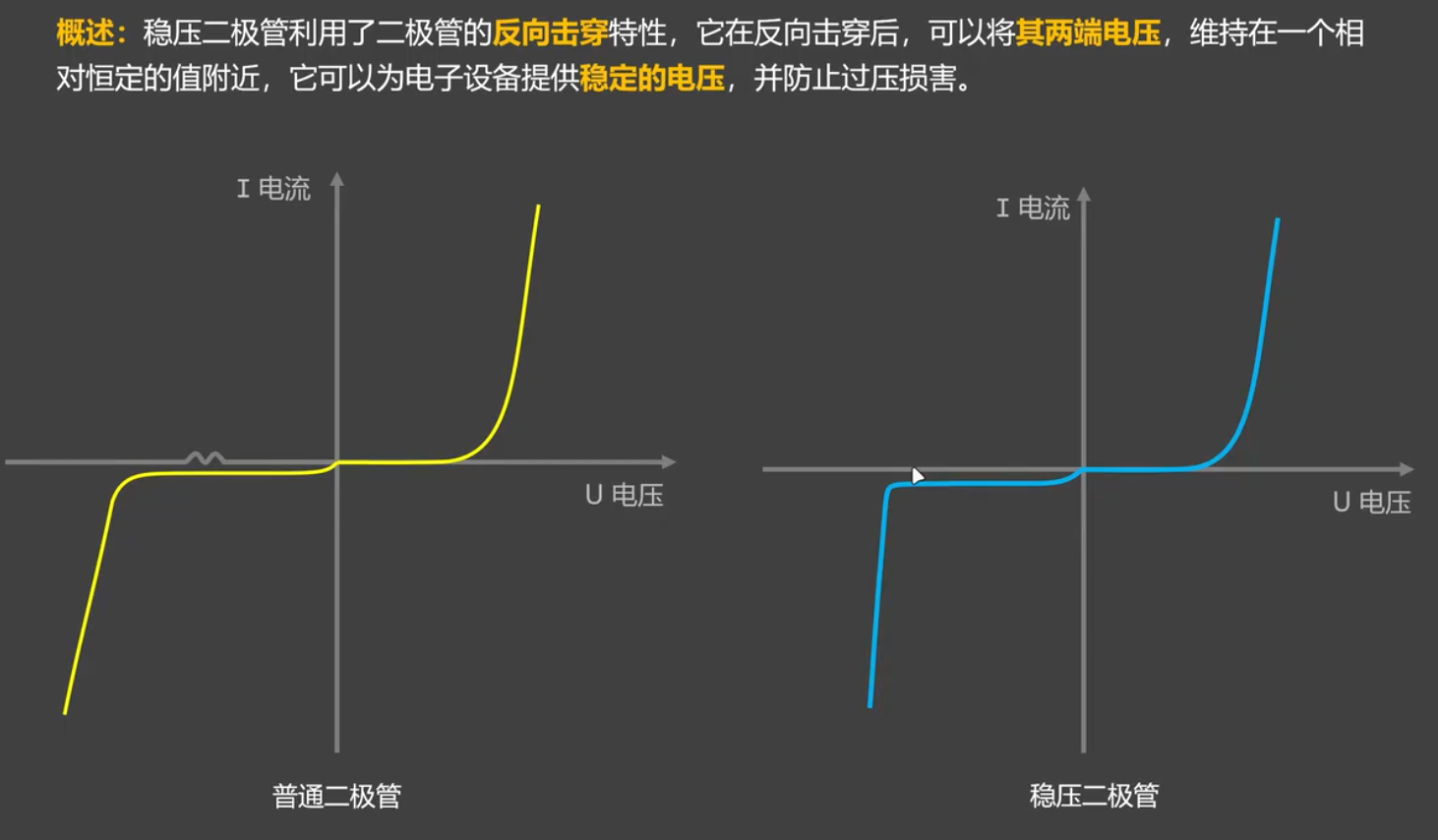

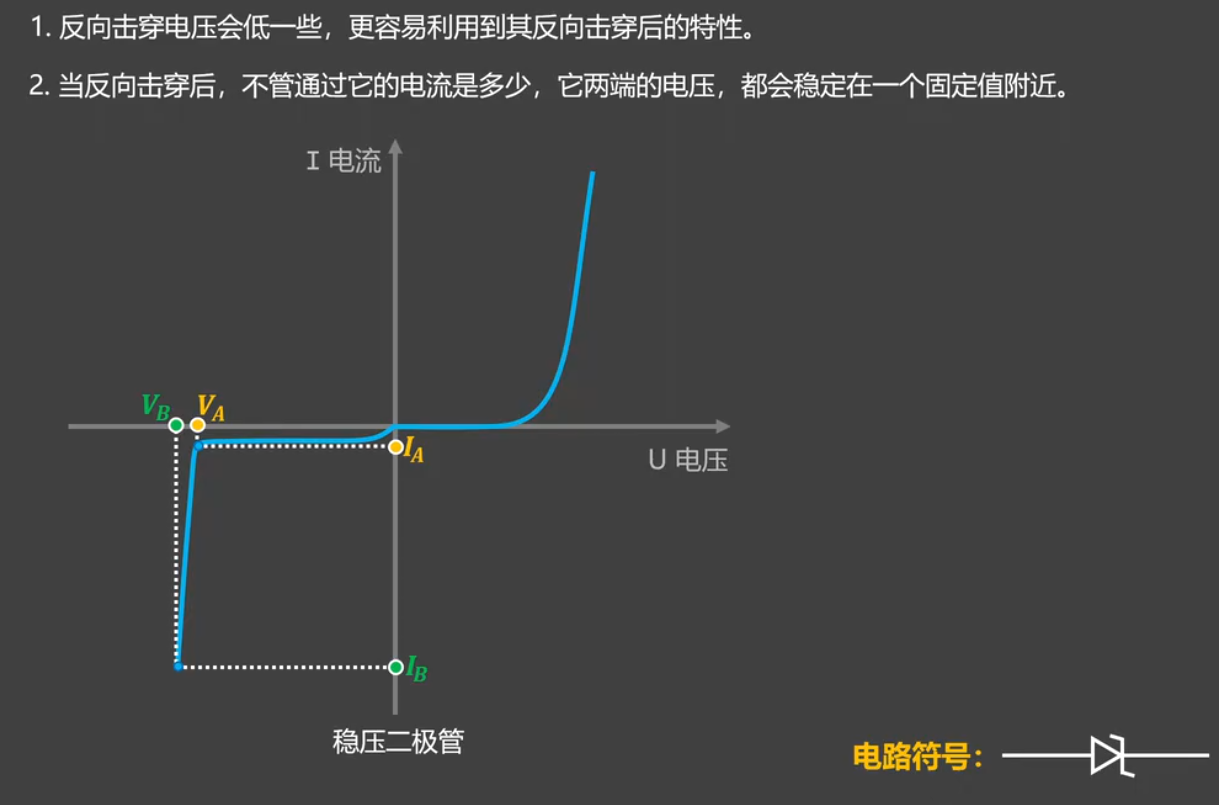

2. 稳压二极管(齐纳二极管)

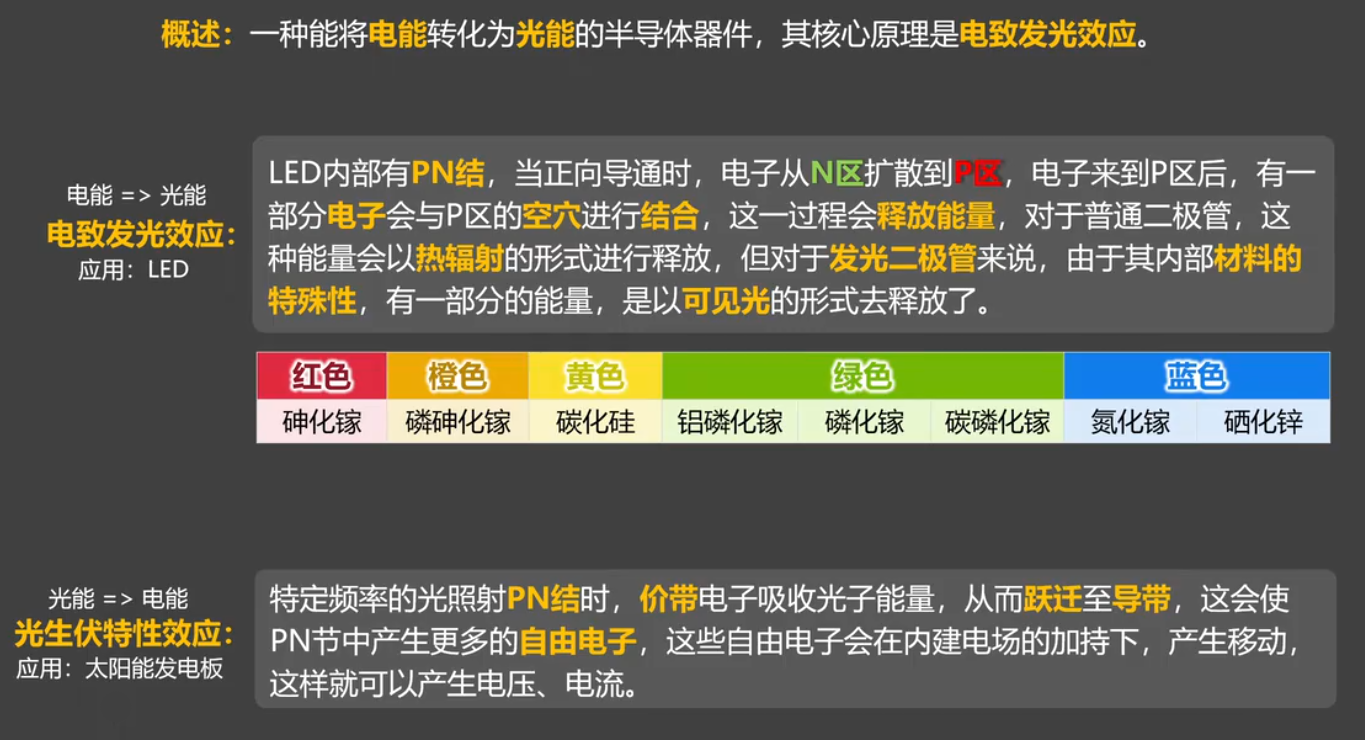

3. 发光二极管

应用场景

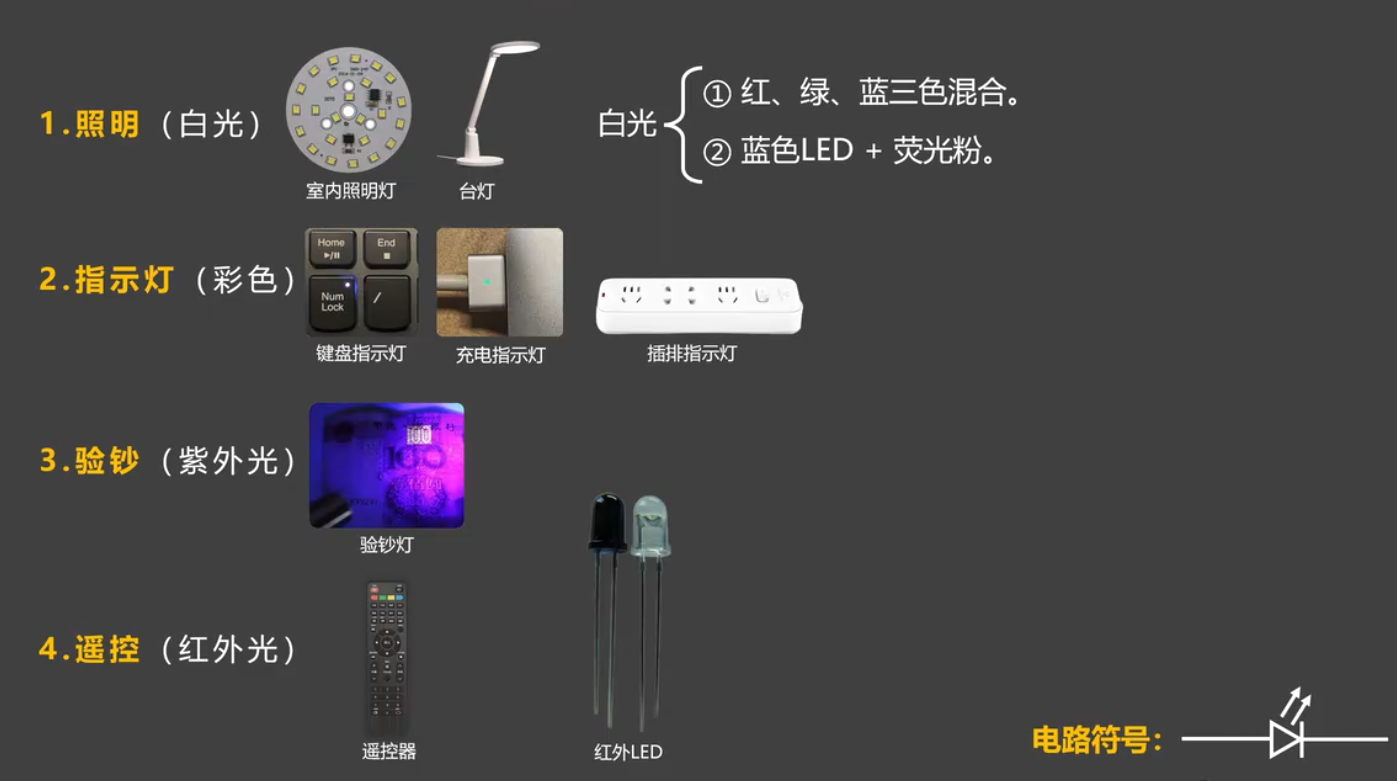

为什么要给LED增加限流电阻

三极管(Bipolar Junction Transistor)

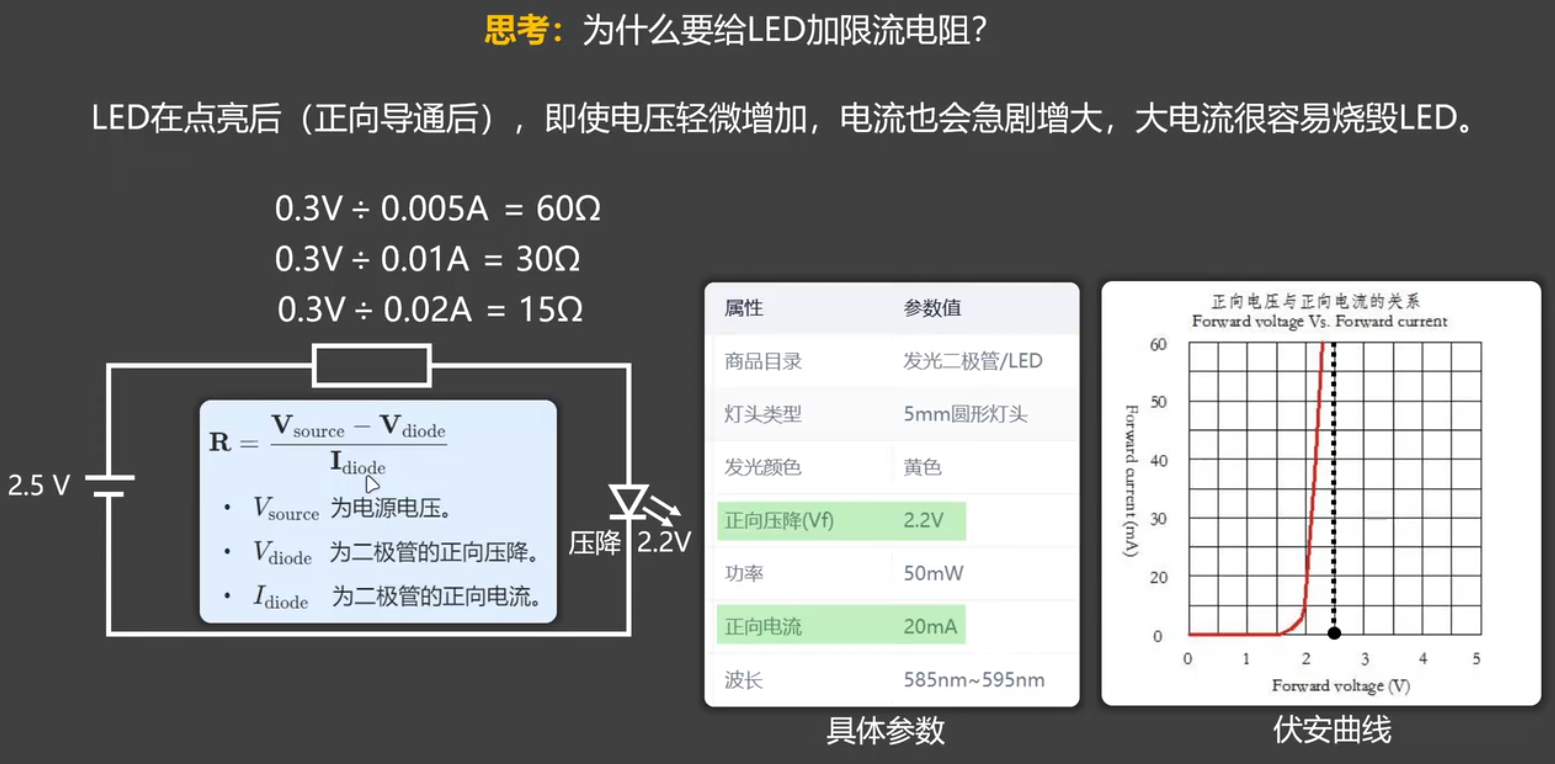

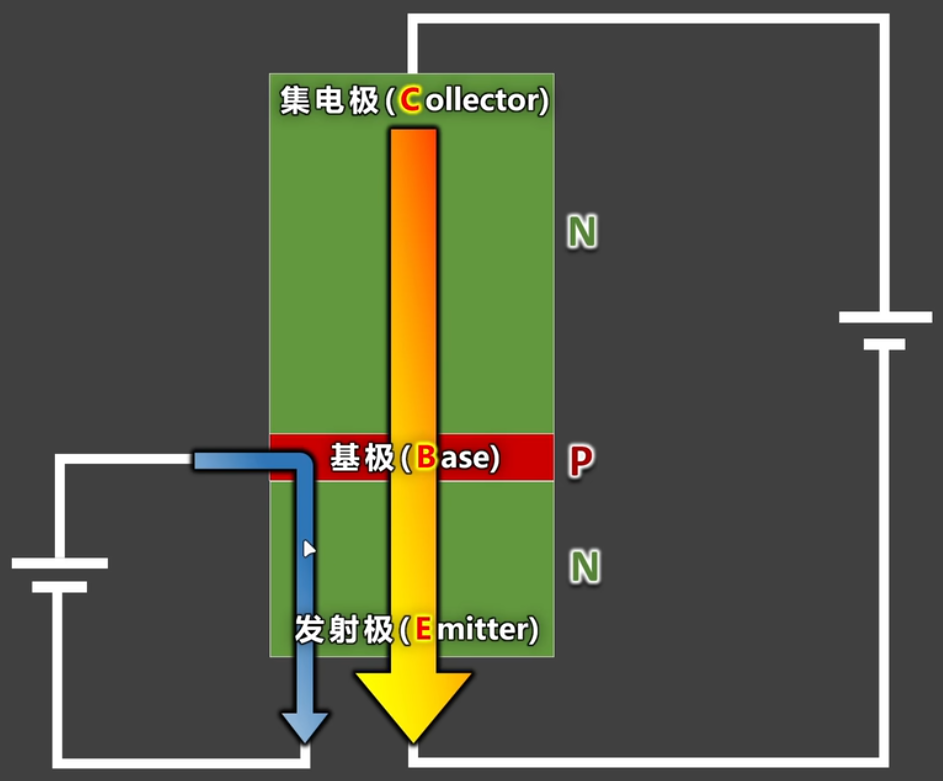

NPN型三极管

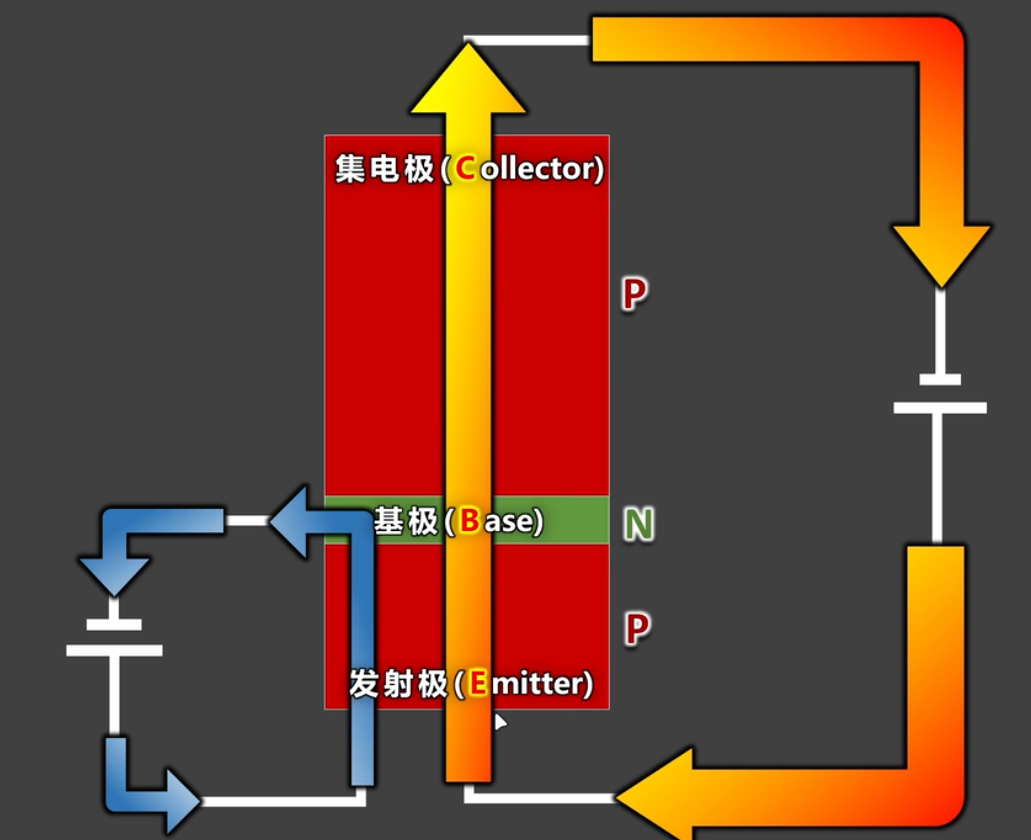

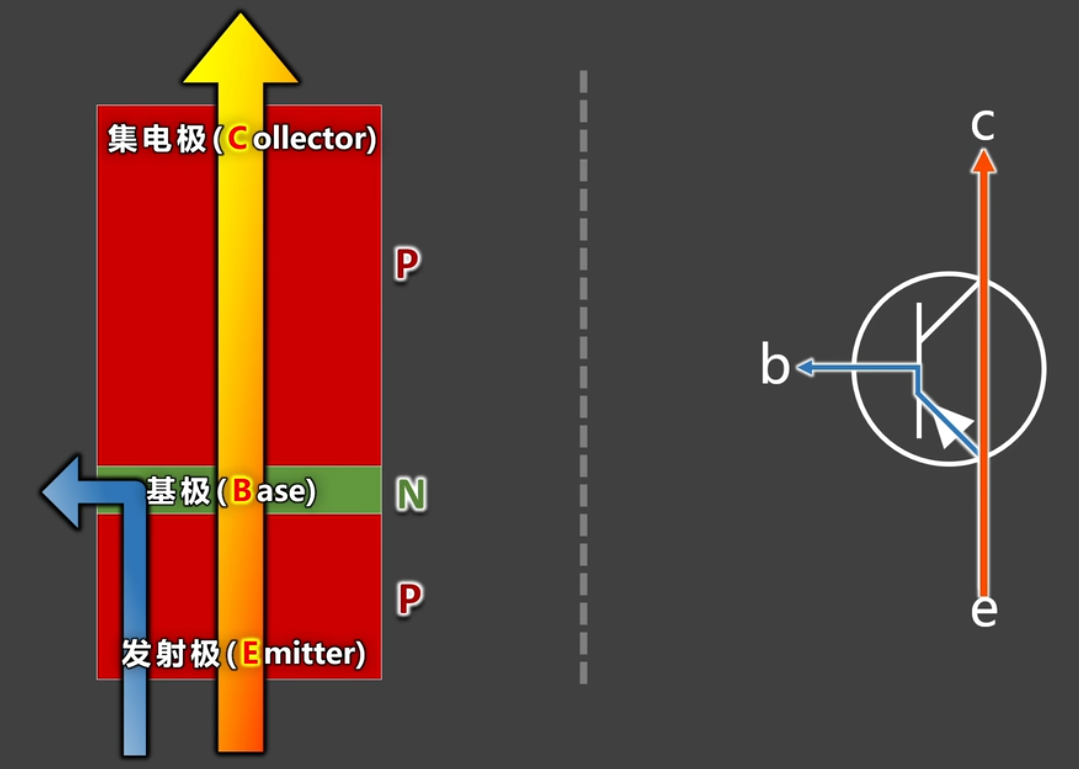

PNP型三极管

三极管极性

三极管的电流关系

三极管对电流的放大作用

三极管的三种状态

截至状态

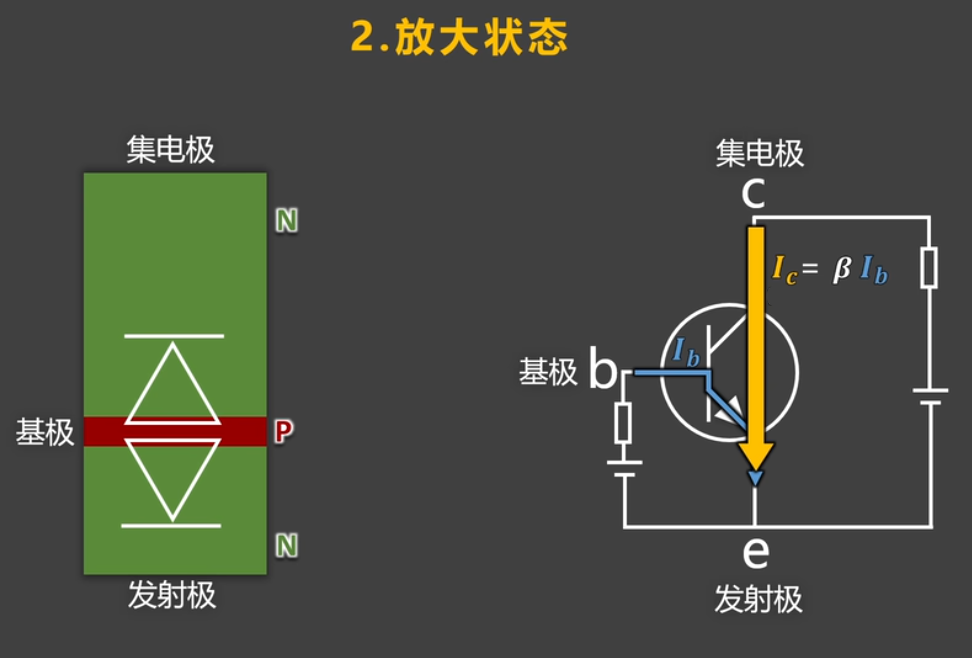

放大状态

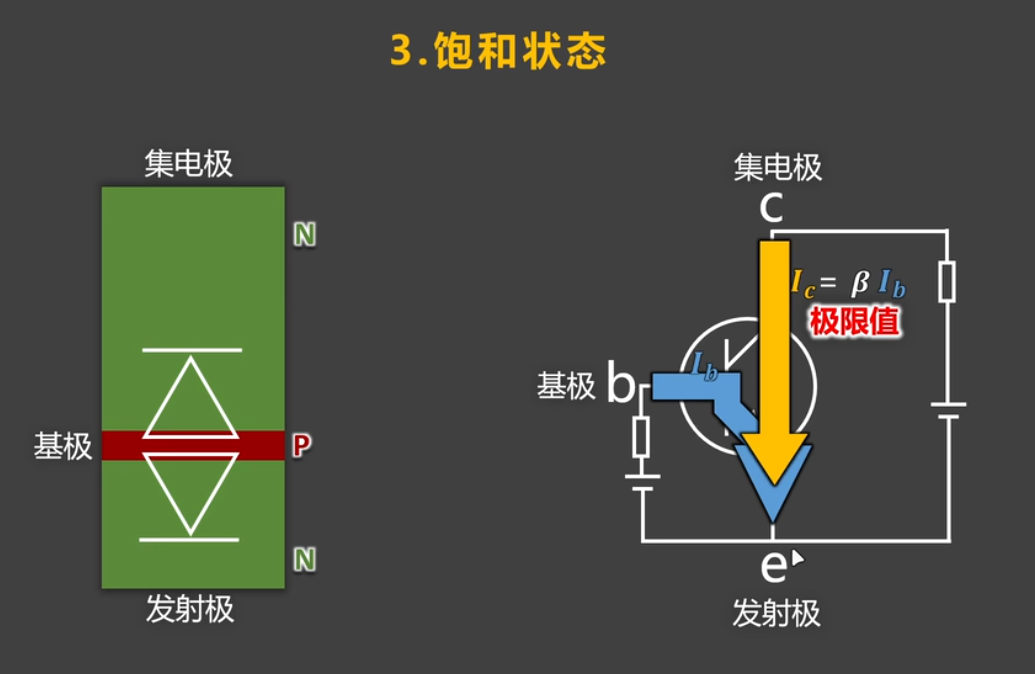

饱和状态

Ic的极限值为电源所能提供的最大电流,Ic达到极限值之后,Ib再怎么增大Ic也不会受其影响

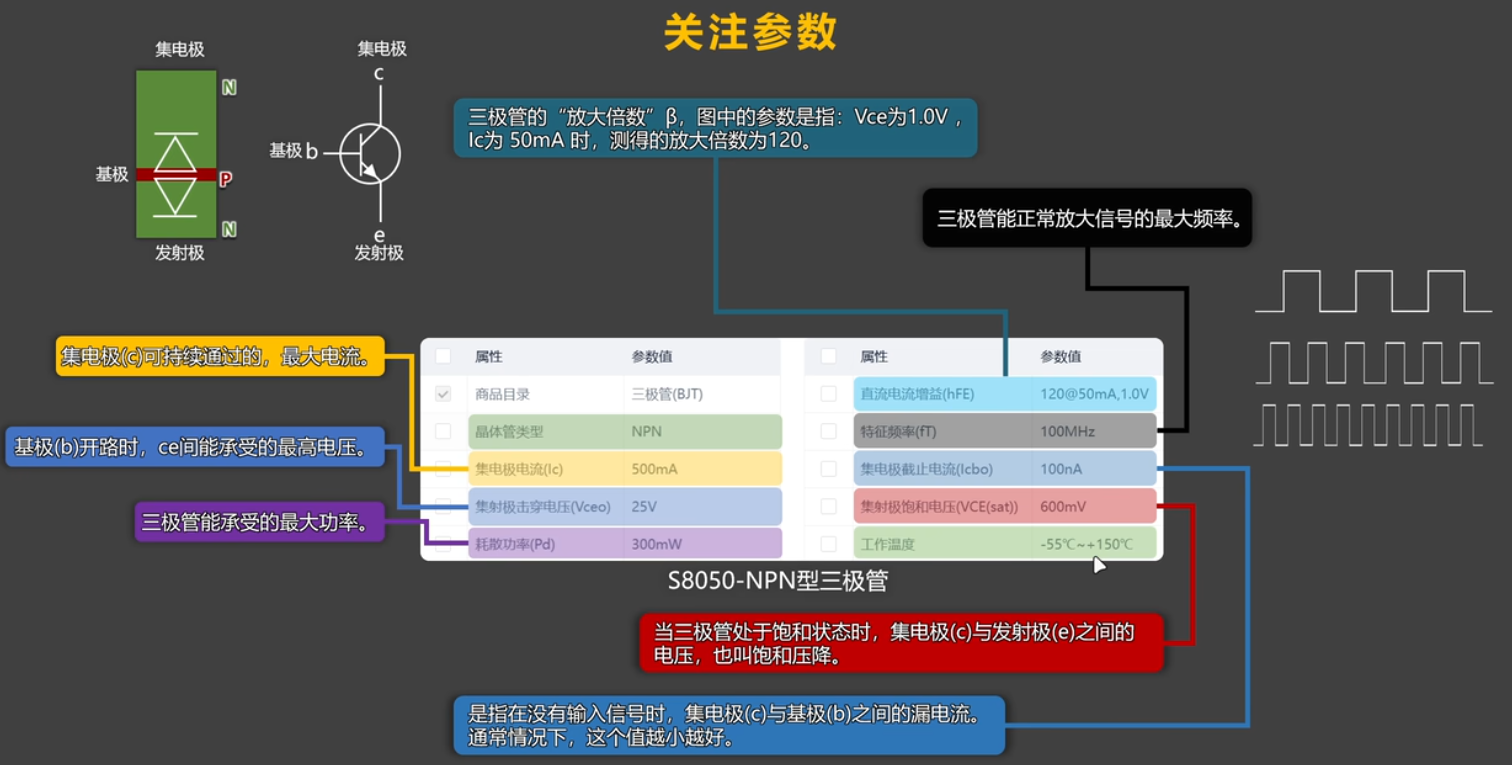

关注参数

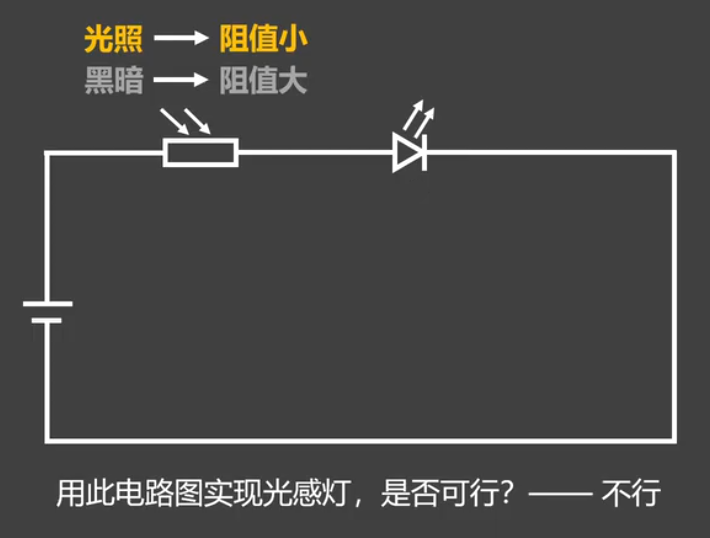

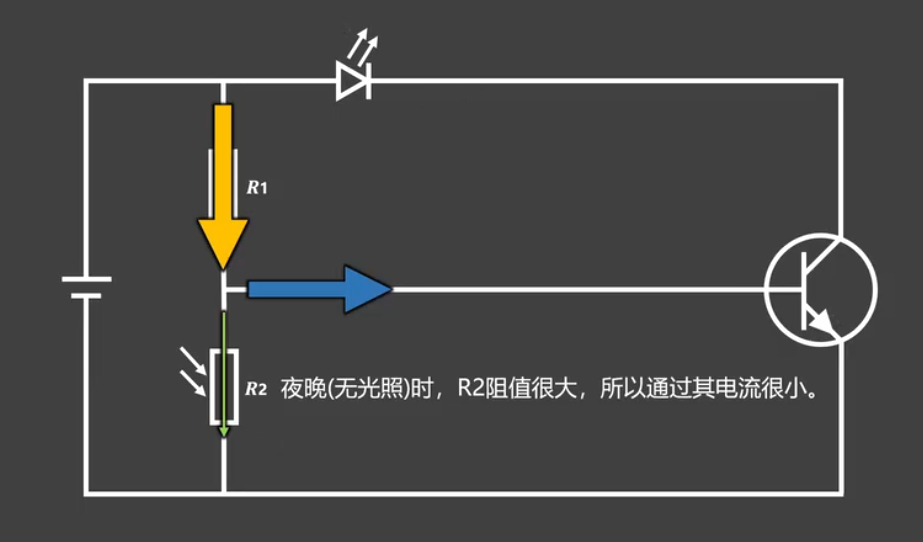

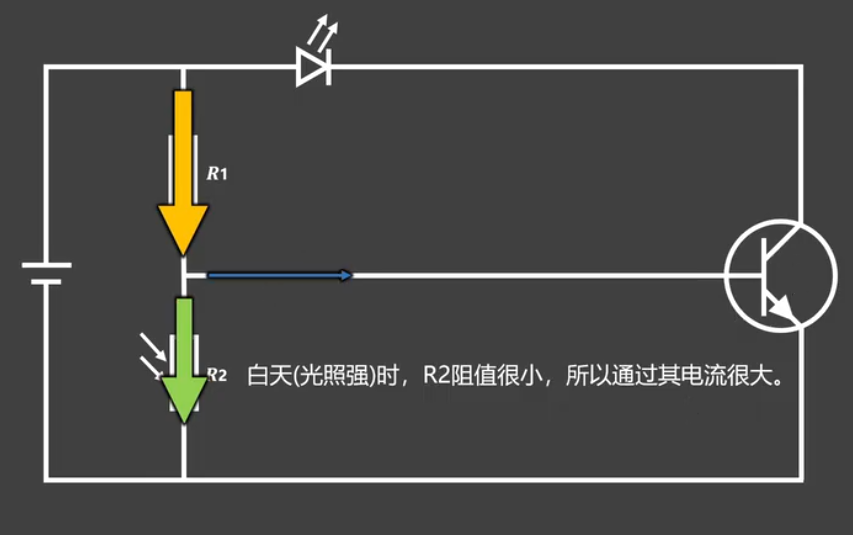

三极管实现光感灯

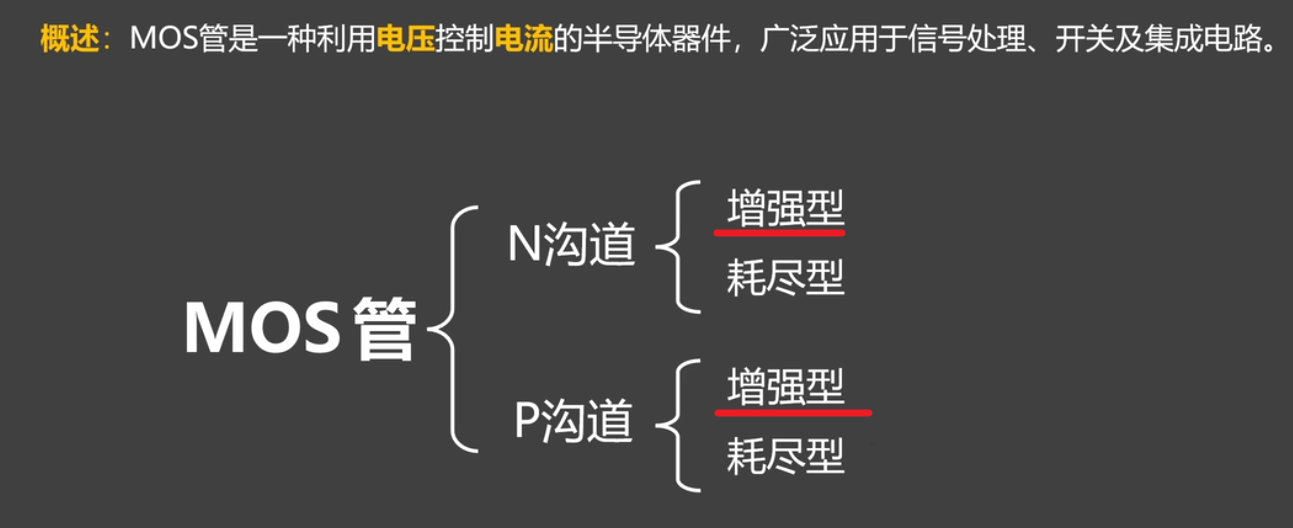

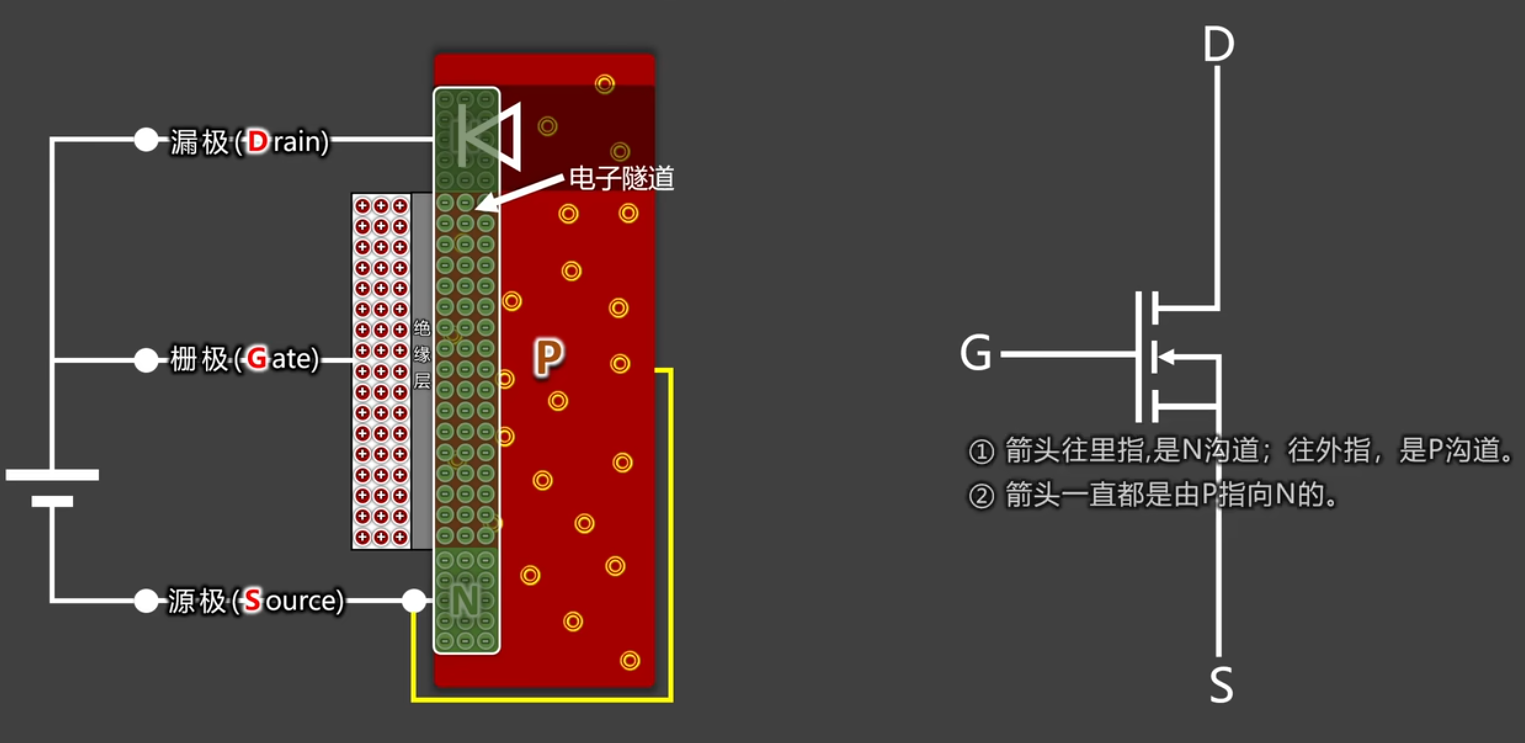

MOS管(Metal Oxide Semiconductor FIeld Effect Transistor)

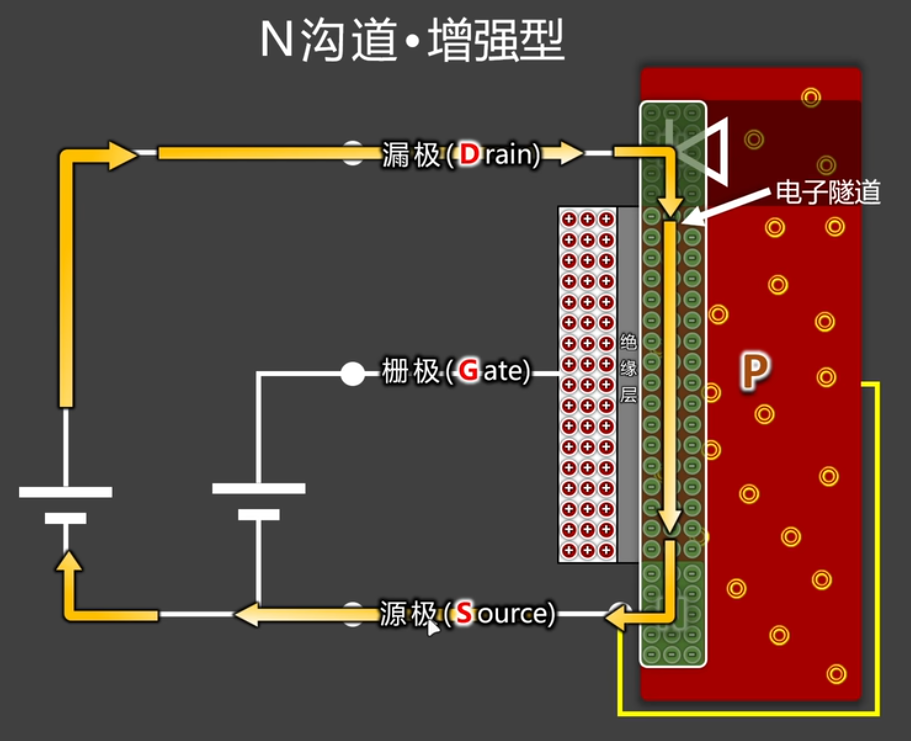

N沟道-增强型

可以简化为一个电源

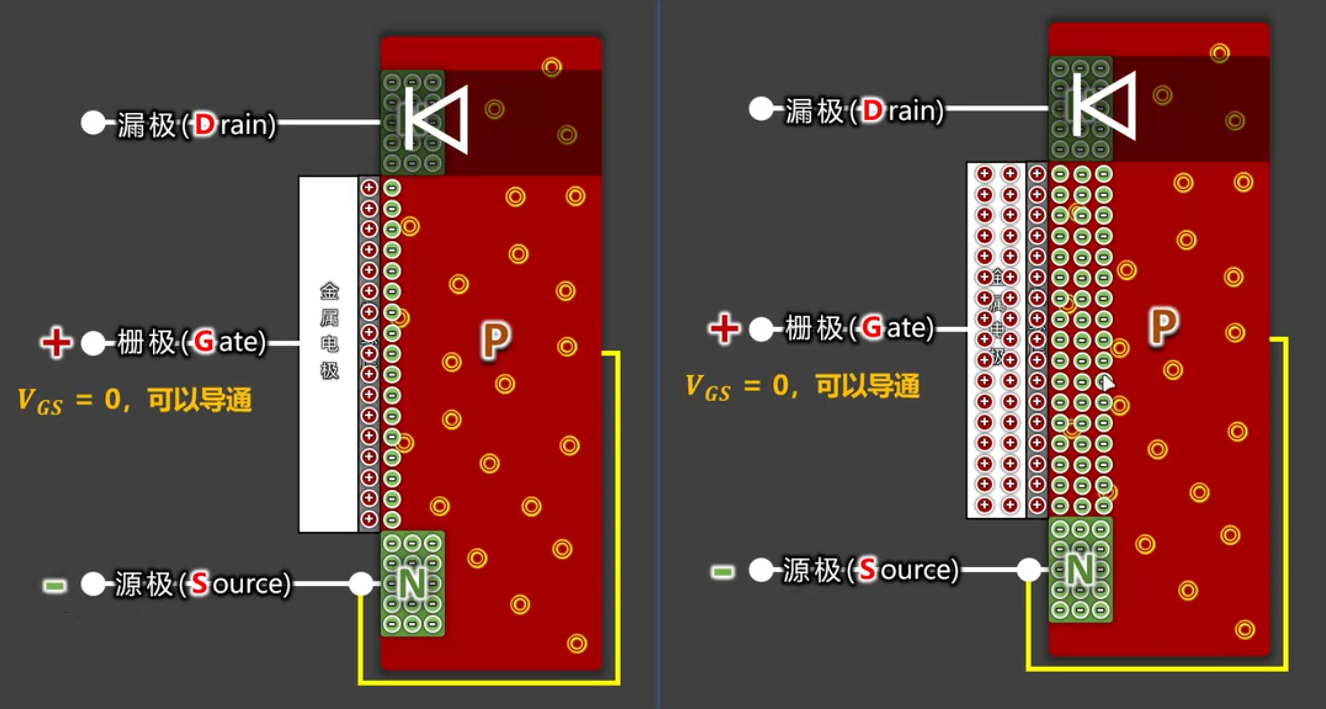

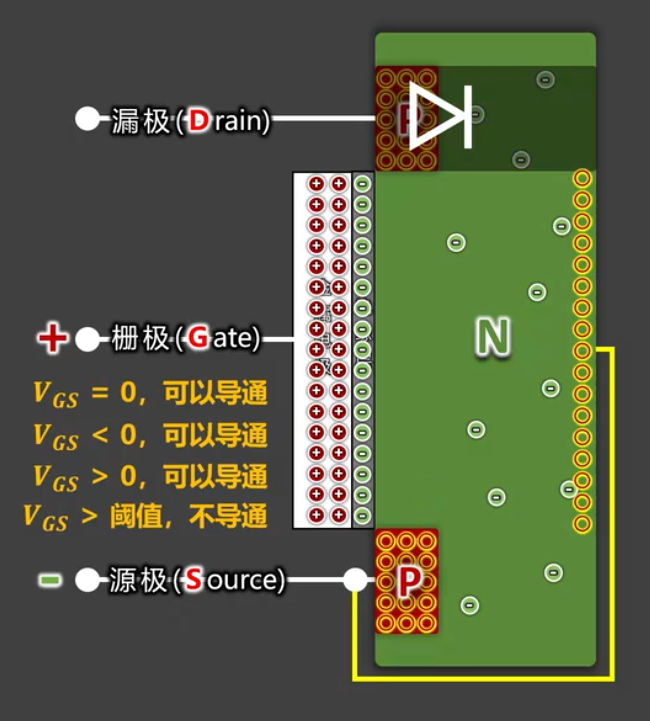

N沟道-耗尽型

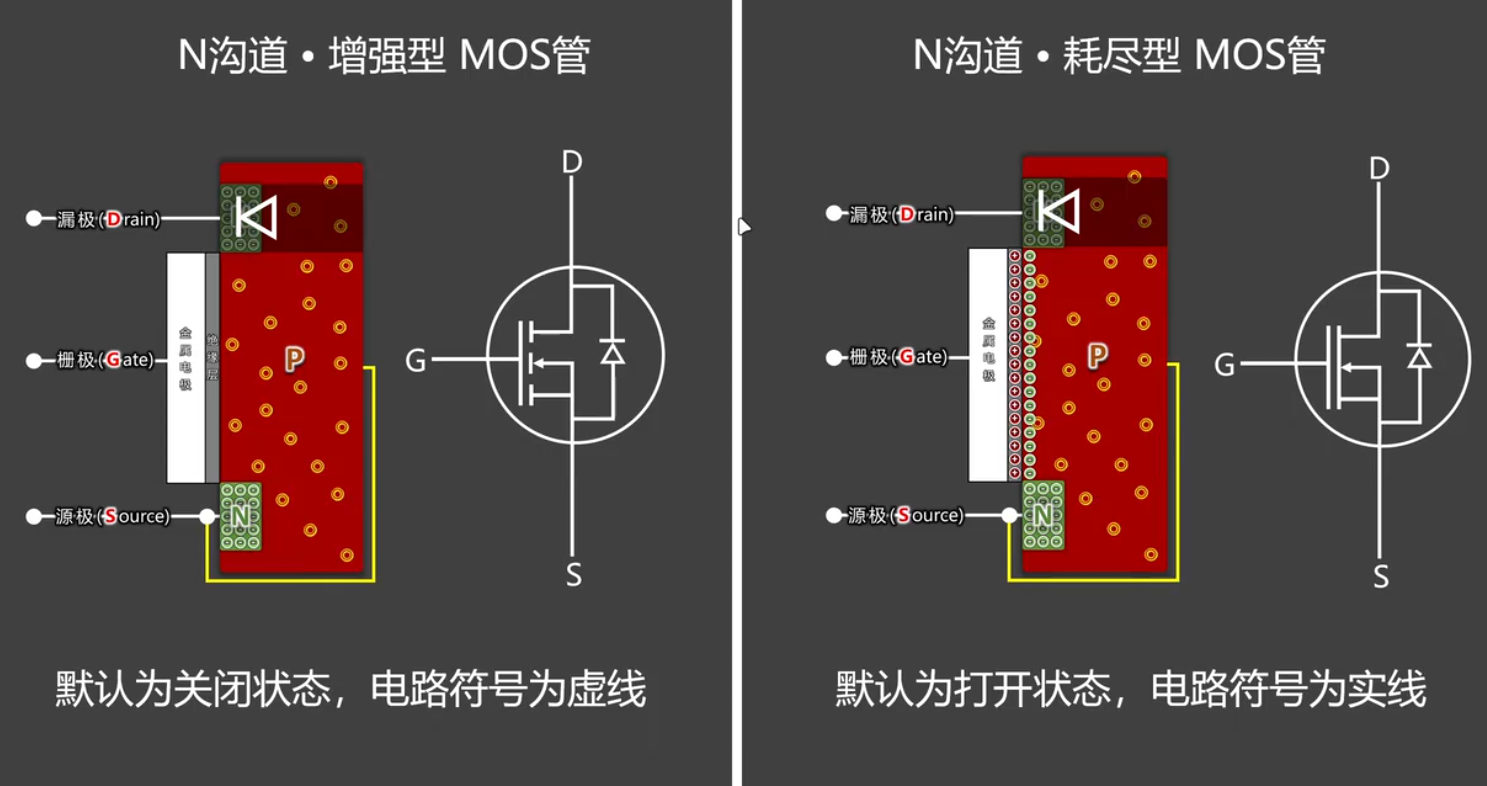

N沟道 增强型和耗尽型区别

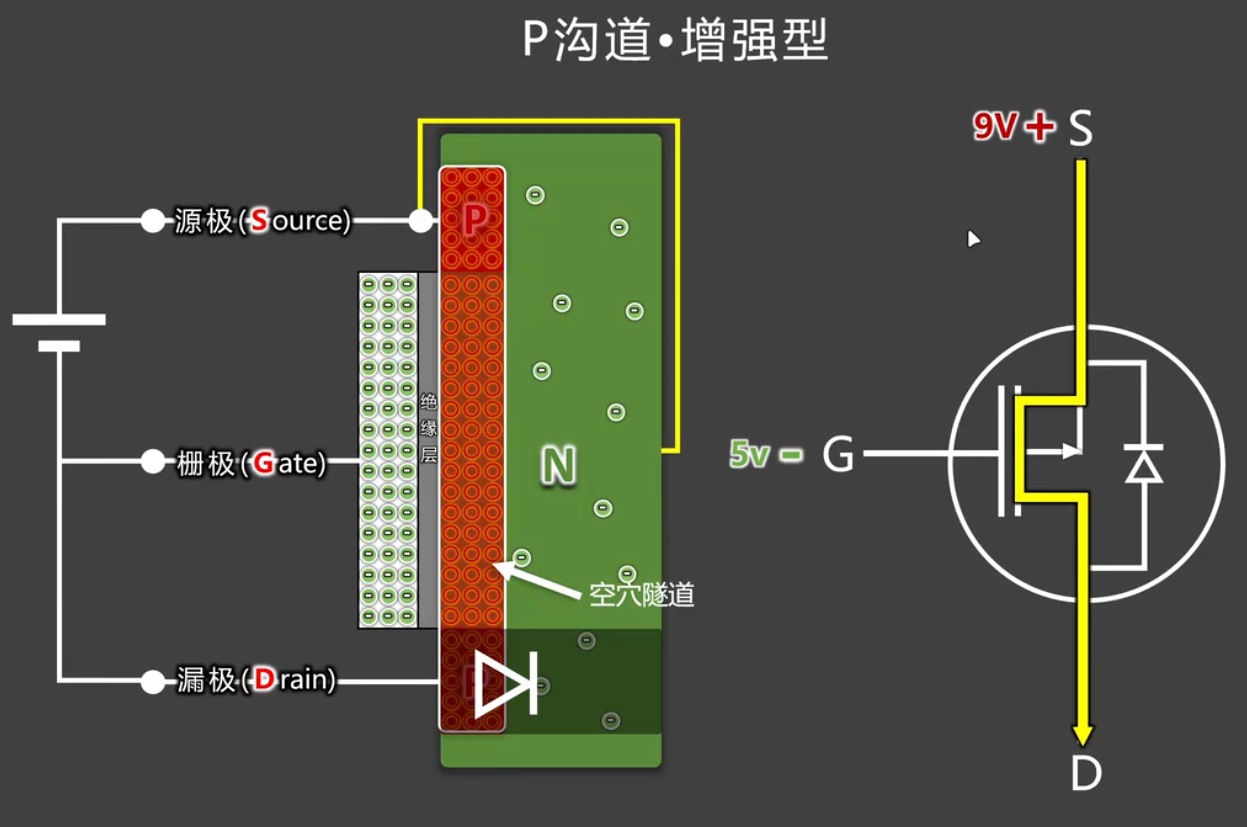

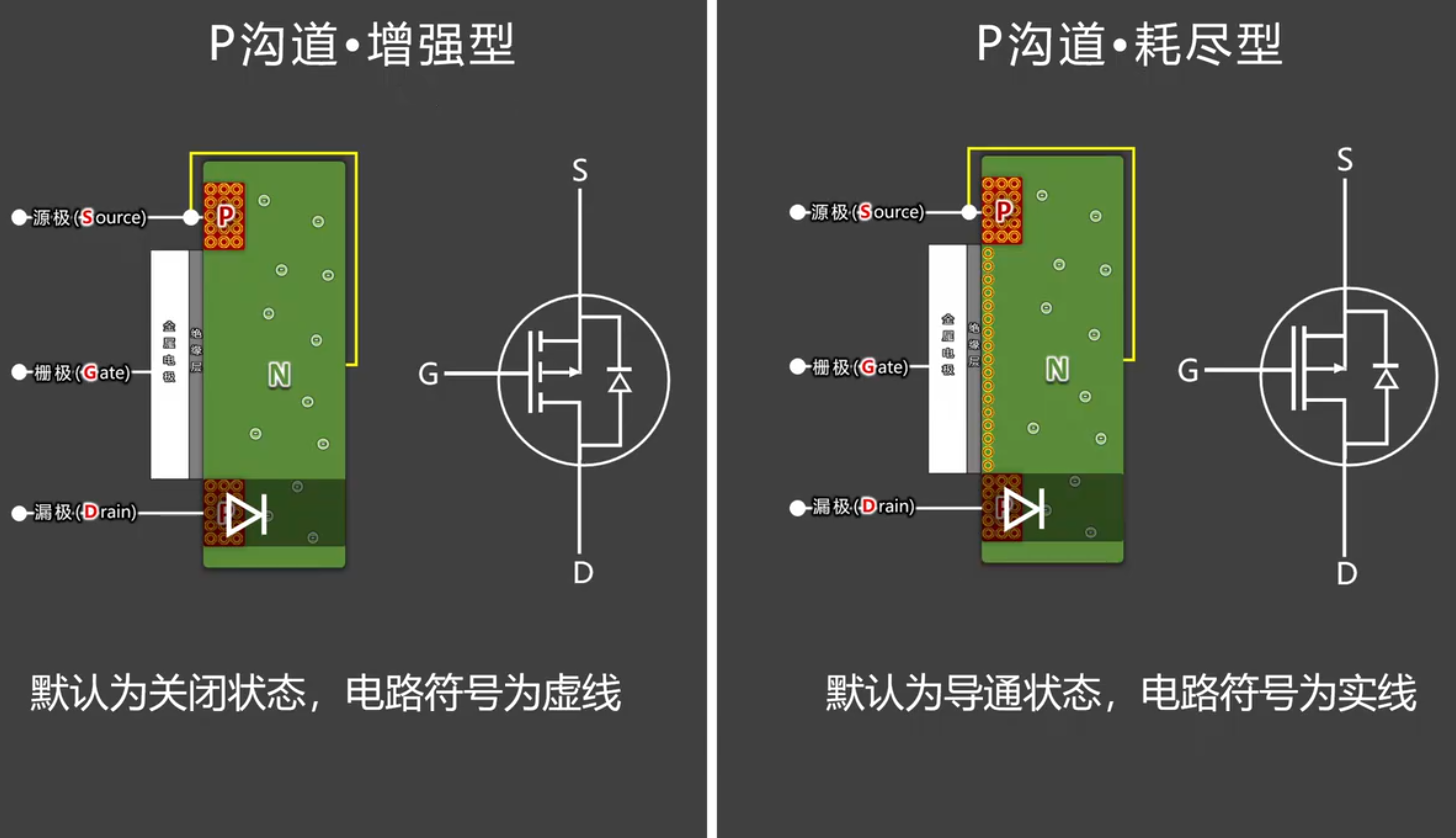

P沟道-增强型

P沟道 增强型和耗尽型区别

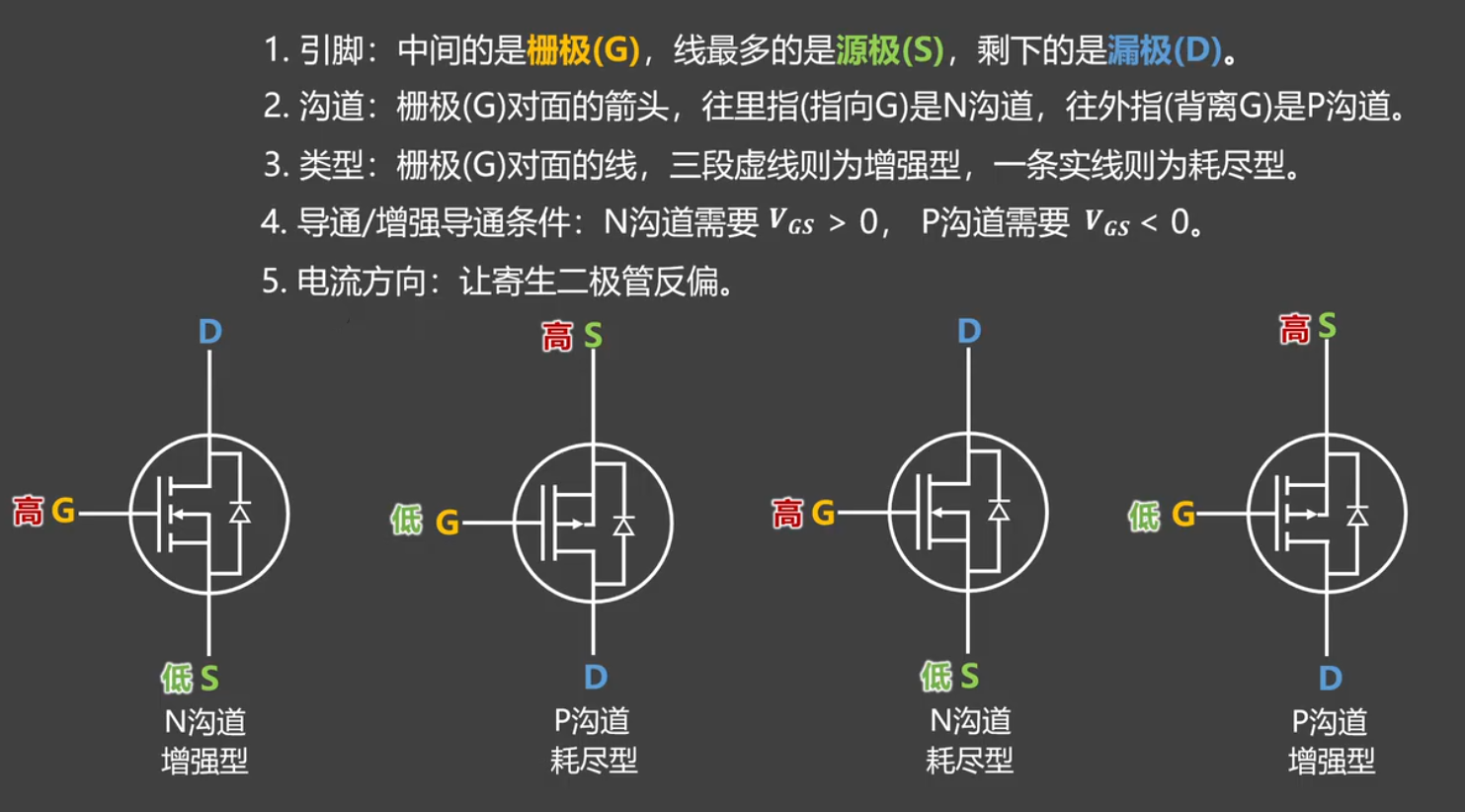

MOS管的快速判断

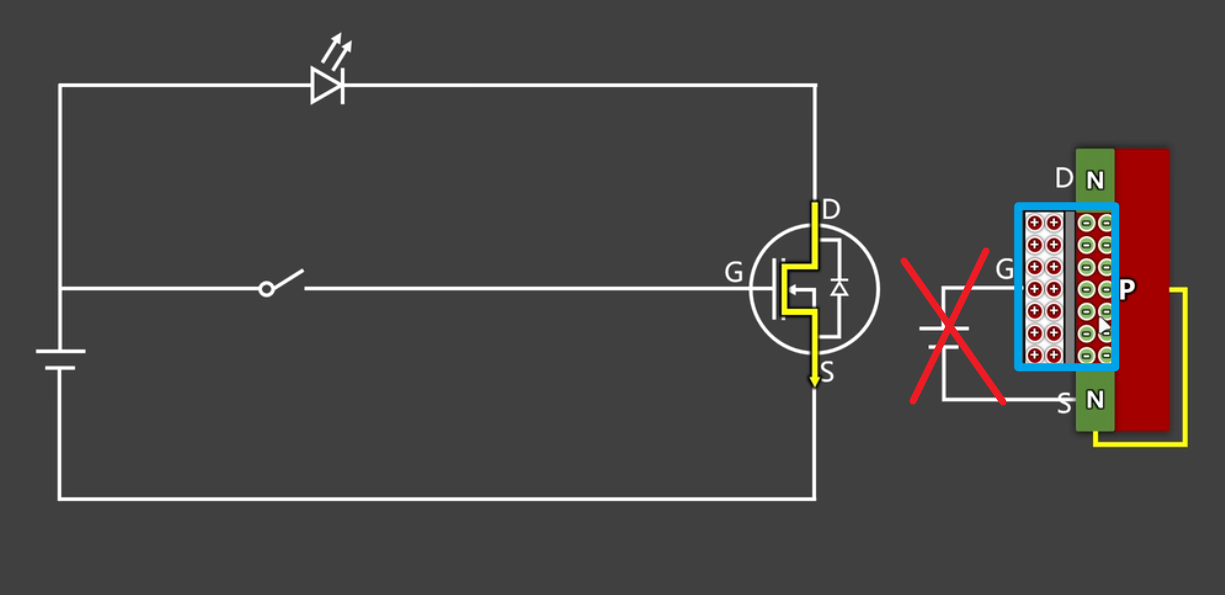

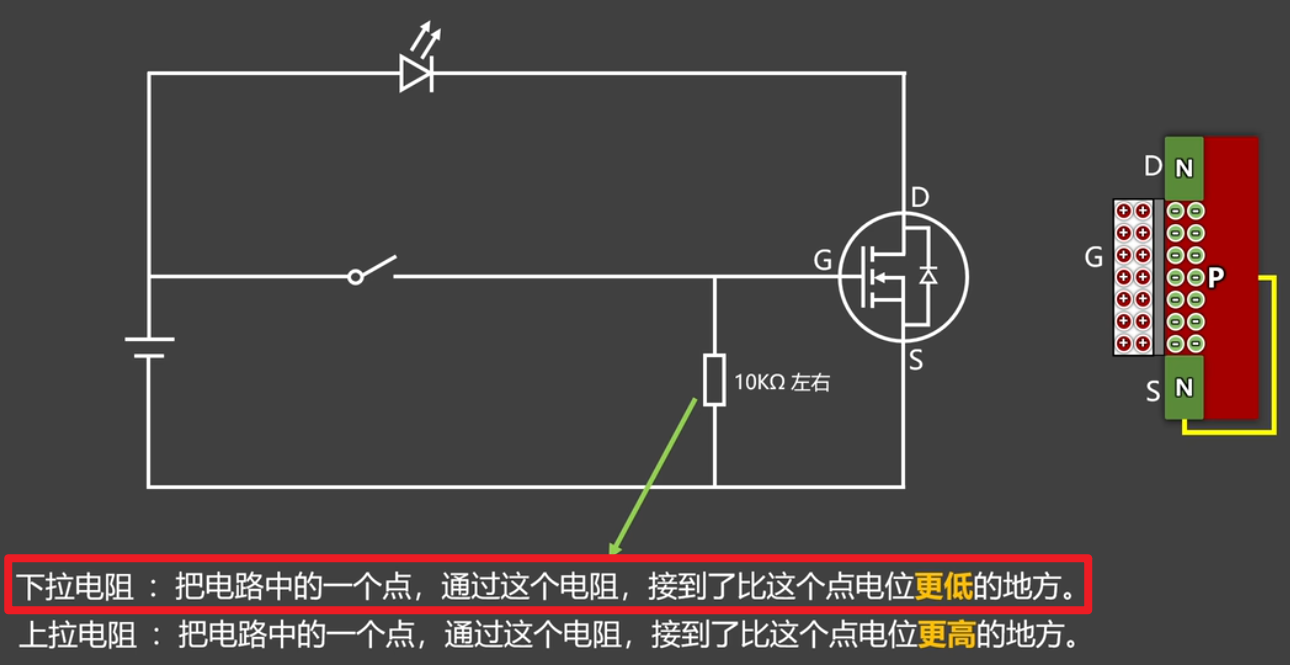

MOS管实操

电源关断之后,蓝框区域相当于一个电容,导致栅极正电一直保持无法释放,无法切断沟道的电子流动,需要增加下拉电阻

这种操作核心原理围绕MOS管栅极的“电容特性”和下拉电阻的“放电回路”作用展开,具体分析如下:

1. MOS管栅极的“电容本质”

MOS管的栅极(G)与源极(S)、漏极(D)之间是绝缘的氧化层(如SiO₂),这使得栅极与沟道之间形成了一个寄生电容(栅极电容)。当栅极施加正电压时,电容会存储电荷,从而在沟道中感应出可导电的电子(以N沟道增强型MOS为例),让漏极(D)和源极(S)之间形成导通的沟道。

2. 无下拉电阻时:电荷无法释放,MOS管持续导通

当电源关断、开关断开后,栅极电容中存储的正电荷没有放电回路(因为栅极与其他部分绝缘,电荷难以自然流失)。此时,栅极仍维持较高的正电位,会持续在沟道中感应电子,导致D-S之间的沟道保持导通状态,无法正常关断。

3. 增加下拉电阻后:提供放电回路,确保MOS管关断

下拉电阻(图中10kΩ左右的电阻)一端接栅极(G),另一端接电位更低的节点(通常是源极S或地)。这样,栅极电容中存储的正电荷就可以通过下拉电阻缓慢放电,使栅极电位逐渐降低到与源极(或地)相近的水平。当栅极电位低于MOS管的“开启电压”时,沟道中的感应电子消失,D-S之间的导通被切断,MOS管可靠关断。

补充:上拉/下拉电阻的共性逻辑

- 下拉电阻:将节点电位“拉向更低电位”,为电容等元件提供放电回路;

- 上拉电阻:将节点电位“拉向更高电位”,为电容等元件提供充电回路(或维持高电位)。

两者都是通过电阻的电流通路特性,解决“节点电位因电容/高阻抗而无法稳定控制”的问题。

三极管与MOS管的区别