sv时钟块中default input output以及@(cb)用法总结

在时钟块中,加入default input output可以自定义采样和驱动时间。

其中input是指时钟块在时钟沿后多久去采样输入,output是指多久去驱动

如果没有default,也是会有默认值的,input为1step,output为0。

clocking cb @(posedge clk);default input #1step output #1ps;output c;endclocking以代码为例,input #1step是指在时钟沿后1step去采样,output #1ps是指在1ps后驱动。

但事情并没有这么简单!

首先看如下代码示例:

interface tf(input clk);logic [3:0] a,b,c;clocking cb @(posedge clk);default input #1step output #1ps;input a;output c;endclockingendinterfacemodule test;bit clk = 0;tf t(clk);rd rd_test;initial beginforever begin#5ns;clk = ~clk;endendinitial begint.a = 0;t.b = 0;t.c = 0;repeat(5)@(posedge clk);t.a <= 1;repeat(5)@(posedge clk);t.a <= 0;repeat(5)@(posedge clk);repeat(5)@(posedge clk);repeat(5)@(posedge clk);$finish; endinitial beginforever begin@(posedge t.clk);if(t.a == 1)t.c <= 1;elset.c <= 0;endendinitial begin$fsdbDumpfile("tst.fsdb");$fsdbDumpvars(0,test);endendmodule

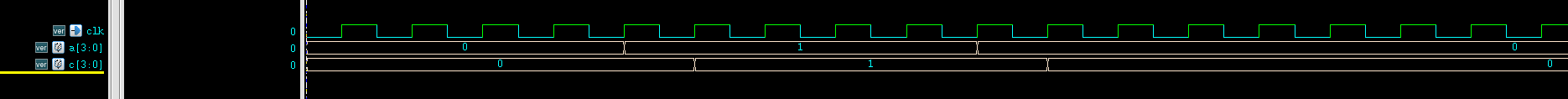

代码逻辑很简单,先把a驱动成1,过一会驱动成0,当采样到a为1后,再将c赋值为1,这里我们先不使用cb来驱动和采样,波形如下:

这里我们可以看到,在给a驱动1后,下一个clk才能采样到a为1,然后c才会被驱动成1。

如果换成cb,情况和前面是一样的。

initial beginforever begin@(t.cb);if(t.cb.a == 1)t.cb.c <= 1;elset.cb.c <= 0;endend如果a信号没有放在cb里,直接用vif驱动呢?

interface tf(input clk);logic [3:0] a,b,c;clocking cb @(posedge clk);default input #1step output #1ps;output c;endclockingendinterfacemodule test;bit clk = 0;tf t(clk);rd rd_test;initial beginforever begin#5ns;clk = ~clk;endendinitial begint.a = 0;t.b = 0;t.c = 0;repeat(5)@(posedge clk);t.a <= 1;repeat(5)@(posedge clk);t.a <= 0;repeat(5)@(posedge clk);repeat(5)@(posedge clk);repeat(5)@(posedge clk);$finish; endinitial beginforever begin@(t.cb);if(t.a == 1)t.cb.c <= 1;elset.cb.c <= 0;endendinitial begin$fsdbDumpfile("tst.fsdb");$fsdbDumpvars(0,test);endendmodule

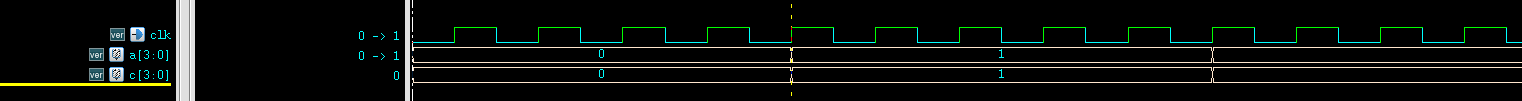

可以看到,这里a和c在同一个时钟沿后变化了,但c因为cb还是落后了时钟沿1ps。

为什么会这样?大家可能会以为@(posedge t.clk)和@(t.cb)实现的效果是一样的,都是等一个clk,但实际结果并不是。

因为在@(t.cb)后,就以cb的default进行采样了,而不是clk进行采样。这里在@(t.cb)后,会在时钟沿后1step进行采样,但此时a已经被驱动为1了,所以就采样到了a为1的情况,就将c赋值为1了,所以就得到了a和c在同一个周期被赋值为1的情况。

如果将@(t.cb)改成@(posedge t.clk),那么对a的采样就是0,因为此时还没对a进行赋值,所以c就在下一个clk才知道a为1,就是c落后a一个clk的情况。

如果在@(t.cb)的情况下,将a的赋值delay 1ps,也是c落后a的情况,因为cb的采样在时钟沿后1step,a的赋值在时钟沿后1ps,采样到的值是0。