ARM架构详解:从内核到异常处理

1.CPU架构

CISC:复杂指令集架构;

RISC:精简指令集架构;

ARM属于(RISC)精简指令集架构

2.ARM内核的组成

ISA(指令集架构):定义了CPU能执行的全部指令;

ALU(算数逻辑单元):执行算术运算和逻辑运算的核心单元;

MMU:内存管理单元,用于映射物理与虚拟内存,提高物理内存的使用率;

是否存在MMU是该内核是否适合移植操作系统的关键,存在,即适合移植操作系统,反之,不适合移植操作系统;

CACHE:高速缓存,可以提高程序运行的效率;

icache:指令,dcache: 数据;

一般使用时,打开icache,关闭dcache;

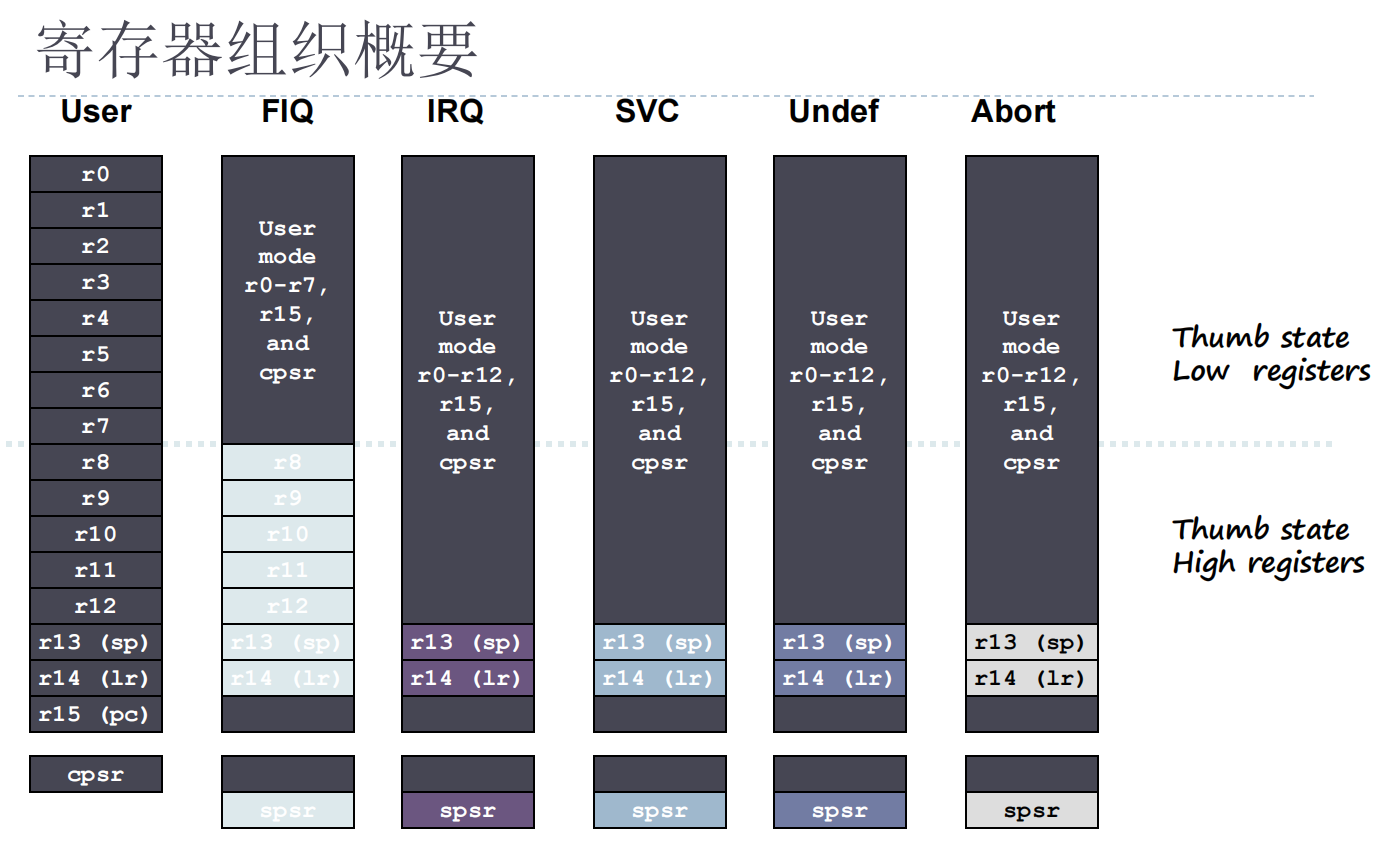

寄存器组:

通用寄存器:(R0 ~ R12)

几个特殊的寄存器:

R13(SP):栈指针寄存器;

R14(LR):链接寄存器,用于调用函数时,保存被调函数在主调函数中的返回地址;

R15(PC):程序指令寄存器,其指向正在执行的程序指令的下一条程序指令;

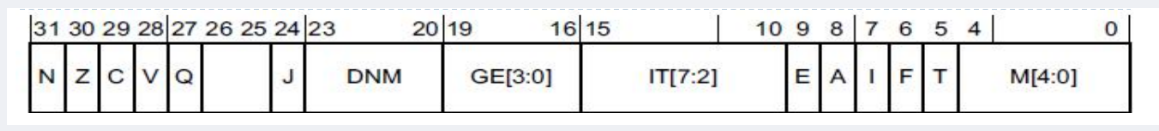

CPSR:当前程序状态寄存器;

SPSR:备份CPSR的寄存器;

3.ARM9与Cortex A的工作模式

(1)ARM9 的工作模式

ARM9 属于 ARMv4T / ARMv5TE 架构,支持 7 种工作模式(ARM 传统模式)。模式列表:

User (usr)普通用户模式,运行应用程序,权限最低。

FIQ (fiq)

快速中断模式,用于处理高速数据传输或通道处理,提供额外的寄存器以加速处理。

IRQ (irq)

普通中断模式,用于处理中断请求。

Supervisor (svc)

管理模式,操作系统内核常用,响应软件中断 (SWI)。

Abort (abt)

存储器异常模式,处理预取或数据访问异常。

Undefined (und)

未定义指令模式,处理非法或未实现的指令。

System (sys) (ARMv4T 之后新增)

特权模式,和 User 模式的寄存器相同,但拥有特权,常用于 OS 运行内核代码。

ARM9 工作模式总结:

用户态:User

特权态:FIQ, IRQ, SVC, ABT, UND, SYS

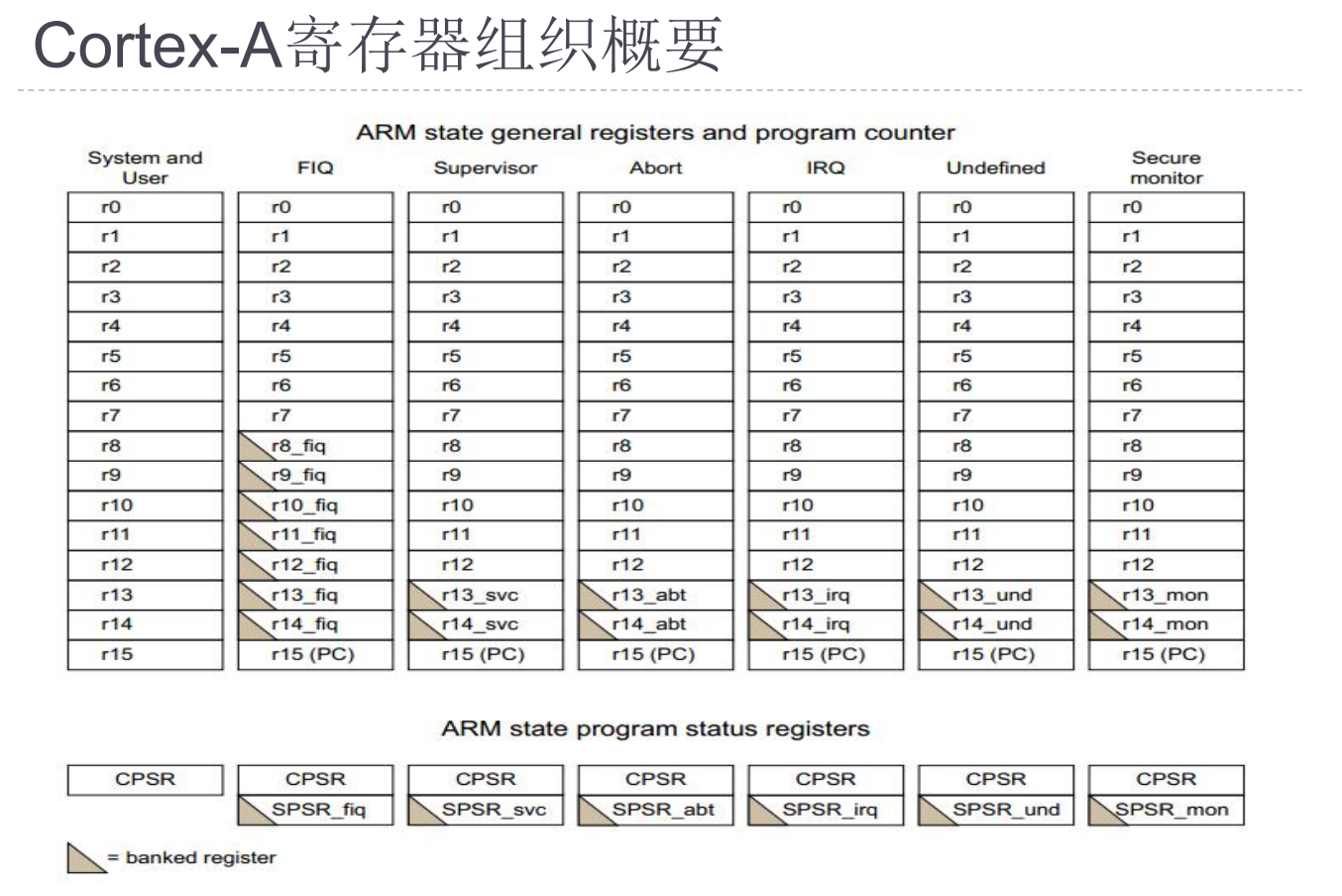

(2)ARM Cortex-A (ARMv7-A/ARMv8-A) 的工作模式

ARMv7-A

延续 ARM9 的模式,支持9 种模式:User (usr)

FIQ (fiq)

IRQ (irq)

Supervisor (svc)

Abort (abt)

Undefined (und)

System (sys)

Cortex-A特有模式(新增)

Monitor (mon) (新增)

用于 TrustZone 安全扩展,在 Normal World 与 Secure World 之间切换;

4.ARM9与Cortex A的寄存器区别

ARM9中有37个寄存器,Cortex A中有40个寄存器;

ARM9:

Cortex-A:

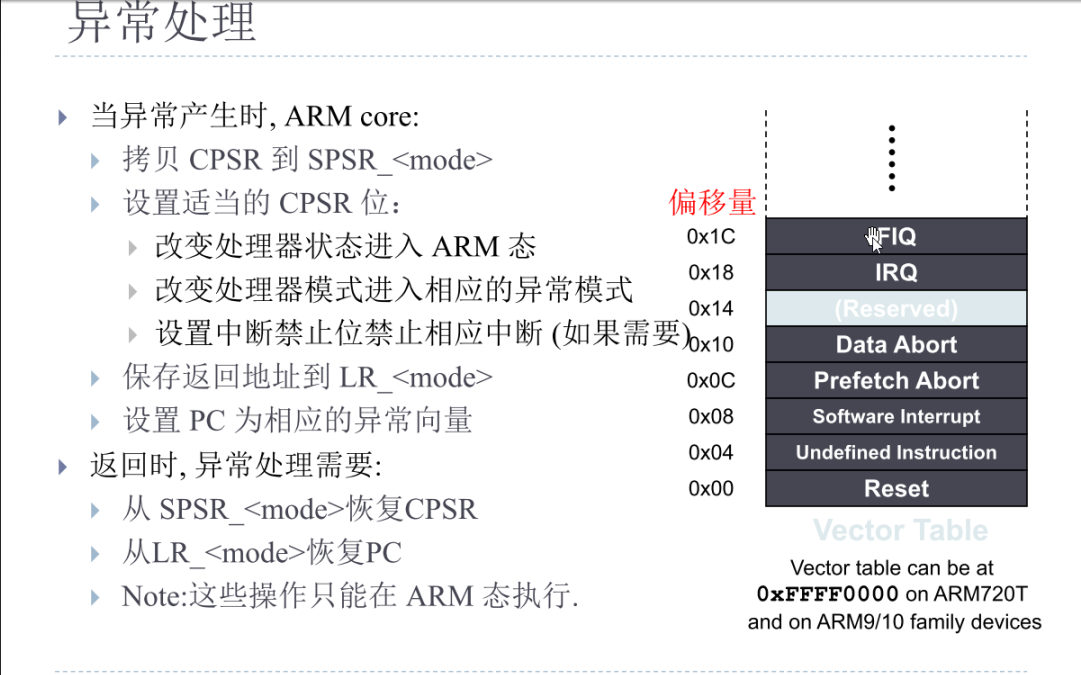

5.ARM 内核在异常(Exception)产生时的处理流程

(1)ARM 异常的基本概念

异常 (Exception):指令执行过程中发生的特殊事件,比如 中断、系统调用、内存访问错误、未定义指令 等。当异常发生时,CPU 会 自动切换模式、保存现场、跳转到异常向量入口,从而交给异常处理程序。

(2) ARM 发生异常时内核自动完成的工作

当异常产生时,ARM 内核硬件会执行以下步骤(以 AArch32/ARMv7-A 为例):模式切换 (Mode Switch)

处理器从当前模式切换到相应的异常模式(如 IRQ → irq 模式,FIQ → fiq 模式,SVC → svc 模式等)。

保存返回地址 (LR = Link Register)

把当前的 下一条指令地址(PC + 偏移)保存到该模式下的 LR(R14)中,作为异常返回时的依据。

偏移量与异常类型相关:

IRQ/FIQ:LR = PC + 4

SWI/未定义指令:LR = PC + 4

Prefetch Abort:LR = PC + 4

Data Abort:LR = PC + 8

保存程序状态寄存器 (SPSR)

将 CPSR (Current Program Status Register) 的内容保存到当前模式的 SPSR (Saved Program Status Register)。

包含条件码、中断使能标志、处理器模式等。

设置新的 CPSR

处理器模式切换到对应的异常模式。

中断屏蔽位可能被设置(如进入 IRQ/FIQ 时自动屏蔽后续同类中断)。

跳转到异常向量地址 (Vector Table)

根据异常类型,从 异常向量表中取出入口地址并跳转执行:

0x00:Reset

0x04:Undefined Instruction

0x08:Software Interrupt (SWI/SVC)

0x0C:Prefetch Abort

0x10:Data Abort

0x14:Reserved

0x18:IRQ

0x1C:FIQ

(3)异常处理程序的工作

硬件只做最小化的工作,剩下由 异常处理程序 (Exception Handler) 完成:保存现场(将通用寄存器 R0–R12 压栈)

根据异常类型执行相应的处理逻辑

恢复现场(出栈恢复寄存器)

从 LR/SPSR 中恢复程序执行(通过 SUBS PC, LR, #偏移 或 MOVS PC, LR 返回)

总结(ARM 内核在异常产生时自动完成的工作)

切换到对应的异常模式

保存返回地址到 LR_异常模式

将 CPSR 保存到 SPSR_异常模式

修改 CPSR(切换模式、屏蔽中断等)

跳转到异常向量表对应入口地址

6.异常向量表 (Exception Vector Table)

(1)定义

异常向量表是一张位于 固定内存地址 的小型跳转表(通常占用几十字节),它保存了各类 异常处理程序入口的地址(即异常处理程序的跳转语句)。

当 ARM 处理器发生异常时,硬件会自动跳转到对应的向量表入口地址,从而执行异常处理流程。(2)表项内容

每个表项对应一种异常,存放的不是“完整的处理代码”,而是一条跳转指令(通常是 LDR PC, [PC, #offset] 或 B handler),用来跳到真正的异常处理程序入口。典型 ARMv7-A (AArch32) 异常向量表布局:

偏移地址 异常类型 描述

0x00 Reset 上电或复位

0x04 Undefined Instruction 未定义指令

0x08 SWI (SVC) 软件中断(系统调用)

0x0C Prefetch Abort 取指异常

0x10 Data Abort 数据访问异常

0x14 Reserved 保留

0x18 IRQ 普通中断

0x1C FIQ 快速中断

每个表项通常只有 4 字节(一条 ARM 指令),所以整个表大小一般是 32 字节。(3)作用

将不同类型的异常映射到对应的处理程序实现异常处理的快速入口,减少硬件开销

保证异常响应的统一性(固定入口 → 软件分发)

总结

异常向量表 = 异常类型 → 异常处理入口 的映射表

包含 Reset、IRQ、FIQ、SVC、Abort 等入口

大小一般是 8 个表项 × 4 字节 = 32 字节