FPGA设计杂谈之七:异步复位为何是Recovery/Removal分析?

目录

一、复位

1.1 复位的定义

1.2 复位的作用

二、同步复位与异步复位

2.1 复位示例

2.2 同步复位优劣

2.3 异步复位优劣

三、异步复位与Recovery/Removal

3.1 Recovery/Removal

3.2 Recovery/Removal违例的影响

3.3 异步复位同步释放

一、复位

Recovery/Removal的定义如下

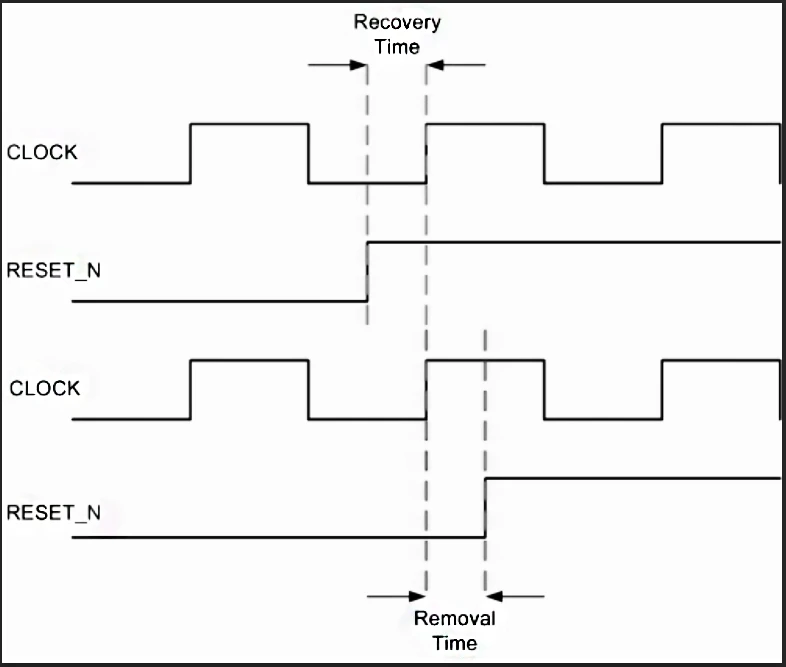

Recovery(恢复时间):异步复位信号释放后,恢复到非复位状态的电平必须在时钟有效沿来临前保持的最小时间,该段时间为recovery time(恢复时间)

Removal(移除时间):异步复位信号在时钟有效沿来临之后,复位信号还需要保持有效状态的最小时间,该段时间为removal time(去除时间)

定义与setup/hold分析类似,检查与时钟信号延时的关系,但为何不用setup/hold来分析呢?定义中都提到了异步复位,先来看看什么是复位。

1.1 复位的定义

复位(Reset)是一种特殊的控制信号,用于将寄存器、触发器、状态机等数字逻辑电路强制回到一个已知的初始状态,复位根据是否依赖时钟可分为同步复位和异步复位。

1.2 复位的作用

a)上电初始化

在FPGA上电时,内部寄存器/存储器处于未知状态(亚稳态或无效电平),使用复位信号强制所有逻辑单元(触发器、状态机、计数器等)进入到确定状态(如全0或初始值)。从而避免系统因初始状态混乱导致逻辑错误(例如状态机卡死、计数器溢出等)。

b)强制退出异常状态

FPGA运行中可能因外部干扰(电磁噪声)、时序违例(Setup/Hold失败)、设计缺陷等进入未定义状态(如死锁、跑飞)。使用复位信号作为“紧急制动器”,无条件重置系统到安全状态。例如看门狗超时复位、通信协议超时重同步、故障保护机制。

c)可控系统重启

对于动态重配置FPGA模块、切换工作模式(如从待机模式唤醒),使用局部复位(Partial Reset)仅重置特定模块,而非整个芯片。从而减少重启延迟,保留其他模块运行状态(如继续处理数据流)。

d)同步多模块协同

在复杂系统中多个模块需同时启动(如多通道ADC采集、并行处理器核)是,全局复位信号确保所有模块从同一初始时刻开始工作。例如图像处理流水线中,复位使能后所有像素缓冲区同时清零。

e)测试与调试

在测试与调试流程中,使用复位使系统回到已知状态,便于重复验证特定功能(如仿真测试向量),并且可通过触发复位强制重现错误场景,定位逻辑问题。

二、同步复位与异步复位

前面提到复位分为同步复位和异步复位,下面分析以两种复位的Verilog代码查看对应的时序报告

2.1 复位示例

以下图同步复位和异步复位的触发器为例

module reset(clk,d,asyn_rst,syn_rst,q0,q1);

input clk,d,asyn_rst,syn_rst;

output reg q0,q1;

//异步复位

always @(posedge clk or posedge asyn_rst) beginif (asyn_rst)q0 <= 0;elseq0 <= d;

end

//同步复位

always @(posedge clk) beginif (syn_rst)q1 <= 0;elseq1 <= d;

end

endmodule时钟约束

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk]

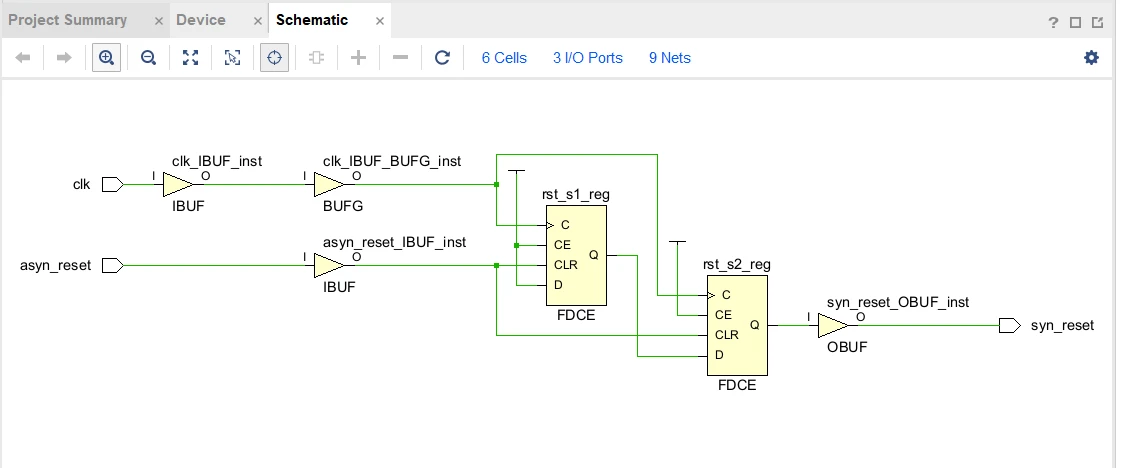

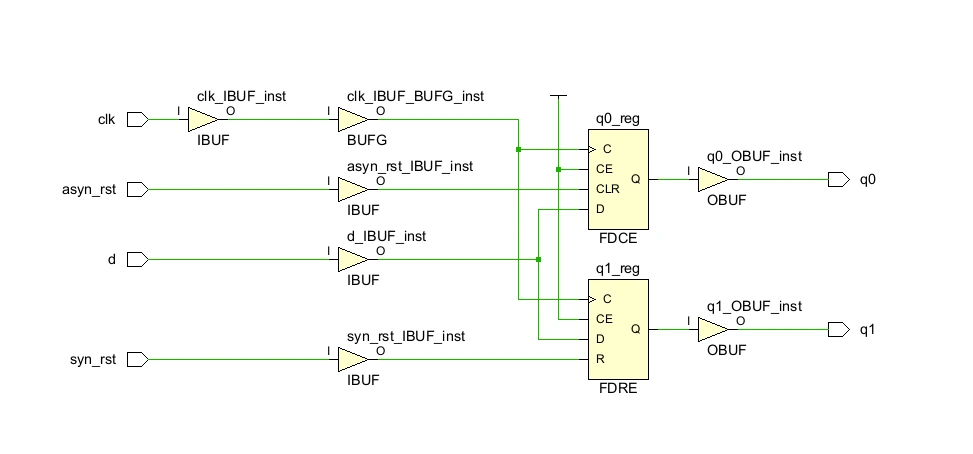

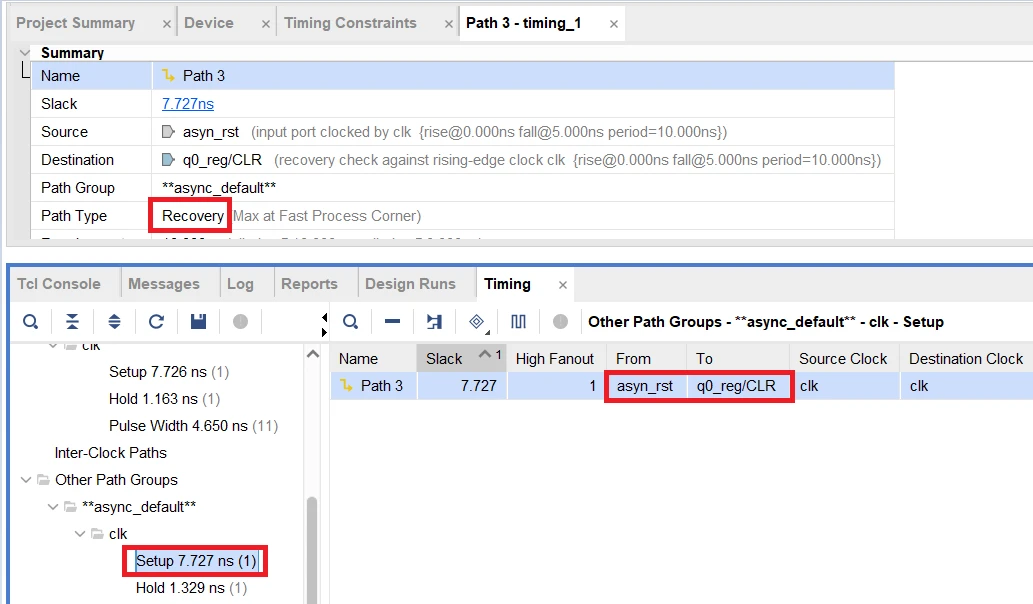

set_input_delay -clock [get_clocks -regexp .*] 2.000 [get_ports {asyn_rst syn_rst}]网表连接图中asyn_rst连接的是异步复位FDCE的CLR,syn_rst连接的是同步复位FDRE的R端口,即异步复位是由专门的寄存器实现

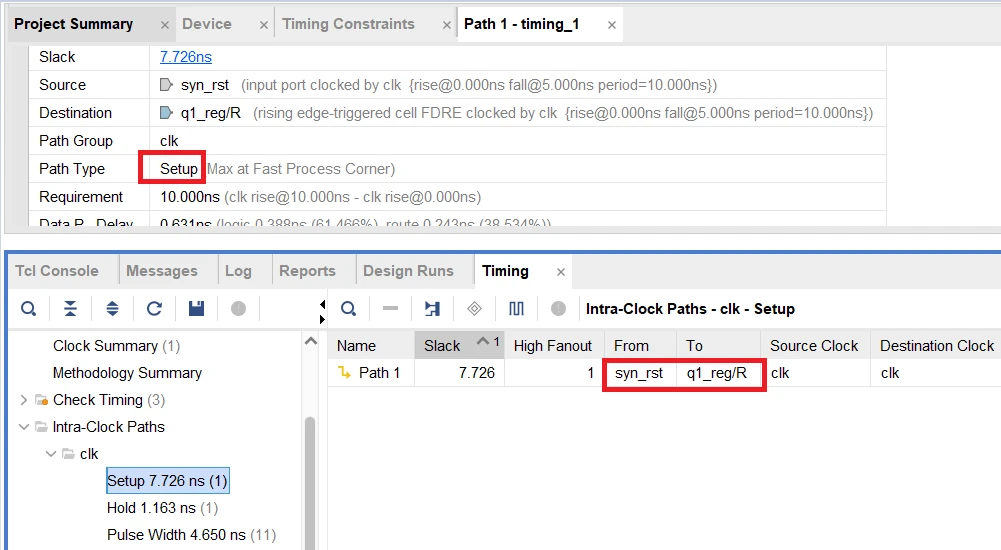

时序报告中,可以看到对于同步复位的寄存器q1_reg中sys_rst端口与时钟clk的分析为setup,即同步复位分析和普通数据D与时钟clk的分析类型相同

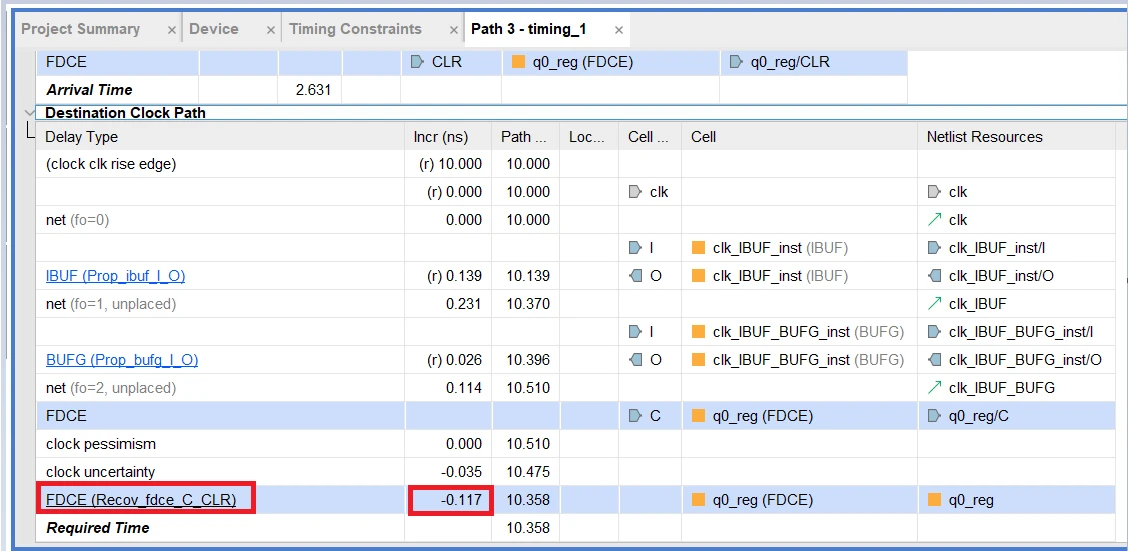

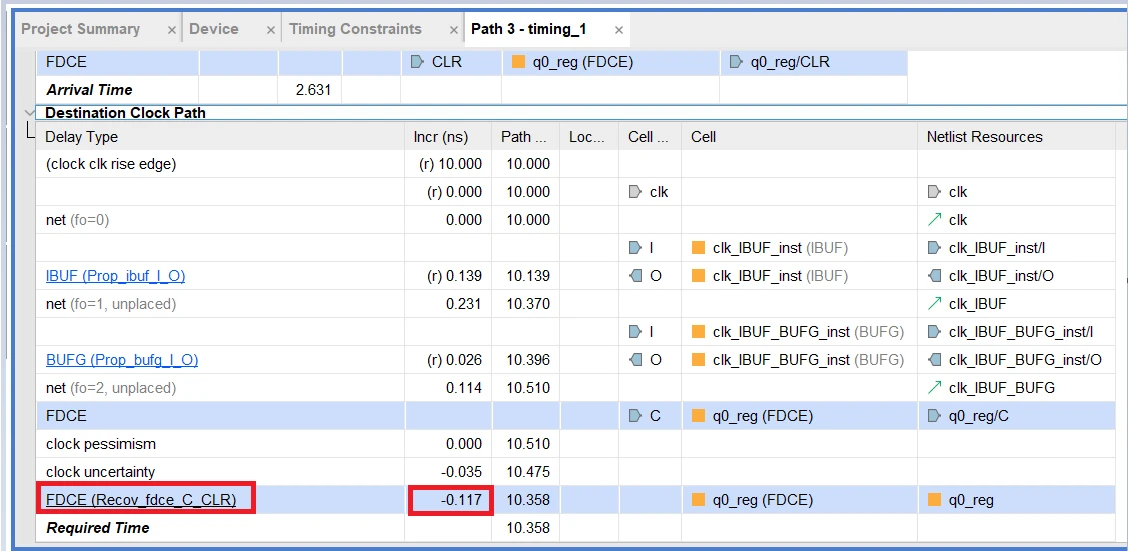

在Destination Clock Path中的FDCE(Recov_fdce_c_clr)的Incr时间即为寄存器自身要求的recovery时间,

对于同步复位的寄存器q0_reg中asys_rst端口与时钟clk的分析为recovery

2.2 同步复位优劣

优点

时序安全性高:复位信号和时钟同时作用,不会出现recovery/removal的问题。

易于STA分析:直接作为普通信号参与setup/hold分析。

行为更确定:复位只在时钟沿触发,避免复位信号毛刺导致的意外复位。

缺点

需要时钟才能复位:上电时钟不稳定或未启动时,无法保证逻辑立即进入安全状态。

逻辑资源开销可能更大:由于同步复位通过组合逻辑实现(不是直接用触发器的复位引脚),可能导致LUT资源和延时增加。

复位扇出大时收敛困难:大量寄存器的同步复位信号可能形成一条长的关键路径,影响时序。

2.3 异步复位优劣

优点

a)响应速度快:不依赖时钟,在任意时刻触发即可立即清零寄存器。

b)上电初始化方便:在时钟尚未稳定或系统时钟还没起来时,异步复位可以直接初始化逻辑。

c)大部分FPGA原语原生支持:FPGA的DFF基本都有async clear/preset端口,硬件代价低。

缺点

释放复位时有时序风险:异步复位释放需满足 recovery/removal 时序约束,否则容易导致亚稳态,需要设计“同步释放”电路来防止不确定行为。

时序分析复杂:STA(静态时序分析)工具需要单独分析异步路径,增加设计和调试复杂度。

跨时钟域时风险更高:在多时钟系统中,异步复位必须在每个时钟域同步释放。

三、异步复位与Recovery/Removal

在第二小节中,会发现对于异步复位的寄存器FDCE,其recovery分析依旧考虑clk,下图FDCE(Recov_fdce_C_CLR)的incr时间即为复位信号与时间的检查,和异步复位不依赖于时钟信号矛盾?

3.1 Recovery/Removal

原因是异步复位真正的流程包含了"复位-保持-撤销"三个阶段,"异步"仅指复位,当复位信号拉低时,可以不考虑时钟信号立即实现复位。但复位撤销的时刻,如果撤销时时钟边沿刚好来临,寄存器就会处于既要保持复位状态,又要采样新数据的冲突情况。因此,recovery和removal都是针对复位撤销时与时钟关系的分析进行的,关系如下图

3.2 Recovery/Removal违例的影响

如果工程出现recovery/removal违例时,会出现亚稳态,触发器会进入一种奇怪的、未定义的状态。或者输出中意外的转换会导致不可靠的结果,出现功能问题。

3.3 异步复位同步释放

为了降低recovery/removal违例的风险,通常异步复位同步释放的方式

module asyn_reset_ayn_release(clk,asyn_reset,syn_reset);

input clk;

input asyn_reset;

output syn_reset;

reg rst_s1;

reg rst_s2;

always @( posedge clk ,negedge asyn_reset)

begin

if(!asyn_reset)

begin

rst_s1<=1'b0;

rst_s2<=1'b0;

end

else

begin

rst_s1<=1'b1;

rst_s2<=rst_s1;

end

end

assign syn_reset=rst_s2;

endmodulea)当异步复位(asyn_reset=1)无效,即为高电平时,同步后的复位信号 syn_reset 也为高电平;

b)当异步复位(asyn_reset=0)有效时,同步后的复位信号立刻为低电平0,即实现了“异步复位”;

c)信号释放时,会在时钟上升沿来临时,才可以恢复为高电平1,实现“同步释放”;

网表连接图如下