ODDR双边沿数据输出

ODDR双边沿数据输出

一、说明

1.oddr是xilinx fpga底层原语,其作用是将内部单沿信号转为双沿信号输出到外部设备

2.实现时钟减半,数据速率保持不变的功能

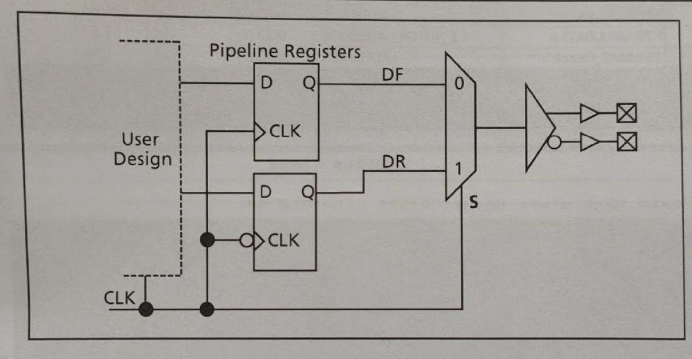

3.oddr是使用ologic模块实现的,底层使用FF触发器+MUX选择器

4.核心功能是SDR和DDR转换

5.opposite_edge模式:时钟的上升沿采集D1,时钟的下降沿采样D2

6.SAME_EDGE:在时钟的同一个边沿采集D1和D2

7.INIT:输出Q的初始值(0或1)。

8.SRTYPE:置位/复位类型(同步或异步)。

9.CE:时钟使能信号(高电平有效)

10.ODDR复位需要120ns左右,复位的时候需要注意

二、S/R置位/复位引脚,高电平有效

1.set和reset不能同时使用

IDDR #(

.DDR_CLK_EDGE ("OPPOSITE_EDGE" ), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1 (1'b0 ), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2 (1'b0 ), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_ctrl (

.Q1 (data_en ), // 1-bit output for positive edge of clock

.Q2 (data_err ), // 1-bit output for negative edge of clock

.C (rx_clk ), // 1-bit clock input

.CE (1'b1 ), // 1-bit clock enable input

.D (rx_ctrl ), // 1-bit DDR data input

.R (~rst_n ), // 1-bit reset

.S (1'b0 ) // 1-bit set

);

参考:https://blog.csdn.net/dimples_Song/article/details/79442409

三、ODDR模拟模型

module oddr_model #(

parameter DDR_CLK_EDGE = "OPPOSITE_EDGE", // 模拟模式参数

parameter INIT = 1'b0, // 初始值

parameter SRTYPE = "SYNC" // 复位类型,本例只做简单同步

)(

output reg Q,

input C,

input CE,

input D1,

input D2,

input R,

input S

);

reg d1_reg, d2_reg;

// 上升沿触发的触发器,捕获D1

always @(posedge C) begin

if (R) begin

d1_reg <= 1‘b0;

end else if (S) begin

d1_reg <= 1’b1;

end else if (CE) begin

d1_reg <= D1;

end

end

// 下降沿触发的触发器,捕获D2

always @(negedge C) begin

if (R) begin

d2_reg <= 1‘b0;

end else if (S) begin

d2_reg <= 1’b1;

end else if (CE) begin

d2_reg <= D2;

end

end

// 用时钟选择要输出的数据

// 注意:实际硬件中这个MUX的切换速度极快,这里只是行为模拟

always @(*) begin

if (C) begin

Q = d1_reg; // 时钟高电平时,输出上升沿采样的D1

end else begin

Q = d2_reg; // 时钟低电平时,输出下降沿采样的D2

end

end

endmodule