5.驱动led灯

1. 工程建立

1.1. 工程组织方式

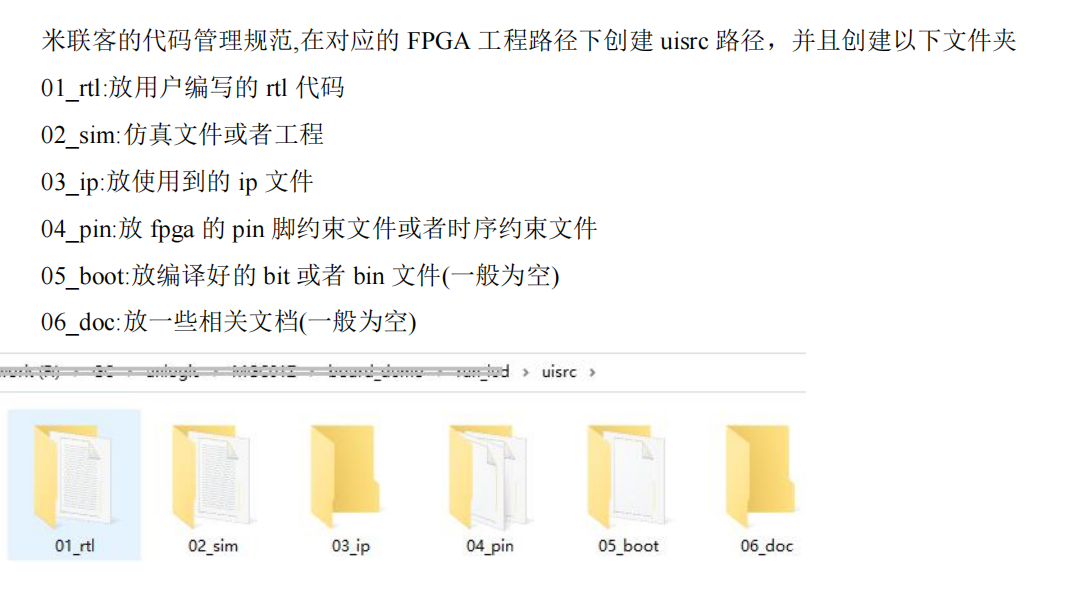

比较喜欢米联客的工程组织:

1.2. 新建FPGA工程

具体内容:略

1.3. 硬件约束文件

具体内容:略

1.4. RTL仿真方法

具体内容:略

1.5. 程序下载

具体内容:略

2. 代码设计

首先就是一个led.v的设计文件:

`timescale 1ns / 1ns

编译指令,它对仿真过程中的时间表示和延迟计算有重要影响

timescale 1ns / 1ns 表示:

- 模块内的时间单位为 1 纳秒。

- 时间精度为 1 纳秒(即小于 1ns 的时间值会被舍入)。

模块定义

寄存及定义

always begin end模块

例化

`timescale 1ns / 1nsmodule run_led#(parameter T_INR_CNT_SET = 32'd99_999_999 //分频时钟计数,初始时钟过快,人眼观察会导致LED常亮) //设置分频系数,降低流水灯的变化速度( //该参数可以由上层调用时修改input I_sysclk, //系统时钟信号input I_rstn, //全局复位output [3:0] O_led //LED灯输出);reg [3:0] led_r; //设置一个LED的寄存器,用来存储LED信号状态reg[32:0] t_cnt;assign O_led = led_r; //将寄存器内信号输出//计数模块//时钟的上升沿,和复位拉低时触发此逻辑always @(posedge I_sysclk or negedge I_rstn)beginif(I_rstn==1'b0) //系统复位t_cnt <= 0;else if(t_cnt == T_INR_CNT_SET) //计数t_cnt达到目标时清零t_cnt <= 0;elset_cnt <= t_cnt + 1'b1; //否则计数+1end//流水灯状态切换always @(posedge I_sysclk or negedge I_rstn)begin //系统时钟的上升沿触发以及复位的下降沿触发if(I_rstn==1'b0)led_r <= 4'b0111; //设置LED 寄存器的初始状态,0表示灯亮,1表示灯灭else if( t_cnt == 0) //当计数器计数达到预定值被清零时led_r <= {led_r[0],led_r[3:1]}; //LED寄存器将最低为左移至最高位,通过{}来完成数据的拼接end//ila例化//抓计数信号和LED输出信号特征ila_led led_test (.clk(I_sysclk), // input wire clk.probe0(I_rstn), // input wire [0:0] probe0 .probe1(t_cnt), // input wire [0:0] probe1 .probe2(O_led) // input wire [3:0] probe2);

endmodule 在RTL仿真时,需要设计testbench文件,用于模拟输入激励,以便于模拟仿真,因为在RTL仿真时,是没有真实的输入输出的。

`timescale 1ns / 1nsmodule tb_run_led();reg I_sysclk,I_rstn; //时钟信号以及复位信号

wire [3:0] O_led; //仿真的LED 信号run_led#

(

.T_INR_CNT_SET(1000) //设置一个较小的时钟计数参数,可以大大缩小我们仿真需要的时间

)

run_led_inst(.I_sysclk(I_sysclk), //例化时钟接口.I_rstn(I_rstn), //例化复位接口.O_led(O_led) //例化led接口

);initial beginI_sysclk <= 1'b0; //时钟信号的寄存器设置初值I_rstn <= 1'b0; //复位信号的寄存器设置初值#100; //延时100个时间单位I_rstn <= 1'b1; //复位恢复高点平,模拟复位完成

endalways #5 I_sysclk=~I_sysclk; //每过5个时钟周期,模拟的系统时钟信号进行一次翻转endmodule