STM32 F103外部晶振8MHz改为12MHz,如何配置?

STM32 F103外部晶振8MHz改为12MHz,如何配置?

KEIL中STM32F103的外部晶振默认是8MHz,如果在开发中,外部晶振被修改成其它值,如何修改呢?

假设外部晶振从8MHz修改为12MHz,但主频仍保持72MHz。配置外部晶振的详细步骤如下:

1、修改外部晶振频率

打开stm32f10x.h,找到下面的语句:

#if !defined HSE_VALUE

#ifdef STM32F10X_CL

#define HSE_VALUE ((uint32_t)25000000) /*!< Value of the External oscillator in Hz */

#else

#define HSE_VALUE ((uint32_t)8000000) /*!< Value of the External oscillator in Hz */

#endif /* STM32F10X_CL */

#endif /* HSE_VALUE */

修改如下:

#if !defined HSE_VALUE

#ifdef STM32F10X_CL

#define HSE_VALUE ((uint32_t)25000000) /*!< Value of the External oscillator in Hz */

#else

#define HSE_VALUE ((uint32_t)12000000) /*!< Value of the External oscillator in Hz */

#endif /* STM32F10X_CL */

#endif /* HSE_VALUE */

2、设置主频

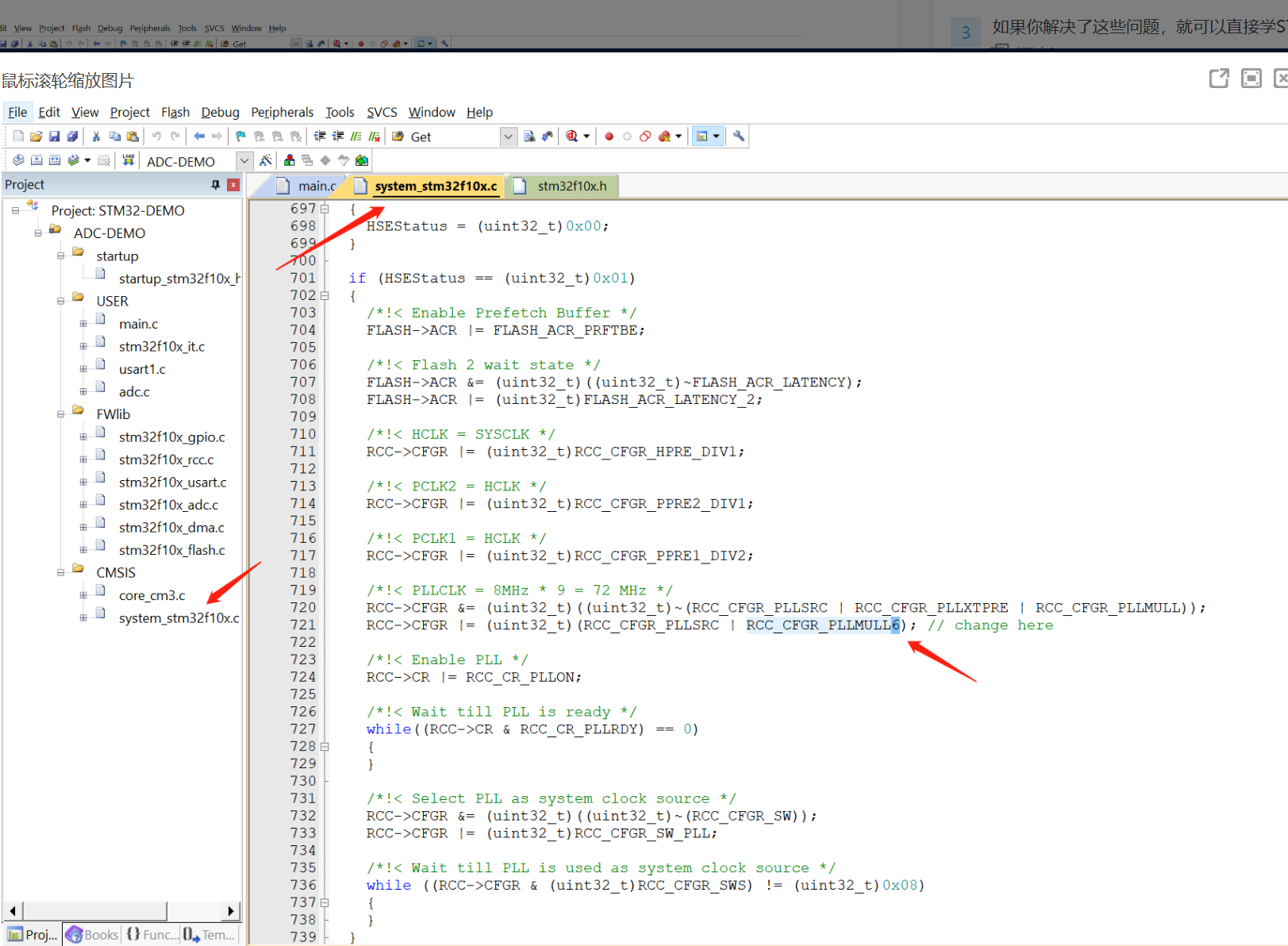

打开system_stm32f10x.c,找到下面的语句:

/* PLL configuration: PLLCLK = HSE * 9 = 72 MHz,2025年11月8日修改 */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

修改如下:

/* PLL configuration: PLLCLK = HSE * 6 = 72 MHz,2025年11月8日修改 */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL6);

3、配置系统时钟

//HSE_SetSysClock(RCC_PLLMul_6); // 设置系统时钟为12MHz * 6 = 72MHz

void HSE_SetSysClock(uint32_t RCC_PLLMul_x)

{

__IO uint32_t StartUpCounter = 0, HSEStartUpStatus = 0;

RCC_DeInit();//把RCC寄存器复位成复位值

RCC_HSEConfig(RCC_HSE_ON);//使能HSE

HSEStartUpStatus = RCC_WaitForHSEStartUp();

//等待HSE启动,Waits for HSE start-up

if (HSEStartUpStatus == SUCCESS)//HSE启动成功

{

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);//使能预取指

FLASH_SetLatency(FLASH_Latency_2);

RCC_HCLKConfig(RCC_SYSCLK_Div1);

RCC_PCLK1Config(RCC_HCLK_Div2);

RCC_PCLK2Config(RCC_HCLK_Div1);

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_x);

// 配置 PLLCLK = HSE * RCC_PLLMul_x

RCC_PLLCmd(ENABLE);//使能PLL

while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)

{//等待PLL稳定

}

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);//选择系统时钟

while (RCC_GetSYSCLKSource() != 0x08)

{

}

}

else

{/* 如果HSE 启动失败,用户可以在这里添加处理错误的代码 */

while (1)

{

}

}

}

4、调用示例:

#include "stm32f10x.h"

//使能uint8_t,uint16_t,uint32_t,uint64_t,int8_t,int16_t,int32_t,int64_t

#include "delay.h"

#include "USART1.h"

#include "IWDG.h"

//PLL配置: PLLCLK = HSE * 6 = 72 MHz,2025年11月8日修改

const char CPU_Reset_REG[]="\r\nCPU reset!\r\n";

int main(void)

{

HSE_SetSysClock(RCC_PLLMul_6); // 设置系统时钟为12MHz * 6 = 72MHz

NVIC_PriorityGroupConfig(NVIC_PriorityGroup_4);//设置系统中断优先级分组4

USART1_Serial_Interface_Enable(115200);

delay_ms(1000);

while(1)

{

}

}