SPI NOR Flash 家族的常见存储结构

什么是SPINOR?

SPI NOR 是一种非易失性存储器(断电后数据不丢失),名称由两部分组成:SPI 接口和NOR 存储类型,两者结合决定了它的通信方式和存储特性。

1. 拆解术语:SPI + NOR

SPI(Serial Peripheral Interface):即 “串行外设接口”,是一种简单的同步串行通信协议。它通过少数几根线(通常 4 根:时钟线 SCK、主机输出 / 从机输入 MOSI、主机输入 / 从机输出 MISO、片选线 CS)实现芯片之间的通信,结构简单、成本低,适合中小速率的数据传输(常见速率 50MHz~200MHz)。

NOR(NOR Flash):是 Flash 存储器的两大主流类型之一(另一类是 NAND Flash)。NOR Flash 的核心特点是支持 “随机读取”(像内存一样按字节 / 字地址直接访问),且能直接被 CPU 读取并执行程序(称为 “XIP,eXecute In Place”),因此非常适合存储程序代码(如固件、启动程序)。

2. SPI NOR 的本质:用 SPI 接口通信的 NOR Flash

简单说,SPI NOR 就是 “通过 SPI 协议传输数据的 NOR 型 Flash 存储器”。

它继承了两者的优势:

- 继承 SPI 的 “接口简单”:只需 4 根线即可与 MCU(微控制器)连接,硬件设计难度低,适合嵌入式设备的小型化需求。

- 继承 NOR 的 “代码执行能力”:存储的程序可直接被 CPU 调用执行,无需先加载到 RAM,节省系统资源。

3. 关键特性与应用场景

- 容量:中小容量为主(通常 1MB~512MB),远小于 NAND Flash(常见 GB 级)。

- 速度:读取速度较快(支持 XIP),但写入 / 擦除速度较慢(擦除需按扇区 / 块操作)。

- 典型应用:

- 嵌入式设备的启动程序(如路由器、智能手表的 Bootloader);

- 固件存储(如传感器、物联网模组的配置程序);

- 小型系统的代码存储(如 MCU 的应用程序)。

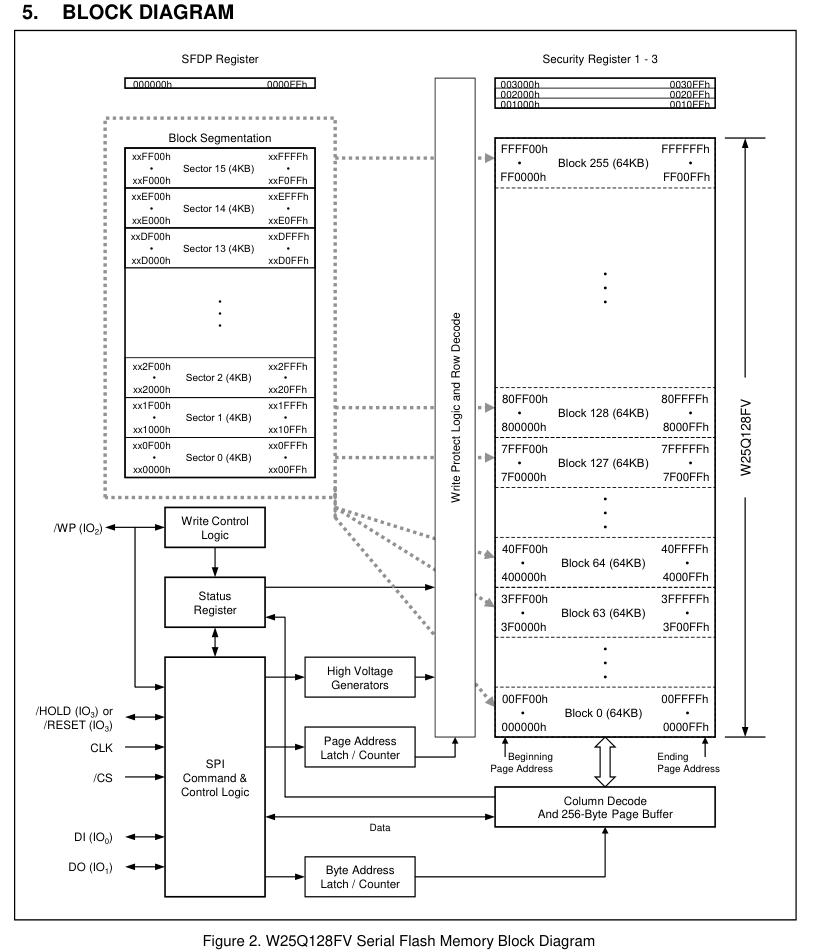

一、SPI NOR 的 “块 - 扇区 - 页” 核心定义

三级结构的本质是 “操作单位分层”,每一级对应不同的硬件操作粒度:

- 页(Page):最小写入单位,通常为 256 字节、512 字节或 1024 字节(主流 256 字节)。写入数据时必须按整页或页内连续地址操作(不能跨页写入单字节)。

- 扇区(Sector):最小擦除单位,通常由多个页组成(如 16 页 = 4KB,32 页 = 8KB)。擦除操作必须按整扇区执行(不能擦除单个页或字节)。

- 块(Block):由多个扇区组成的更大单元(如 16 扇区 = 64KB,32 扇区 = 128KB),部分芯片支持 “块级擦除”(一次擦除整个块,比逐扇区擦除更高效)。

二、主流 SPI NOR 型号的结构实例

几乎所有知名厂商(华邦、兆易创新、旺宏、美光等)的 SPI NOR 都遵循这一结构,仅在具体大小上因容量不同略有差异:

| 型号系列 | 页大小 | 扇区包含页数 | 扇区大小 | 块包含扇区数 | 块大小 | 典型容量示例 |

|---|---|---|---|---|---|---|

| 华邦 W25Q 系列 | 256B | 16 页 | 4KB | 16 扇区 | 64KB | W25Q128(16MB) |

| 兆易创新 GD25Q 系列 | 256B | 16 页 | 4KB | 16 扇区 | 64KB | GD25Q64(8MB) |

| 旺宏 MX25L 系列 | 256B | 16 页 | 4KB | 16 扇区 | 64KB | MX25L128(16MB) |

| 美光 N25Q 系列 | 256B | 16 页 | 4KB | 16 扇区 | 64KB | N25Q064(8MB) |

三、少数 “变体” 不改变核心层级

个别 SPI NOR 型号会因容量或特殊需求调整单级大小,但 “块 - 扇区 - 页” 的三级结构不变:

- 大容量型号(如 512MB 以上):可能将扇区扩大到 8KB(32 页 ×256B),块扩大到 128KB(16 扇区 ×8KB),但层级依然是三级。

- 小容量型号(如 1MB 以下):可能简化块的数量(如 1 块 = 8 扇区),但 “块 - 扇区 - 页” 的逻辑关系不变。

各类 Flash 结构与关键特性

“块 - 扇区 - 页” 并非所有 Flash 的通用结构,仅为SPI NOR 家族的典型分层方式;其他类型 Flash 因功能定位不同,结构差异显著。

| 类别 | 最小擦除单元 | 最小写入单元 | 核心结构特点 | 典型特点 |

|---|---|---|---|---|

| SPI NOR | 扇区(如 4KB) | 页(如 256B) | 块→扇区→页(三层分层) | 随机读快,容量较小(≤256Mbit) |

| 并口 NOR | 扇区(2KB/4KB) | 字 / 字节 | 块→扇区→字节(无 “页” 概念) | 支持字节级写入 |

| Raw NAND | 块(如 128KB) | 页(2KB~16KB) | 块→页→段(简化为 “块 - 页” 两层) | 顺序读写快,容量大(≥1Gbit),需 ECC 和坏块管理 |

| eMMC/UFS | 擦除块(≥512KB) | 段(512B) | 内部隐藏细节,对外仅暴露逻辑块 | 适合大容量存储,用户无需关注底层分层 |

| MCU 片内 Flash | 扇区(1KB/2KB/4KB) | 字(4B) | 块→扇区→字(以 “字” 为最小写入单元) | 适配 MCU 快速编程需求 |

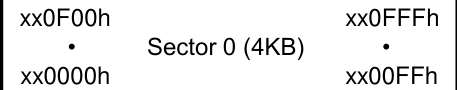

SPI NOR 关键细节

每个扇区里画了 4 个地址角标,它们的意义完全对应 “扇区内部” 的 4 个边界点(用低 12 位表示,高 20 位统一写成 xx):

| 角标 | 低 12 位值 | 在扇区中的位置 | 真实含义 |

|---|---|---|---|

左下 xx000h | 0x000 | 扇区首字节地址 | 扇区开始 |

右下 xx0FFh | 0x0FF | 扇区第 256 字节地址 | 第 1 页末尾 |

左上 xxF00h | 0xF00 | 扇区倒数第 256 字节地址 | 最后一页开始 |

右上 xxFFFh | 0xFFF | 扇区最后一个字节地址 | 扇区结束 |

因此,四角数据就是“一个 4 KB 扇区”的 4 个特征边界地址,帮你一眼看出:

扇区从哪里开始、到哪里结束

页大小 256 B 的切分点(0x000、0x0FF、0xF00、0xFFF)

横着看分别表示了扇区中的第一页和最后一页的范围- 典型分层(以 W25Q 系列为例):1 芯片 = 多个块,1 块 = 多个扇区,1 扇区 = 多个页(如 1 扇区 = 16 页,1 页 = 256B),以上述的W25Q128为例,可以看到,一个存储芯片分为了(0-255)256个块,每个块又分成了(0-15)16个扇区,每个扇区又分成了16个页(每个页256B (1Byte=8bit))

- 地址快速计算:32 位地址中,右移 16 位得块号,右移 12 位得全局扇区号,右移 8 位得全局页号,低 8 位为页内偏移。

记忆口诀与核心总结

SPI NOR 家族的常见存储结构均以 “块 - 扇区 - 页” 为核心分布形式,这是行业主流设计(因擦除、写入单位的硬件限制,必须通过三级分层实现高效管理)。差异仅体现在单级的具体大小(如页 256B vs 512B,扇区 4KB vs 8KB),但 “块包含扇区、扇区包含页” 的层级关系一致。

- 口诀:“NOR 才讲页,NAND 只讲块;扇区是擦除,页是写边界;地址右移 8 找页,右移 12 找扇区。”

- 总结:Flash 的地址层级由其类型决定,SPI NOR 的 “块 - 扇区 - 页” 是特例而非通用标准,判断时需先明确 Flash 类型,再结合手册确认操作单元。