基于单片机的数字电压表设计

绪 言

数字电压表(Digital Voltmeter)简称DVM,它是采用数字化测量技术,把连续的模拟量(直流输入电压)转换成不连续、离散的数字形式并加以显示的仪表。传统的指针式电压表功能单一、精度低,不能满足数字化时代的需求,采用单片机的数字电压表,由精度高、抗干扰能力强,可扩展性强、集成方便,还可与PC进行实时通信。目前,由各种单片A/D 转换器构成的数字电压表,已被广泛用于电子及电工测量、工业自动化仪表、自动测试系统等智能化测量领域,示出强大的生命力。同时,由DVM扩展而成的各种通用及专用数字仪器仪表,也把电量及非电量测量技术提高到崭新水平。目前,数字电压表的内部核心部件是A/D转换器,转换的精度很大程度上影响着数字电压表的准确度,因而,以后数字电压表的发展就着眼在高精度和低成本这两个方面。

本文是以基于单片机的数字电压表的设计为研究内容,本系统主要包括三大模块:转换模块、数据处理模块及显示模块。其中,A/D转换采用ADC0809对输入的模拟信号进行转换,控制核心AT89S52再对转换的结果进行运算处理,最后驱动输出装置4位数码管实时显示数字电压信号,测量的4路输入直流电压范围是0~5V。

第一章 设计总体方案

1.1 设计内容与要求

利用单片机AT89S52与A/D转换器件ADC0809设计一个数字电压表,能够测量0~5V之间的直流电压值,并用4位数码管实时显示该电压值。

1.2 设计思路

1 根据设计要求,选择AT89S52单片机为核心控制器件。

2 A/D转换采用ADC0809,与单片机的接口为P1口和P2口的高四位引脚。

3 电压显示采用4位一体的LED数码管。

4 LED数码的段码输入,由并行端口P0产生;位码输入,用并行端口P2低四位产生。

1.3 设计方案

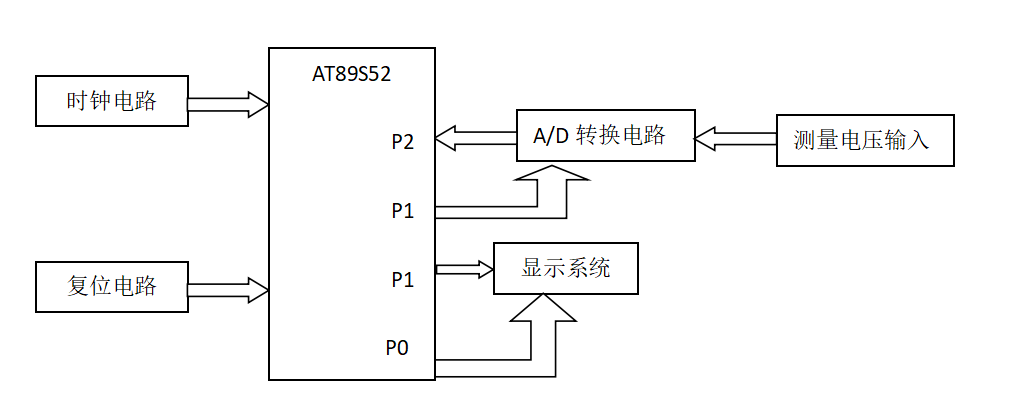

硬件电路设计由6个部分组成; A/D转换电路,AT89S52单片机系统,LED显示系统、时钟电路、复位电路以及测量电压输入电路。硬件电路设计框图如图1所示。

图1.1 数字电压表系统硬件设计框图

1.4 设计目的与意义

设计目的:

1 进一步熟悉和掌握单片机AT89S52的结构和工作原理;

2 掌握ADC0809芯片的特性,控制方法及单片机的接口技术;

3 掌握以单片机为核心的电路设计的基本方法和技术;

4 通过实际程序设计和调试,掌握模块化程序设计的方法和调试技术。

设计意义:

通过完成一个包括电路设计和汇编程序编写的完整过程,解开发单片机应用系统的全过程,强化巩固所学知识,为以后的学习和工作打下基础。

第二章 系统硬件设计

2.1 AT89S52单片机引脚功能介绍

2.1.1 简单概述

单片机是一种集成电路芯片,采用超大规模集成电路技术将具有数据处理能力的中央处理器、随机存取存储器、输入/输出电路,可能还包括定时/计数器、串行通信口、显示驱动电路、脉冲调制电路、模数转换器等电路集成到一片芯片上,构成一个既小而又完善的计算机系统。

AT89S52是低电压、高性能CMOS8位单片机,片内含4K bytes的反复擦写的只读程序存储器和128bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS—52令系统,片内置通用8位中央处理器(CPU)和FLASH存储单元。

2.1.2 AT89S52的引脚介绍

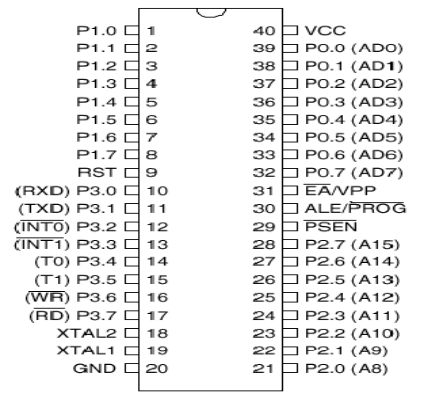

要想掌握AT89S52单片机,应该首先了解AT89S52的引脚。89S52系列及89S52系列中各种型号芯片的引脚是互相兼容的。目前AT89S52单片机多采用40只引脚的双列直插封装方式,AT89S52的引脚分布图如图2.1.2所示 。

图2.1.1 AT89S52的引脚分布图

1 电源引脚

电源引脚接入单片机的工作电源。

(1) Vcc(40引脚):+5V电源。

(2) GND(20引脚):接地。

2 时钟引脚

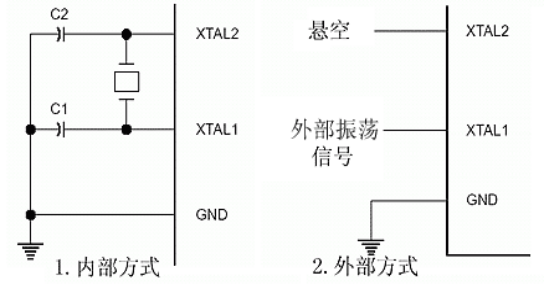

(1) XTAL1(19引脚): 片内振荡器反相放大器和时钟发生器电路的输入端。使用片内振荡器时,该引脚连接外部石英晶体和微调电容。

(2) XTAL2(20引脚):片内振荡器反相放大器的输出端。使用片内振荡器时,该引脚连接外部石英晶体和微调电容,采用外接时钟源时,引脚XTAL1接收 外部时钟振荡器的信号,XTAL2悬空。XTAL1和XTAL2的电源接入方式如图2.1.2所示:

图2.1.2 电源接入方式

3 控制引脚

(1)复位RST(9引脚)

复位线,可以使89S52处于复位(即初始化)工作状态。在振荡器运行时,有持续时间大于2个机器周期(24个振荡周期)以上的高电平出现在此引脚时,就能使该单片机复位,只要这个脚保持高电平,51芯片便循环复位。

在单片机正常工作时,此引脚应为≤0.5V的低电平。

(2)/Vpp(31引脚)

为外部程序存储器访问允许控制端。当它为高电平时,单片机读片内程序存储器,在PC值超过0FFFH后将自动转向外部程序存储器。当它为低电平时,只限定在外部程序存储器,地址为0000H~FFFFH。Vpp为该引脚的第二功能,为

编程电压输入端。

(3)ALE/(30引脚)

ALE为低八位地址锁存允许信号。在访问外部存储器时,89S52的CPU在P0.0-P0.7引脚线去传送随后而来的片外存储器读/写数据。在不访问片外存储器时,89S52自动在ALE线上输出频率为时钟振荡器频率fosc的1/6的脉冲序列。该脉冲序列可以作为外部时钟源或定时脉冲使用。为该引脚的第二功能,在对片内存储器编程时,此引脚为编程脉冲输入端。

(4)(29引脚)

片外程序存储器的读选通信号。在单片机读片外程序存储器时,89S52自动在此引脚线上产生一个负脉冲,作为片外程序存储器的读选通信号。

4 I/O口引脚

(1) P0口:(pin39-pin32为P0.0-P0.7输入输出脚)

P0是一个8位漏极开路型双向I/O口。P0口具有两种功能:第一,P0口可以作为通用的I/O口使用,用于传输CPU的输入/输出数据,需要加上上拉电阻。当作为普通的I/O输入时,应该先向端口的输出锁存器写入1。P0口可以驱动8个LS型TTL负载。第二,P0口在CPU访问片外存储器时用于传送片外存储器的低8位地址,然后传送CPU对片外存储器的读写。

(2) P1口:(Pin1-Pin8为P1.0-P1.7输入输出脚)

P1口是一个带内部上拉电阻的8位双向I/0口。P1口能驱动4个LSTTL负载。其中P1.7为最高位,P1.0为最低位,当P1口作为通用I/O口使用时,P1.0-P1.7的功能和P0口的第一功能相同,也用于传送用户的输入和输出数据。

(3) P2口:(Pin21-Pin28为P2.0-P2.7输入输出脚)

P2口是一个带内部上拉电阻的8位双向I/O口,P2口能驱动4个LSTTL负载。这组引脚可以作为通用I/O口使用,也用于传送用户的输入和输出数据。当89S52扩展外部存储器及I/O口时,P2口用于输出片外存储器的高8位地址。

添加链接描述