AD5621(单通道缓冲电压输出DAC)芯片的详细用法

目录

一,硬件电路与接线

二、软件写入信号(基于 SPI 协议)

1. 数据帧格式

2. SPI 时序控制(图 2)

3. 异常处理

二、ESP32-PICO 软件模拟 SPI 控制 AD5621 代码

1.硬件接线

2.ESP32-PICO软件模拟SPI代码

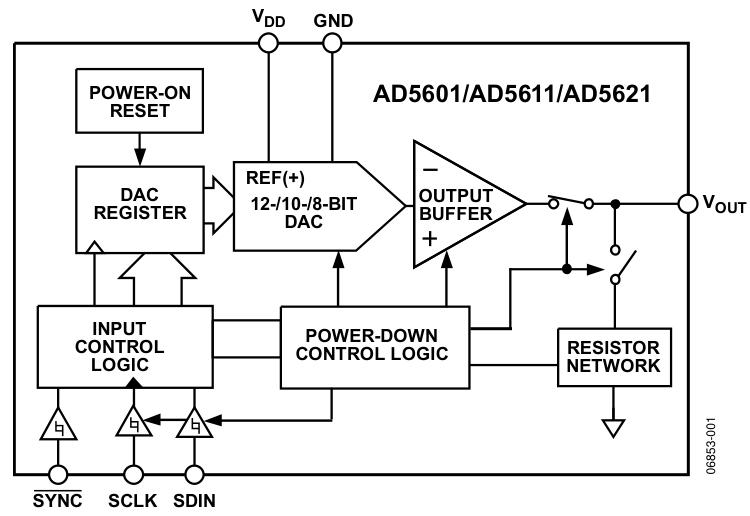

一,硬件电路与接线

核心引脚定义与供电

| 引脚 | 名称 | 功能描述 |

|---|---|---|

| 1 | SYNC | 同步信号(低有效),下拉启动 SPI 通信,16 位数据传输后上升沿更新 DAC 寄存器 |

| 2 | SCLK | 串行时钟(最大 30MHz),数据在下降沿采样 |

| 3 | SDIN | 串行数据输入(16 位,MSB 优先),前 2 位为控制位(PD1/PD0),后 12 位为 DAC 码 |

| 4 | VDD | 电源(2.7V~5.5V),需就近并联 0.1μF 陶瓷电容(高频去耦)+10μF 钽电容(低频储能) |

| 5 | GND | 地,裸露焊盘(EP)必须直接接地以降低热阻 |

| 6 | VOUT | 轨到轨电压输出(0V~VDD),直接驱动负载(2kΩ+200pF 以内) |

供电设计:

单电源供电,VDD 建议通过 LC 滤波(如 10Ω+10μF)抑制噪声,避免与大电流模块共地;

基准电压直接取自 VDD,无需外部参考源,输出公式:VOUT=VDD×4096D(D=0∼4095)

二、软件写入信号(基于 SPI 协议)

1. 数据帧格式

控制位(前 2 位):

| PD1 | PD0 | 模式 | 说明 |

|---|---|---|---|

| 0 | 0 | 正常模式 | 输出缓冲激活,电流 75μA(5V 典型) |

| 0 | 1 | 掉电 1kΩ 接地 | 电流 0.2μA(3V 典型),用于快速恢复 |

| 1 | 0 | 掉电 100kΩ 接地 | 更低漏电流,适合高阻抗负载 |

| 1 | 1 | 三态(高阻) | 输出悬空,需外部上拉 / 下拉 |

数据位(后 12 位):12 位 DAC 码(0x000~0xFFF),MSB 在前,补零至 16 位。

示例:输出 2.5V(VDD=5V),代码 \(D=2.5/5 \times 4096=2048\),对应 16 位帧为 0b00_0000_0000_0000(控制位 00 + 0x0800),这里相当于做一个量程转换。

2. SPI 时序控制(图 2)

写操作步骤:

拉低 SYNC(t8≥20ns),启动传输;

在 SCLK 下降沿逐位发送 16 位数据(t5≥5ns 建立时间,t6≥4.5ns 保持时间);

第 16 个下降沿后,拉高 SYNC,DAC 寄存器更新(t7=0ns);

SYNC 高电平持续≥20ns,准备下次传输。

3. 异常处理

SYNC 中断:若传输中提前拉高 SYNC(t9≥13ns),当前数据被丢弃,避免无效更新;

掉电恢复:从掉电模式(如 1kΩ 接地)恢复需 13μs(5V),需在代码中加入延迟或状态标志。

二、ESP32-PICO 软件模拟 SPI 控制 AD5621 代码

1.硬件接线

| AD5621 引脚 | 功能 | ESP32-PICO GPIO(可自定义) | 说明(基于 AD5621.pdf 引脚定义) |

|---|---|---|---|

| SYNC | 同步信号(低有效) | GPIO2 | 拉低启动通信,16 位数据发送后拉高更新 DAC 输出 |

| SCLK | 串行时钟 | GPIO4 | 软件手动控制电平,空闲低(CPOL=0),下降沿采样数据 |

| SDIN | 串行数据输入 | GPIO5 | 软件输出数据位(MSB 优先),需与 SCLK 时序同步 |

| VDD | 电源 | 3.3V 或 5V | 符合文档 2.7V~5.5V 供电范围,需与代码VDD变量一致 |

| GND | 地 | GND | 必须共地,AD5621 裸露焊盘(EP)需同步接地 |

| VOUT | 模拟输出 | -(接负载 / 示波器) | 输出范围 0V~VDD,文档建议负载≤2kΩ(并联电容≤200pF) |

2.ESP32-PICO软件模拟SPI代码

#include <Arduino.h>// 1. 软件模拟SPI引脚定义(可根据实际接线修改)

const int AD5621_SYNC = 2; // SYNC引脚

const int AD5621_SCLK = 4; // SCLK引脚

const int AD5621_SDIN = 5; // SDIN引脚

const float VDD = 3.3; // AD5621供电电压(3.3V/5V,需与硬件一致)

// 正常模式控制码(AD5621.pdf图41:前2位控制位PD1=0、PD0=0,对应正常工作)

const uint16_t NORMAL_MODE = 0b00 << 14;// 2. 初始化软件SPI引脚

void AD5621_SPI_Init() {pinMode(AD5621_SYNC, OUTPUT);pinMode(AD5621_SCLK, OUTPUT);pinMode(AD5621_SDIN, OUTPUT);// 初始状态:SYNC拉高(禁止通信),SCLK拉低(空闲低,符合CPOL=0)digitalWrite(AD5621_SYNC, HIGH);digitalWrite(AD5621_SCLK, LOW);

}// 3. 软件模拟SPI发送16位数据(核心:AD5621.pdf时序要求——下降沿采样)

// 数据帧格式:2位控制位 + 12位DAC数据 + 2位忽略位(MSB优先)

void AD5621_SPI_Send16Bits(uint16_t data) {// 步骤1:拉低SYNC,启动通信(AD5621.pdf图2:SYNC低电平有效)digitalWrite(AD5621_SYNC, LOW);delayMicroseconds(1); // 确保SYNC低电平稳定(满足文档t8≥20ns)// 步骤2:逐位发送16位数据(MSB优先,从bit15到bit0)for (int i = 15; i >= 0; i--) {// ① 输出当前数据位到SDIN(先准备数据,满足文档t5≥5ns建立时间)uint8_t dataBit = (data >> i) & 0x01;digitalWrite(AD5621_SDIN, dataBit);delayMicroseconds(1); // 数据建立时间(远大于文档要求的5ns)// ② SCLK拉高(上升沿,AD5621不采样,符合CPHA=1)digitalWrite(AD5621_SCLK, HIGH);delayMicroseconds(1); // 满足文档t2≥5ns(SCLK高电平持续时间)// ③ SCLK拉低(下降沿,AD5621采样SDIN数据,核心时序)digitalWrite(AD5621_SCLK, LOW);delayMicroseconds(1); // 满足文档t3≥5ns(SCLK低电平持续时间)}// 步骤3:拉高SYNC,更新DAC输出(AD5621.pdf第14章:SYNC拉高触发更新)digitalWrite(AD5621_SYNC, HIGH);delayMicroseconds(1); // 确保更新完成

}// 4. 计算DAC数据并发送(基于AD5621.pdf输出电压公式:Vout = VDD × D/4096)

void AD5621_SetVoltage(float targetVoltage) {uint16_t dacCode;// 电压范围保护(避免超出AD5621 0V~VDD输出范围)if (targetVoltage < 0.0) {dacCode = 0;} else if (targetVoltage > VDD) {dacCode = 4095; // 12位DAC最大数据(全1码)} else {dacCode = (uint16_t)(targetVoltage / VDD * 4096);}// 构建16位数据帧(控制位2位 + DAC数据12位 + 忽略位2位)uint16_t dataFrame = NORMAL_MODE | (dacCode << 2);// 发送数据帧AD5621_SPI_Send16Bits(dataFrame);// 串口调试(可选,验证数据)Serial.print("DAC代码:");Serial.print(dacCode);Serial.print(" | 目标电压:");Serial.print(targetVoltage);Serial.print("V | 实际输出:");Serial.print((float)dacCode / 4096 * VDD, 3);Serial.println("V");

}// 5. 初始化与主循环

void setup() {Serial.begin(115200); // 串口调试(波特率115200)AD5621_SPI_Init(); // 初始化软件SPISerial.println("AD5621软件SPI初始化完成,开始输出电压...");

}void loop() {// 循环输出不同电压(每隔2秒切换,可根据需求修改)AD5621_SetVoltage(0.0); // 输出0Vdelay(2000);AD5621_SetVoltage(1.0); // 输出1Vdelay(2000);AD5621_SetVoltage(2.0); // 输出2Vdelay(2000);AD5621_SetVoltage(VDD); // 输出最大电压(与VDD一致)delay(2000);

}1. 软件模拟 SPI 时序

AD5621.pdf 要求 SPI 时序为CPOL=0(SCLK 空闲低)、CPHA=1(下降沿采样),代码中通过以下步骤实现:

SCLK 初始状态:AD5621_SPI_Init()中设置digitalWrite(AD5621_SCLK, LOW),符合 “空闲低” 要求;

数据采样边沿:每发送 1 位数据时,先将数据位输出到 SDIN(准备数据),再拉高 SCLK(上升沿,不采样),最后拉低 SCLK(下降沿,AD5621 采样数据),完全匹配文档图 2 时序;

时序参数满足:delayMicroseconds(1)(1 微秒 = 1000 纳秒)远大于文档要求的 “建立时间 t5≥5ns”“SCLK 高电平 t2≥5ns”“SCLK 低电平 t3≥5ns”,确保时序稳定。

2. 数据帧格式

AD5621.pdf 图 41 明确 16 位输入寄存器格式为 “2 位控制位 + 12 位 DAC 数据 + 2 位忽略位”:

控制位:NORMAL_MODE = 0b00 << 14(对应正常工作模式,禁止掉电);

DAC 数据:12 位dacCode左移 2 位,填充 “忽略位”,确保数据对齐寄存器;

示例:目标电压 1.65V(VDD=3.3V),dacCode=2048(0x800),数据帧 = 0b00_100000000000_00(0x8000),完全符合文档格式。