玳瑁的嵌入式日记---0919(ARM)

1. 什么是 RISC、CISC

CPU的指令集其实就是用指令对计算机实现控制和计算的指令集合。

分复杂指令集和精简指令集。

RISC:Reduced Instruction Set Computer

CISC:Complex Instruction Set Computer

- CISC(Complex Instruction Set Computer,复杂指令集计算机)

- 特点:指令系统复杂庞大,指令数目一般多达 200 - 300 条,指令格式多 样化,寻址方式丰富,可直接对存储器进行操作。比如一条 CISC 指令可能完成诸如读取内存数据、进行复杂运算并写回内存等多个操作。

- 优势: 对于一些复杂的任务,一条 CISC 指令就能完成,在高级语言编程中可以减少程序代码行数。在早期,CISC 架构可以较好地兼容已有的软件。

- 劣势:由于指令复杂,硬件设计难度大,指令执行速度慢,指令执行周期不固定。而且芯片面积大,功耗高。典型的 CISC 架构处理器有 x86 系列,如 Intel 的奔腾、酷睿系列处理器。

- RISC(Reduced Instruction Set Computer,精简指令集计算机)

- 特点:指令系统相对简单,指令数目一般在几十条,指令格式规整,寻址方式少,通常只允许 load(加载)和 store(存储)指令对存储器进行操作,其余指令都在寄存器之间进行运算 。

- 优势:指令简单,使得硬件设计更简单,指令执行速度快,指令执行周期固定,可以实现流水线操作。同时,芯片面积小,功耗低。

- 劣势:对于复杂任务,可能需要多条指令才能完成,导致程序代码行数增多。不过,随着编译器技术的发展,这一劣势在一定程度上得到了缓解。典型的 RISC 架构处理器有 ARM 系列、MIPS 等。

2. 冯・诺伊曼架构和哈佛架构有何区别?ARM 内核属于哪一种?

- 冯・诺伊曼架构

- 特点:使用单一的存储器,程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置,程序指令和数据的宽度相同。指令和数据通过同一总线进行传输。

- 优势:结构简单,成本低,易于实现。对于一些简单的应用场景,这种架构可以很好地满足需求。

- 劣势:在取指令和取数据时会产生冲突,尤其是在高速运行时,会影响系统性能。

- 哈佛架构

- 特点:拥有独立的程序存储器和数据存储器,程序指令和数据分开存储,各自有独立的总线。这意味着可以同时进行取指令和取数据操作。

- 优势:可以提高数据的吞吐率,增强了处理器的并行处理能力,在高速运行时性能优势明显。

- 劣势:结构相对复杂,成本较高。

- ARM 内核:ARM 内核在最初设计时采用冯・诺伊曼架构,但随着技术发展,现在的 ARM 内核采用了改进的哈佛架构,例如 ARM9 及之后的许多内核版本,它们拥有分离的指令缓存和数据缓存,支持同时取指令和取数据,提高了处理器的性能。

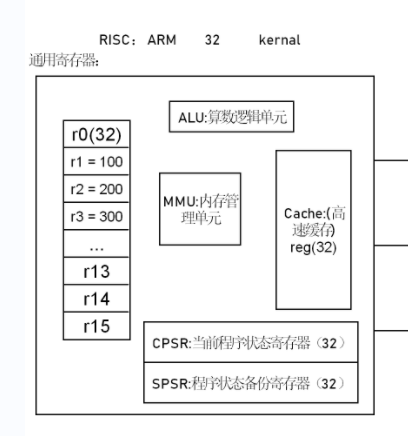

3. ARM 内核中都有什么?

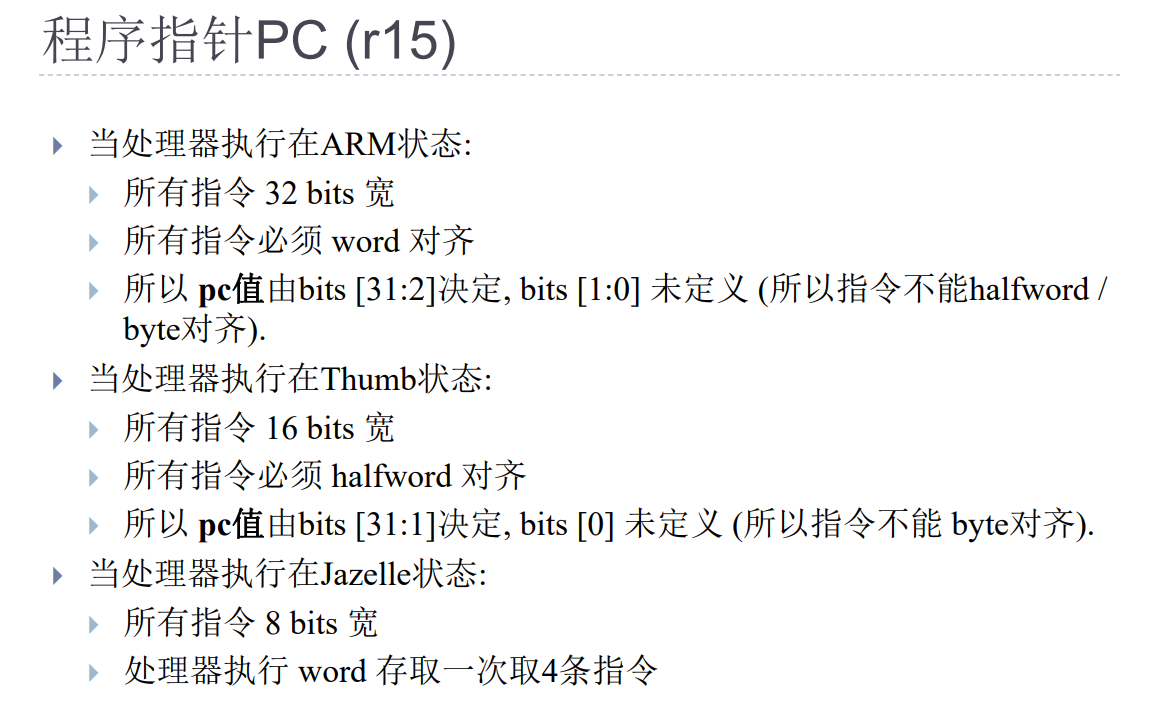

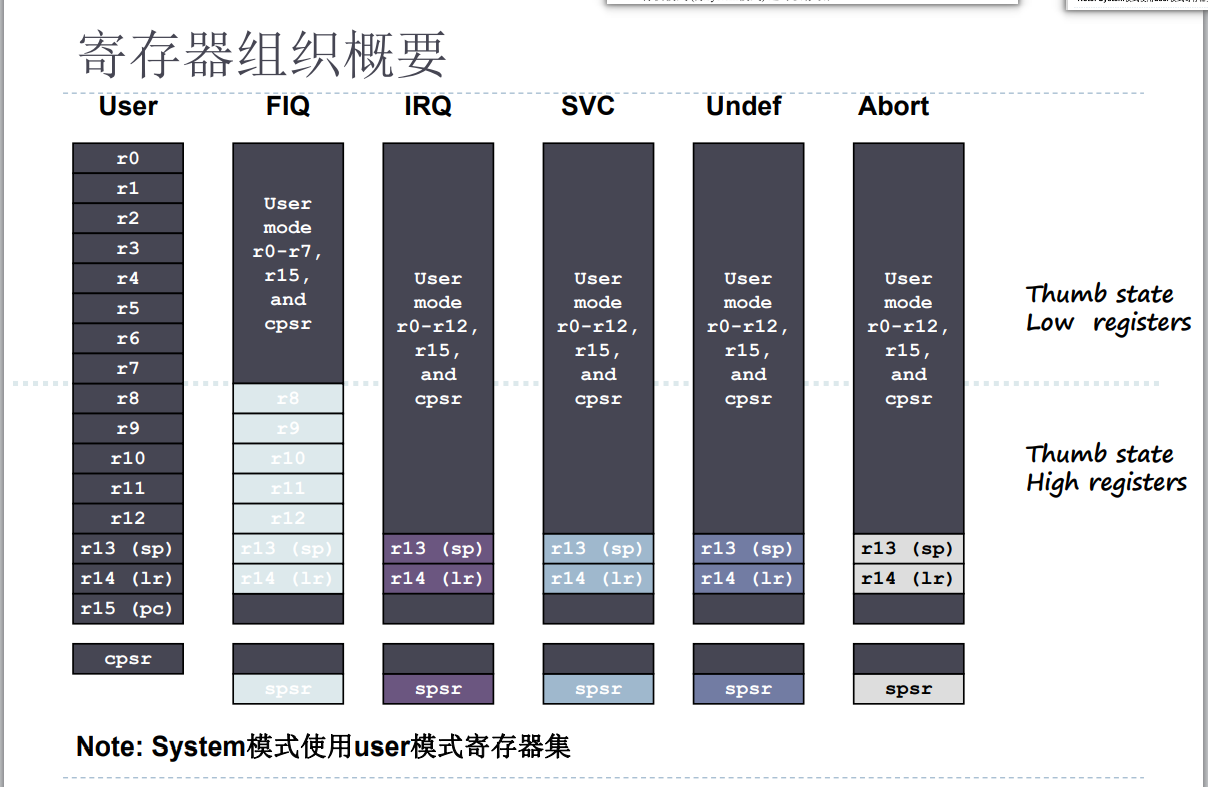

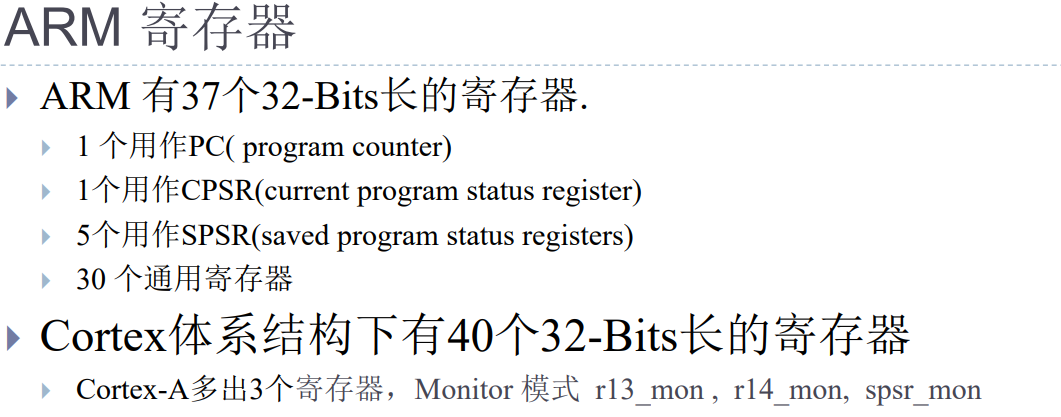

- 寄存器组:包含通用寄存器、程序计数器(PC)、状态寄存器等。通用寄存器用于数据的暂存和运算;程序计数器存储下一条要执行的指令地址;状态寄存器用于记录处理器的工作状态,如运算结果的标志位(是否溢出、是否为零等)。

- r13(SP) ,r14(LR), r15(PC)

- 指令执行单元:负责对指令进行解码和执行,按照指令的要求完成算术运算、逻辑运算、数据传输等操作。

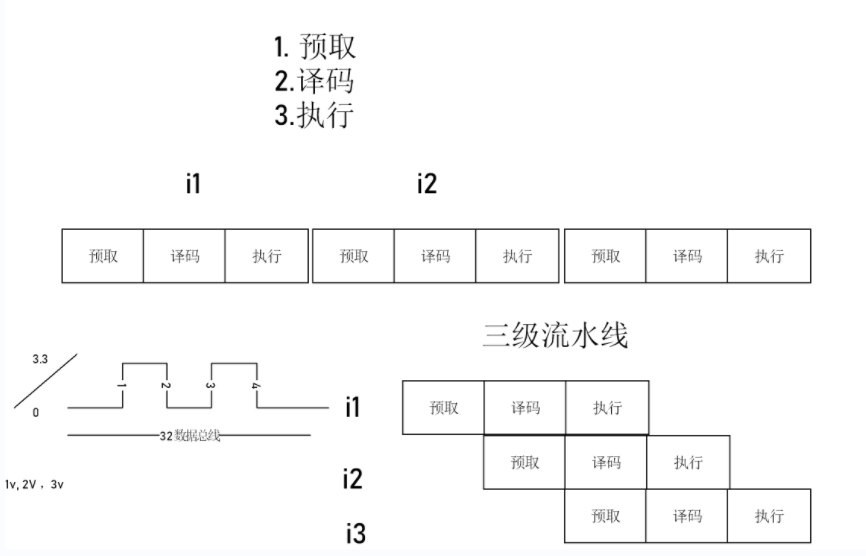

- 流水线:现代 ARM 内核大多采用流水线技术,例如 3 级流水线(取指、译码、执行)或更复杂的流水线结构(如 ARM7 的 3 级流水线、ARM9 的 5 级流水线等),以提高指令的执行效率,使得处理器在一个时钟周期内可以处理多条指令。

- 存储器接口:用于与外部存储器(如闪存、RAM 等)进行数据和指令的传输,实现对程序和数据的读取与存储。

- 中断处理单元:当系统发生中断事件(如外部设备请求、异常情况等)时,中断处理单元负责暂停当前程序的执行,保存现场,然后跳转到相应的中断服务程序进行处理,处理完成后恢复现场并继续执行原来的程序。

- 通用寄存器:有 r0 到 r15 等,像 r0 是 32 位的,图中还示例 r1 值为 100、r2 为 200、r3 为 300 等,这些寄存器用于数据的暂存、运算等操作。

- ALU(算数逻辑单元):负责进行算术运算(如加、减等)和逻辑运算(如与、或等)。

- MMU(内存管理单元):用于管理内存,实现虚拟地址到物理地址的转换等功能,帮助系统高效、安全地使用内存。

- Cache(高速缓存):是 32 位的,用于存储常用的数据和指令,提高处理器访问数据的速度,因为从 Cache 中读取数据比从主存中快很多。

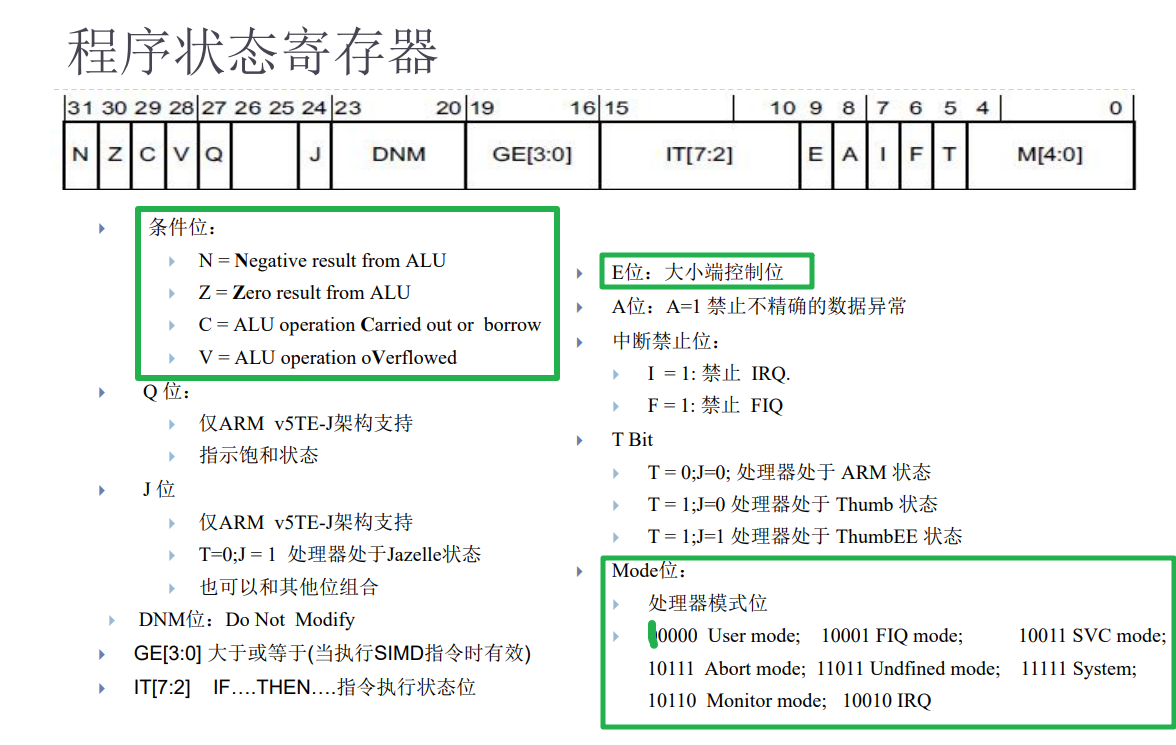

- CPSR(当前程序状态寄存器):32 位,用于记录当前程序运行的状态,比如运算结果的标志(是否溢出、是否为零等)、处理器的工作模式等。

- SPSR(程序状态备份寄存器):32 位,当发生异常(如中断、异常处理等)时,用于备份 CPSR 的内容,以便在异常处理完成后恢复原来的程序状态。

4. ARM 有几种工作模式?

ARM 处理器共有 7 种工作模式:

- 用户模式(User,USR):正常程序执行的模式,用户程序一般在该模式下运行,对系统资源的访问受到一定限制。

- 快速中断模式(Fast Interrupt Request,FIQ):一个高优先级(fast)中断产生时将会进入这种模式 ,用于快速响应中断请求,当有快速中断发生时,处理器进入此模式。该模式下有更多的私有寄存器,以减少中断处理时的现场保护和恢复时间。

- 外部中断模式(Interrupt Request,IRQ):一个低优先级(normal)中断产生时将会进入这种模式 ,处理一般的外部中断请求,当外部设备发出中断信号时,处理器可能进入此模式。

- 管理模式(Supervisor,SVC):当复位或软中断指令执行时将会进入这种模式 ,操作系统内核运行的模式,在系统复位或软件中断(SWI)时进入该模式,具有较高的权限,可以访问系统所有资源。

- 数据访问终止模式(Abort,ABT):当存取异常时将会进入这种模式 ,当发生数据访问异常(如地址无效、权限错误等)时,处理器进入此模式,用于处理数据访问异常情况。

- 系统模式(System,SYS):用于运行特权级的操作系统任务,与用户模式使用相同的寄存器组,但具有更高的权限,可以访问系统所有资源,它的目的是为了让操作系统任务可以方便地访问用户模式的资源。

- 未定义指令中止模式(Undefined,UND):当执行未定义指令时会进入这种模式 ,当处理器遇到无法识别的指令时,进入此模式,用于处理未定义指令异常。

5. 什么是异常向量表?

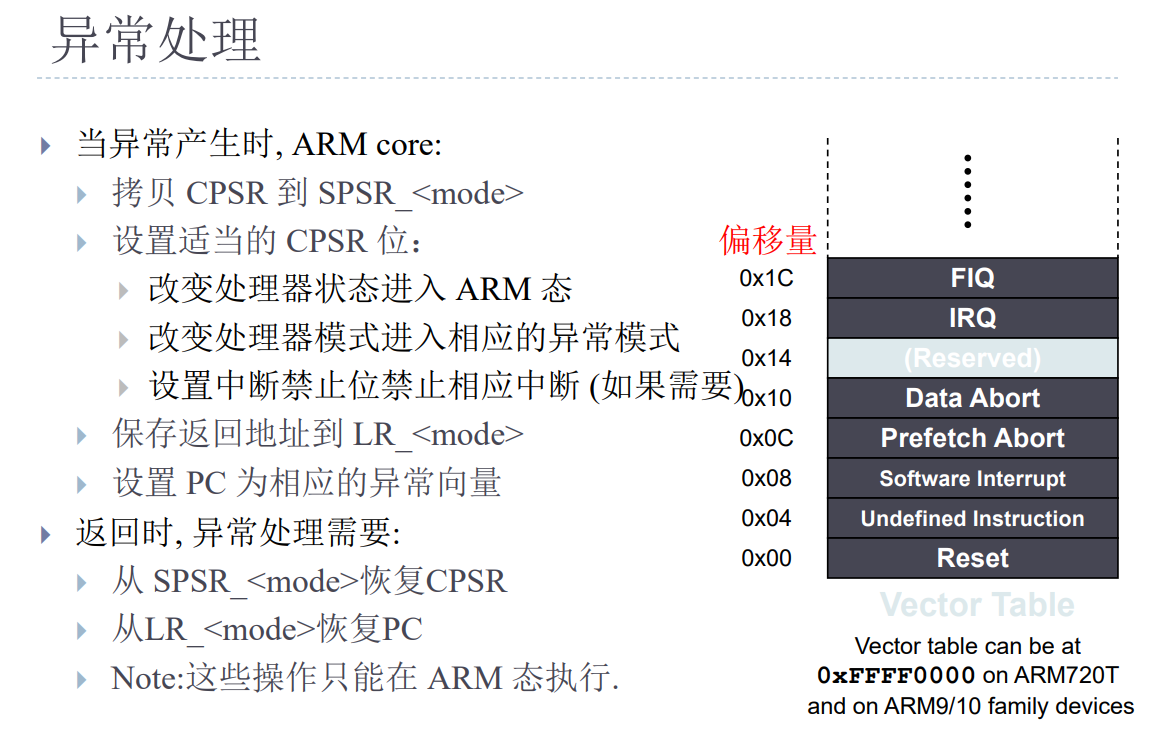

异常向量表是存储异常处理程序入口地址的一段连续内存区域。当 ARM 处理器发生异常(如中断、数据访问终止、未定义指令等)时,处理器会根据异常的类型,从异常向量表中找到对应的异常处理程序入口地址,然后跳转到该地址去执行异常处理程序。

在 ARM 架构中,异常向量表的位置可以是固定的(早期 ARM 版本,位于 0x00000000 地址开始的一段区域 ),也可以通过设置协处理器指令来重新定位(如在 ARMv7 及更高版本中,可以通过设置 VBAR 寄存器来指定异常向量表的基地址 )。异常向量表中每个异常类型对应一个固定的地址偏移,例如:

- 复位异常(Reset)对应异常向量表的 0x00 地址,当处理器复位时,会从该地址对应的处理程序开始执行。

- 未定义指令异常对应 0x04 地址,当遇到未定义指令时,处理器跳转到该地址处的程序进行处理。

- 软件中断(SWI)对应 0x08 地址,当执行软件中断指令时,处理器会跳转到该地址对应的中断处理程序。

通过异常向量表,ARM 处理器可以快速、高效地响应各种异常情况,保证系统的稳定运行。

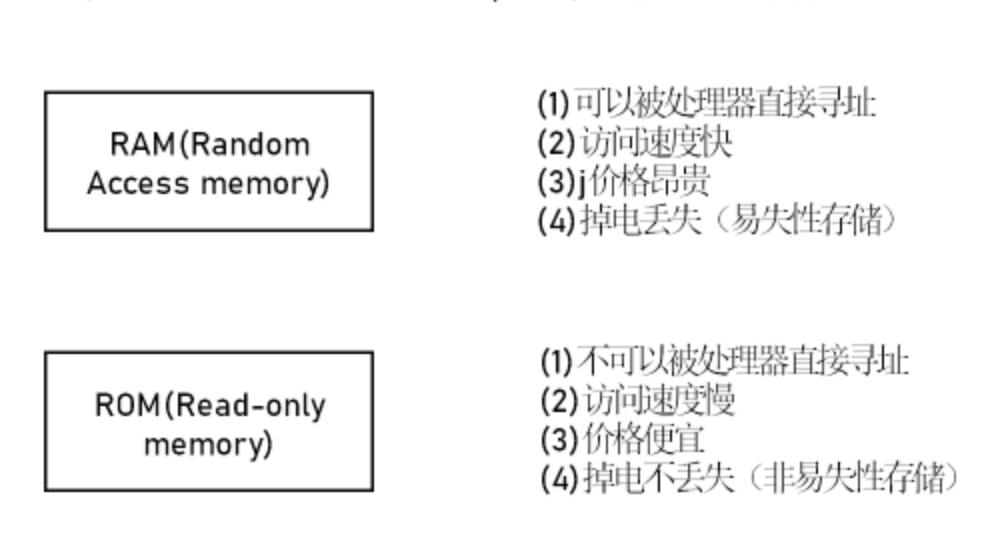

RAM 与 ROM

RAM(Random Access Memory,随机存取存储器)和 ROM(Read-Only Memory,只读存储器)是计算机 / 嵌入式系统中最核心的两类 主存储介质,本质区别在于 数据是否可擦写、断电后数据是否保留,以及由此衍生的功能定位。

| 对比维度 | RAM(随机存取存储器) | ROM(只读存储器) |

|---|---|---|

| 数据保留性 | 易失性(断电丢失) | 非易失性(断电保留) |

| 读写特性 | 高速、可随机读写(字节级修改) | 低速、只读(或需特殊条件擦写,块级操作) |

| 核心功能 | 临时存储 CPU 运行时的指令 / 数据 | 永久存储固定程序 / 数据(如启动代码) |

| 访问速度 | 纳秒级(如 DDR5:~10ns) | 微秒级(如 NOR Flash:~100ns) |

| 成本与容量 | 成本高、容量灵活(KB~GB 级) | 成本低、容量较小(MB~GB 级,通常小于 RAM) |

| 典型应用 | ARM 内核缓存、设备运行内存(DDR) | ARM 启动代码(Bootloader)、系统固件 |

内存管理单元(MMU)

MMU 的主要功能包括:

- 虚拟内存与物理内存映射:将进程使用的虚拟地址转换为实际的物理内存地址,使多个进程可以在各自的虚拟地址空间中运行,而无需关心物理内存的具体分配。

- 内存保护:可以设置不同的内存访问权限,防止进程非法访问其他进程或系统的内存空间,保障系统的稳定性和安全性。

总线架构

多总线结构

AHB(Advanced High - performance Bus,高级高性能总线)

APB(Advanced Peripheral Bus,高级外设总线)

指令集格式

- ARM 状态:使用 32 位的指令集,指令长度固定为 32 位。每一条指令都包含了完整的操作信息,例如操作码、操作数地址等。比如,一条典型的 ARM 32 位指令可以完成复杂的算术逻辑运算,像对两个 32 位数据进行加法操作,并根据结果设置状态寄存器标志位 。

- Thumb 状态:采用 16 位的指令集,指令长度为 16 位。Thumb 指令是 ARM 指令集的一个子集,它通过对一些常用操作进行编码优化,减少了指令所占的存储空间 。不过,Thumb 指令的功能相对单一,往往需要多条指令组合才能完成与 ARM 32 位指令相同的复杂操作。