如何判断nmos和pmos导通和截止

在智能手机、计算机、新能源汽车等现代电子设备的核心电路中,MOSFET(金属氧化物半导体场效应晶体管)如同“电子开关”般无处不在,其精准的导通与截止控制是电路高效运行的基础。其中,NMOS(N沟道MOS管)和PMOS(P沟道MOS管)作为两种最常用的类型,因载流子(电子与空穴)的差异,形成了互补的工作特性,共同支撑着数字逻辑、电源管理等关键功能的实现。对于电子工程师而言,能否快速判断二者的导通与截止状态,直接影响电路设计的效率和调试的准确性。

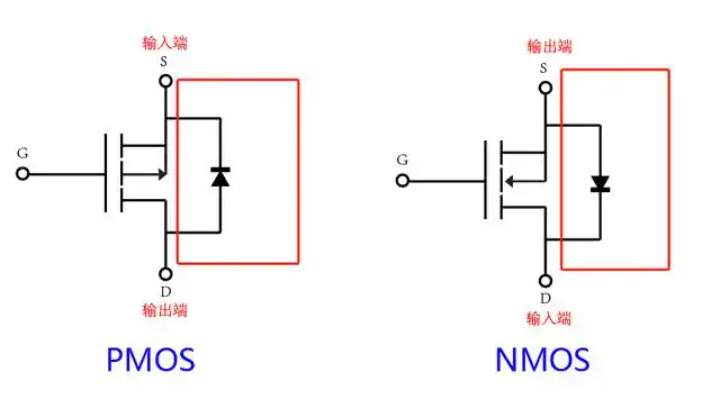

NMOS的导通逻辑源于电子的移动特性:其导电沟道由电子构成,因此需要栅极电位高于源极,才能吸引电子形成导电通路。具体来说,当栅源电压(Vgs,即栅极与源极的电位差)大于其阈值电压Vth(通常为2-4V,不同型号略有差异)时,NMOS管的漏极(D)与源极(S)之间形成N型沟道,电流从漏极流向源极(因电子带负电,实际运动方向与电流方向相反)。例如,在5V供电的数字电路中,若某NMOS的Vth=3V,当栅极接5V、源极接0V时(Vgs=5V>3V),管子导通,漏极与源极之间近似短路;若栅极接2V(Vgs=2V<3V),则沟道无法形成,管子处于截止状态,漏极与源极之间近似开路。这种“高电平导通、低电平截止”的特性,使其常被用于控制电路的“开启”信号,如微处理器的输出引脚通过高电平驱动NMOS,实现对负载的供电控制。

与NMOS相反,PMOS的导电沟道由空穴(带正电)构成,因此需要栅极电位低于源极,才能形成有效通路。其导通条件为Vgs小于阈值电压Vth(该值为负值,绝对值通常也在2-4V)。例如,某PMOS的Vth=-3V,当栅极接0V、源极接5V时(Vgs=0V-5V=-5V<-3V),管子导通,电流从源极流向漏极;若栅极接3V(Vgs=3V-5V=-2V>-3V),则无法满足导通条件,管子截止。这种“低电平导通、高电平截止”的特性,使其适合与NMOS配合使用,例如在锂电池保护电路中,PMOS常被用于控制负极通路,当检测到过流信号时,栅极被施加高电平,PMOS截止,从而切断电池输出。 总结来看,NMOS与PMOS的核心差异可归纳为三点:

1. 电流方向:NMOS为漏极→源极(电子从源极→漏极),PMOS为源极→漏极(空穴从源极→漏极);

2. 电压要求:NMOS需Vgs>Vth(正阈值),PMOS需Vgs<Vth(负阈值);

3. 电平响应:NMOS对高电平敏感(高电平导通),PMOS对低电平敏感(低电平导通)。

这些差异在CMOS(互补金属氧化物半导体)电路中得到了巧妙应用。例如,CMOS反相器由一个NMOS和一个PMOS组成:当输入高电平时,NMOS导通、PMOS截止,输出低电平;当输入低电平时,PMOS导通、NMOS截止,输出高电平。这种互补结构不仅降低了静态功耗(同一时刻只有一个管子导通),还提高了电路的抗干扰能力,成为数字集成电路的主流架构。在电源管理领域,二者的配合同样关键:例如在DC-DC转换器中,NMOS常作为同步整流管(低导通电阻适合大电流),PMOS作为续流管,通过交替导通实现高效的电压转换。

掌握NMOS和PMOS的导通与截止规律,是电子工程师进行电路设计和故障排查的基础。例如,在调试电机驱动电路时,若电机无法启动,可通过测量MOS管的Vgs值快速判断是否因驱动电压不足导致管子未导通;在设计高频开关电路时,需根据NMOS和PMOS的开关速度差异(NMOS通常更快)选择合适的型号,以减少开关损耗。可以说,对这两种器件特性的深入理解,是实现电路高效、稳定运行的前提。