Buck电路输出电容设计:从理论到实践的完整指南

1. 前言

在开关电源设计中,Buck电路(降压斩波器)无疑是应用最广泛的拓扑结构之一。然而,一个稳定高效的Buck电路,其性能往往取决于最容易被忽视的配角——输出电容。很多初学者在设计中会发现,为什么原理图中的输出电容总是由多个不同容值的电容并联组成?其背后的设计逻辑是什么?本文将深入剖析Buck电路输出电容的设计方法,揭示并联背后的工程哲学,并提供实用的设计步骤和选型建议。

2. 输出电容的核心作用

在Buck电路中,输出电容 C_out 绝非一个简单的滤波元件,它肩负着两大核心使命:

滤除开关纹波电流:平滑电感电流中的交流分量,将输出电压的纹波(ΔV_ripple)抑制在负载芯片允许的范围内。

提供动态能量:在负载电流发生瞬态变化时(如CPU突然从低负载进入高负载状态),充当一个微型“能量水库”,迅速提供或吸收电流,维持输出电压的稳定,直到控制环路调整过来。

简单来说,它既要应对“稳态”的纹波,也要应对“瞬态”的冲击,其设计直接关系到电源的稳定性、噪声性能和动态响应速度。

3. 设计步骤:一个系统化的流程

输出电容的设计是一个在体积、成本和性能之间寻找平衡的艺术。遵循以下步骤,可以系统地完成设计。

步骤一:明确设计指标

开始计算前,必须明确以下系统参数:

输入电压范围 (V_in_min, V_in_max)

额定输出电压 (V_out)

最大输出电流 (I_out_max)

开关频率 (f_sw)

电感值 (L) (通常已先行确定)

最大允许输出电压纹波 (ΔV_ripple) (核心指标,由负载芯片手册决定,通常是mV级)

负载瞬态要求:负载阶跃变化的大小 (ΔI_out) 和允许的输出电压偏差 (ΔV_transient)

步骤二:基于输出纹波要求计算

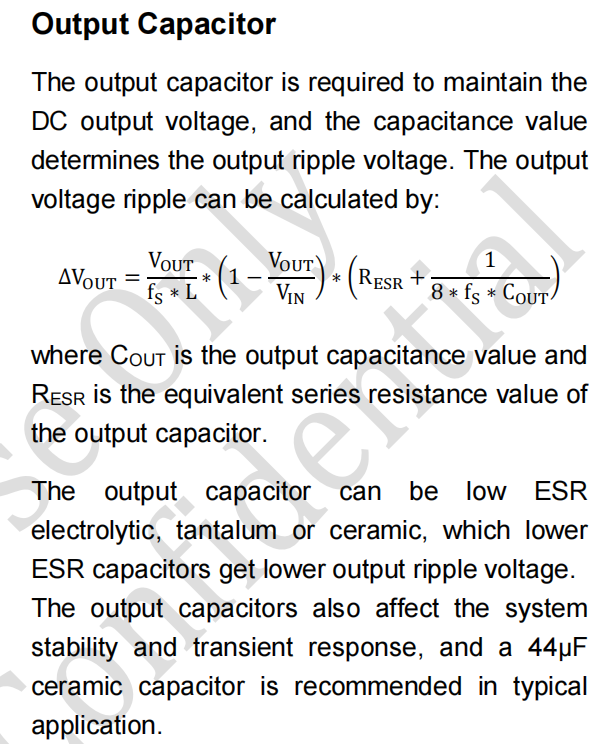

这是最经典的首选方法。输出纹波主要由电容的容值和等效串联电阻 (ESR) 决定。

计算电感纹波电流 (ΔI_L):

ΔI_L = (V_in_max - V_out) * (V_out / V_in_max) * (1 / (f_sw * L))

通常,ΔI_L 被设计为额定输出电流的 20% ~ 40%。分析纹波电压组成:

总纹波由两部分组成:ESR 引起的纹波:

ΔV_esr = ΔI_L * ESR_C容值充放电引起的纹波:

ΔV_c = ΔI_L / (8 * f_sw * C_out)

因此,总纹波为:ΔV_ripple ≈ ΔV_esr + ΔV_c = (ΔI_L * ESR_C) + (ΔI_L / (8 * f_sw * C_out))

初始容值计算 (忽略ESR):

为简化,先估算最小容值:C_out_min_ripple > ΔI_L / (8 * f_sw * ΔV_ripple)关键:基于ESR要求计算:

在现代Buck电路中,ESR往往是纹波的主要来源。因此,ESR要求更为关键:ESR_max < ΔV_ripple / ΔI_L

举例:若 ΔV_ripple ≤ 50mV,ΔI_L = 2A,则需选用 ESR < 25mΩ 的电容。

步骤三:基于负载瞬态响应校验

瞬态要求往往决定了最终的电容值。

当负载发生阶跃变化 ΔI_out 时,在控制环路响应时间 t_response 内,全部电流差由输出电容提供/吸收。其所需电容的简化计算公式为:

C_out_min_transient > (ΔI_out * t_response) / ΔV_transient

t_response:控制环路响应时间(电压模式约1-3个开关周期,电流模式更短)。

比较:从步骤二和步骤三中,选取更大的电容值作为设计值。在现代应用中,瞬态要求通常是决定因素。

步骤四:选择电容类型与组合策略

这是将理论计算转化为实际元器件的关键一步,也是回答“为何要并联”的核心。

| 电容类型 | 优点 | 缺点 | 常见容值 | 角色 |

|---|---|---|---|---|

| 陶瓷电容 (MLCC) | ESR/ESL极低,高频性能好,体积小 | 容值小,有直流偏压效应 | 0.1μF, 1μF, 10μF, 22μF | 高频去耦,应对快速瞬变 |

| 聚合物电容 | 容值较大,ESR很低,无直流偏压,寿命长 | 成本高于电解电容 | 100μF, 220μF, 470μF | 中频滤波和储能,性能主力 |

| 电解电容 | 容价比高(单位容量成本低) | ESR高,寿命较短,ESL高 | 470μF, 1000μF | 低频储能,成本优先方案 |

并联的策略与逻辑:

降低ESR/ESL:并联后等效ESR和ESL显著降低,这是减小纹波最有效的方法。

构建宽频带低阻抗:不同电容擅长不同频段。大电容管低频,小MLCC管高频。并联后可在全频段保持低阻抗。

解决MLCC直流偏压:一个标称100μF的MLCC在12V电压下实际容值可能仅剩30μF。并联多个小容值电容(如10个10μF)是抵消偏压影响、获得准确容值的实用方法。

分散热应力与提高可靠性:将纹波电流分散到多个电容上,避免单个电容过热,提升系统寿命和 robustness。

步骤五:最终校验与其他考虑

RMS电流校验:流经电容的纹波电流有效值

I_C_rms ≈ ΔI_L / √12。所选电容的额定纹波电流必须大于此值,否则会过热损坏。电压额定值:电容额定电压需留有充足余量,一般为输出电压的1.2~1.5倍以上。

仿真验证:使用LTspice、PSIM等工具进行仿真,是验证设计、优化参数的必备环节。

4. 实战举例:常见的并联电容值

一个为处理器核心供电的Buck电路(输出1.2V@10A, f_sw=500kHz)的输出电容配置可能如下:

| 数量 | 容值 | 类型 | 角色与说明 |

|---|---|---|---|

| 2颗 | 100μF | 聚合物电容 | 主储能电容,提供能量缓冲,应对负载瞬变。 |

| 4颗 | 10μF | MLCC | 中频去耦,弥补聚合物电容的中高频阻抗,辅助滤波。 |

| 8颗 | 1μF | MLCC | 电源去耦,应放置在负载芯片周围,应对中高频电流需求。 |

| 12颗 | 0.1μF | MLCC | 高频去耦,滤除极高频率噪声,必须最靠近芯片电源引脚。 |

总计算容量 = (2 * 100μF) + (4 * 10μF) + (8 * 1μF) + (12 * 0.1μF) = 200 + 40 + 8 + 1.2 = 249.2μF

注意:总容值249.2μF只是一个参考数字。设计的精髓不在于此,而在于通过并联不同特性的电容,构建了一个从低频到高频的“低阻抗通道”。

5. 总结与关键要点

设计是权衡:输出电容设计是在纹波、瞬态、体积、成本之间的多次迭代与权衡。

双核心驱动:必须同时满足纹波和负载瞬态两种要求,并取更严格者。

并联是王道:并联不是为了简单堆高容值,而是为了降低ESR/ESL、构建宽频带响应和提高可靠性。

MLCC是高频关键:必须使用MLCC来应对高频噪声,并务必注意其直流偏压特性。

布局决定性能:尤其是0.1μF和1μF的小电容,离负载芯片越近越好,否则长走线引入的电感会使其高频优势尽失。