FPGA时序约束(五)--衍生时钟约束

前言

本文从衍生时钟的定义,它起到的作用来帮助大家理解衍生时钟约束的意义。同时也给出了具体的约束方法和实例帮助大家实际的使用。

衍生时钟是什么

衍生时钟是由FPGA内部的时钟管理单元(如MMCM、PLL)或普通逻辑(如寄存器)对主时钟(Primary Clock) 进行变换(分频、倍频、相位移动等)后所产生的新时钟。

来源:

1.时钟管理单元(MMCM/PLL):这是最常见、最可靠的方式。产生的是频率/相位精确的时钟。

2.RTL逻辑:通过寄存器对主时钟进行分频或门控产生。这种方式产生的时钟质量较差(容易产生毛刺、高时钟偏移),通常不推荐用于高速设计。

关键特性:衍生时钟的时序特性(周期、相位)完全依赖于其源时钟(Source Clock)。它不是独立的。

为什么必须约束衍生时钟

核心原因:为静态时序分析(STA)工具建立清晰的时钟派生关系模型。如果不约束,工具会将衍生时钟信号视为普通数据信号,而不是时钟。这将导致:

1.无法识别时钟树:工具不知道这个信号是时钟,不会为其分配低偏移的全局时钟资源(BUFG),导致时钟质量差。

2.时序路径缺失分析:由这个衍生时钟驱动的所有寄存器之间的路径,以及它与其它时钟域之间的路径,都会被标记为 unconstrained(未约束)而无法得到有效检查,从而隐藏了严重的时序违例风险。

3.错误的时序计算:即使工具识别出它是时钟,如果不告知其与主时钟的关系,工具也无法知道其准确的周期和边沿位置,计算出的时序结果毫无意义。

约束衍生时钟,就是明确地告诉STA工具:“这个信号是时钟,它是由那个主时钟通过某种方式产生的,请你按照这个关系去分析所有与之相关的时序路径。”

衍生时钟约束命令

基本语法:

create_generated_clock -name <generated_clock_name> \-source <source_clock_pin> \-divide_by <N> | -multiply_by <N> | -edges <edge_list> \[get_pins <generated_clock_pin>]-name:为衍生时钟命名。这个名字将用于后续的时序约束引用。

-source:这是最重要的参数! 它指定了衍生时钟的物理源点。这个点必须是主时钟直接驱动的物理引脚,例如:

PLL/MMCM的输入时钟引脚 [get_pins mmcm0/CLKIN]

PLL/MMCM的输出时钟引脚 [get_pins mmcm0/CLKOUT0](用于多级生成)

驱动衍生逻辑的寄存器时钟引脚 [get_pins clk_div_reg/C]

-divide_by/ -multiply_by:定义分频或倍频系数。例如,主时钟100MHz,-divide_by 2生成50MHz时钟。

-edges:最灵活的定义方式,通过主时钟的边沿列表来精确定义衍生时钟的波形。

-edges {1, 3, 5}表示衍生时钟的第一个上升沿对应主时钟的第一个边沿(上升沿),下降沿对应主时钟的第三个边沿(下降沿),下一个上升沿对应第五个边沿。

[get_pins]:指定衍生时钟的物理产生点。这同样是关键!

对于PLL/MMCM,是其输出引脚 [get_pins mmcm0/CLKOUT0]

对于RTL分频,是寄存器输出引脚 [get_pins clk_div_reg/Q]

GUI实现

像之前的主时钟约束一样,延时时钟也可以用GUI来实现。

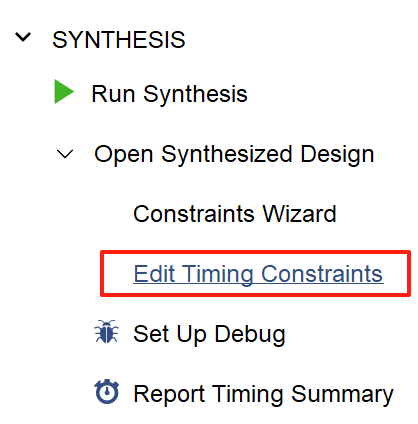

首先打开综合界面下的Edit Timing Constraints

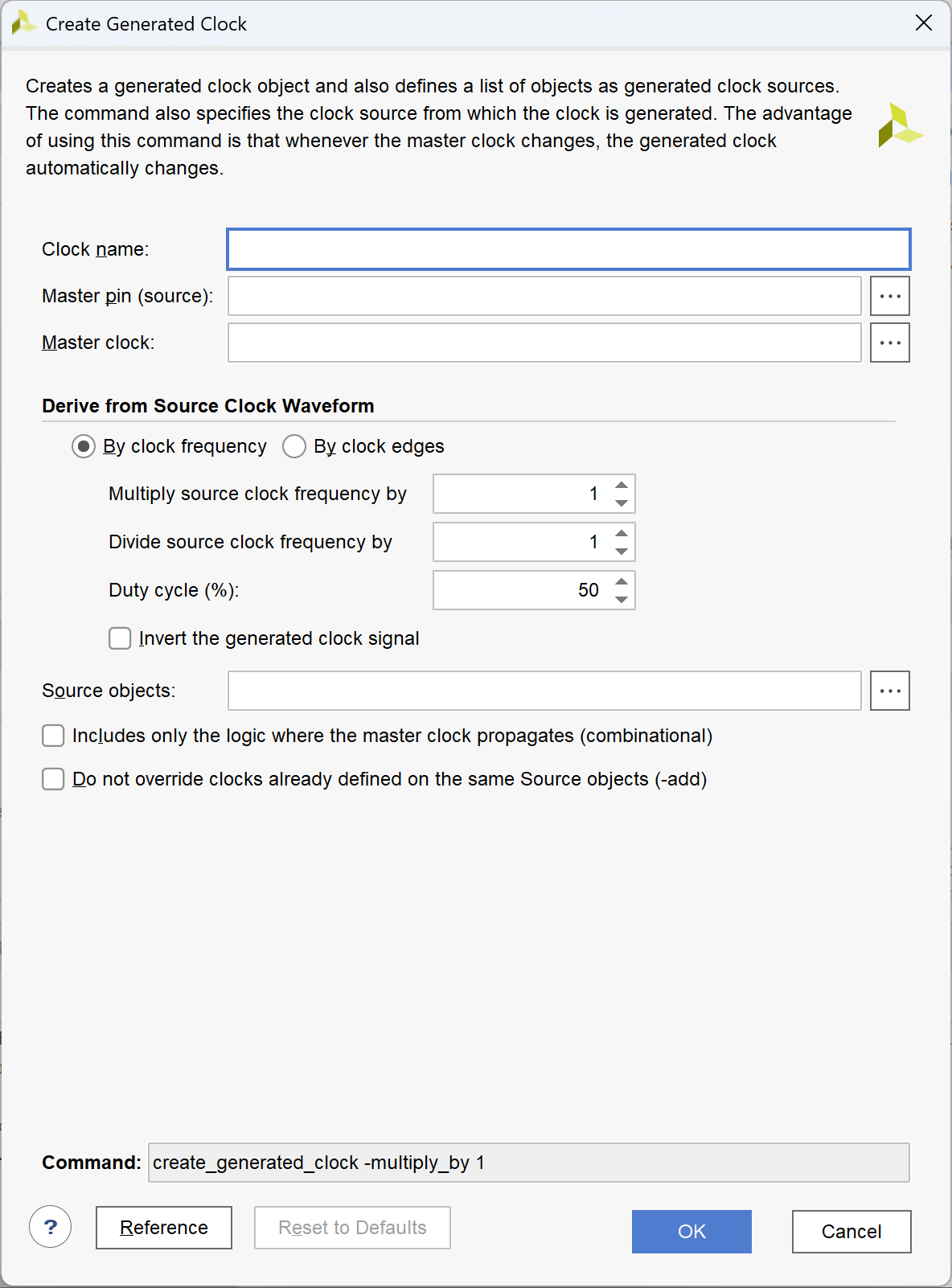

进去之后点击Create Generated Clock

图中的配置和约束命令是对应的,GUI可能会更加方便些。

衍生时钟约束实例

场景1:基础二分频时钟

主时钟 clk_100m (100MHz, 10ns period) 通过一个寄存器进行二分频,产生一个 50MHz 的时钟 clk_50m。

create_clock -period 10.000 -name clk_100m [get_ports clk_in]create_generated_clock -name clk_50m \-source [get_ports clk_in] \-divide_by 2 \[get_pins div_reg/Q]source: 指向原始时钟的源头clk_in端口。这是计算新时钟时序的起点。divide_by 2: 定义分频系数,频率变为主时钟的 1/2。[get_pins div_reg/Q]: 指定生成时钟的物理源点,即分频寄存器的输出引脚Q。工具会从这里开始传播新的时钟网络。

场景2:PLL 倍频时钟

使用芯片内部的 PLL 或 MMCM 硬核资源来产生一个更高频率的时钟。主时钟 clk_50m 输入到 PLL,PLL 产生一个倍频后的 200MHz 时钟 clk_200m 并从 clk_out1 引脚输出。

create_clock -period 20.000 -name clk_50m [get_ports clk_in]create_generated_clock -name clk_200m \-source [get_pins pll_inst/CLKIN] \-multiply_by 4 \[get_pins pll_inst/CLKOUT1]总而言之,衍生时钟约束是主时钟约束的延伸。它通过建立清晰的时钟派生树,将芯片内部的时钟生成逻辑纳入时序分析的范围,确保了整个设计时序分析的完整性和正确性。