自动驾驶中的传感器技术48——Radar(9)

本节开始介绍雷达前端算法,即雷达如何配置。

首先这里推荐两本书:FMCW Radar Design 和 Radar Signal Processing for Autonomous Driving

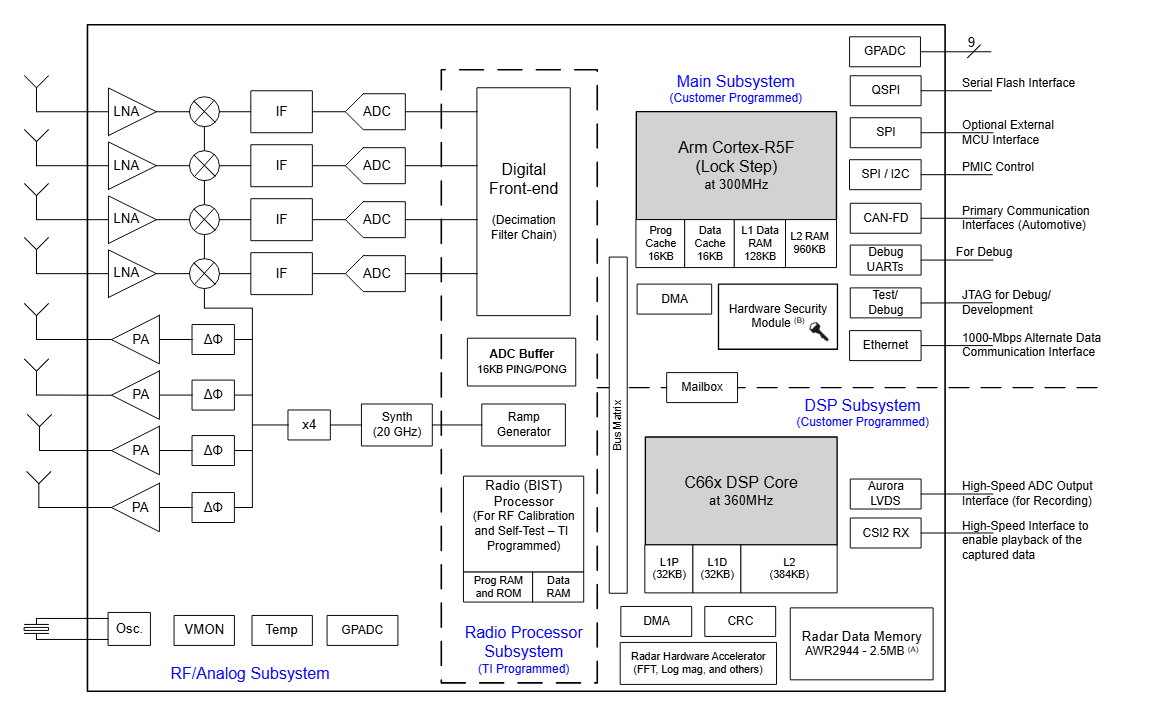

首先对雷达MMIC的技术指标进行相关论述(参数以AWR2944为例):

1、收发通道数

4T4R:各通道独立,影响水平测角和俯仰测角的虚拟阵规模

2、雷达频率范围

76~81GHz:影响了chirp调制的频率范围,从而影响最小距离分辨率,但是调频带宽越大,对后端处理要求约高

3、Tx Power

13.5dBm:LRR雷达的最远作用范围还是要考虑Tx的发射功率的

4、Rx Noise Figure

12dB:影响了最小接收灵敏度

5、1dB Compression Point

-10dBm:影响了最近距离下高反目标导致的雷达饱和

6、Phase Noise at 1MHz

76~77GHz:-96dBc/Hz

77~78GHz:-95dBc/Hz

影响近距离的大小目标区分

7、Per chirp configurable Tx phase shifter

6b,5.625deg

雷达编码波形调制能力

8、Phase shifter accuracy

±5°;±2°(calibrated):雷达DoA以及不同通道之间的相位一致性

9、Chirp Linerity

0.01%:如果Chirp信号存在非线性,频率变化不再严格线性,这将导致目标回波信号的“拍频”(beat frequency)不再恒定,从而影响距离分辨率,甚至可能导致目标位置的误判或“假目标”;在多目标场景中,雷达需要通过多个Chirp信号的组合来区分不同目标。如果Chirp信号的线性度不理想,可能会导致目标之间的相互干扰,从而影响目标的准确识别和定位

10、Advanced chirp support

2048 unique chirp

11、Max IF

15MHz:ADC的采样率决定了中频信号的最大带宽,从而限制了雷达的性能。中频带宽越宽,距离分辨率越高

12、Max real/complex sampling rate

37.5Msps(real):最大探测距离是FMCW雷达的一个重要性能指标,它受到ADC采样率的限制。ADC采样率越高,能够处理的中频信号带宽越宽,从而能够探测更远距离的目标。然而,过高的采样率会增加数据处理的复杂性和系统成本,因此需要在性能和成本之间进行权衡

13、ADC bits

12bit ,ENOB 11.5bit:ADC的分辨率(位宽)直接影响信号处理的质量。ADC的分辨率不足会导致量化噪声增加,降低信号处理质量,尤其是在存在强干扰反射的情况下。例如,低分辨率的ADC可能导致弱目标被掩盖,而高分辨率的ADC虽然能提高灵敏度,但会增加计算负担和成本。

14、Processor

DSP C66x 360MHz;MCU ARM R5F LOCKSTEP 300MHz;Hardware Accelerator HWA2.1 300MHz

15、Hardware Accelerator

FFT:up to 2048, radix-3 supported

CFAR:CA/OS/Local Maxim

Statistics:1D Sum,1D Max,Histogram,CDF,2D Max

DoA:FFT with zero insertion

Windowing:complex widdow

Memory Compression:25/33/50/62.5%

16、On chip memory

4MB

17、Safety

ASIL-B

18、Security

HSM-FULL

19、Temperature

-40~140