HDLBits 解题更新

HDLBits 解题更新

- 题目名称

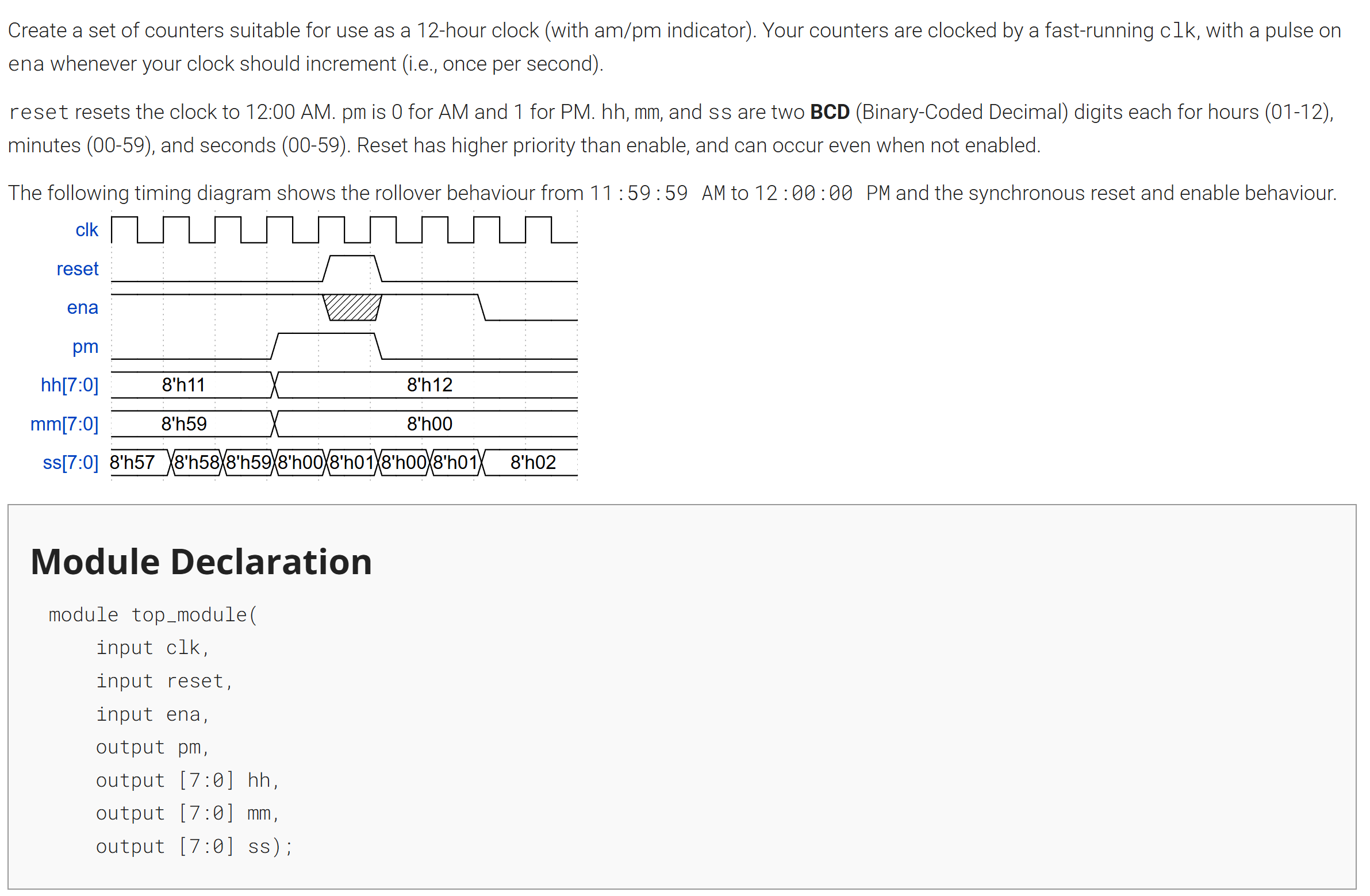

- Count clock

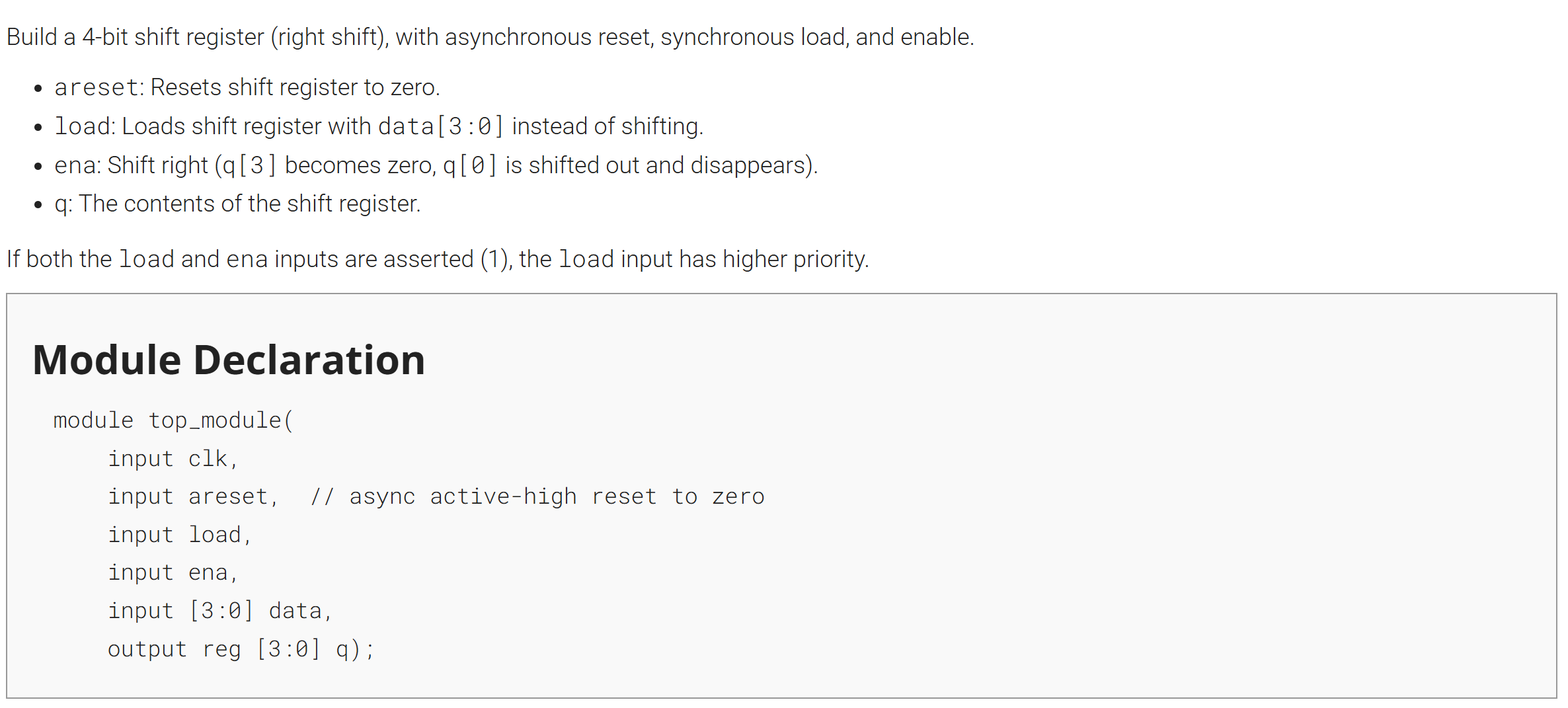

- Shift4

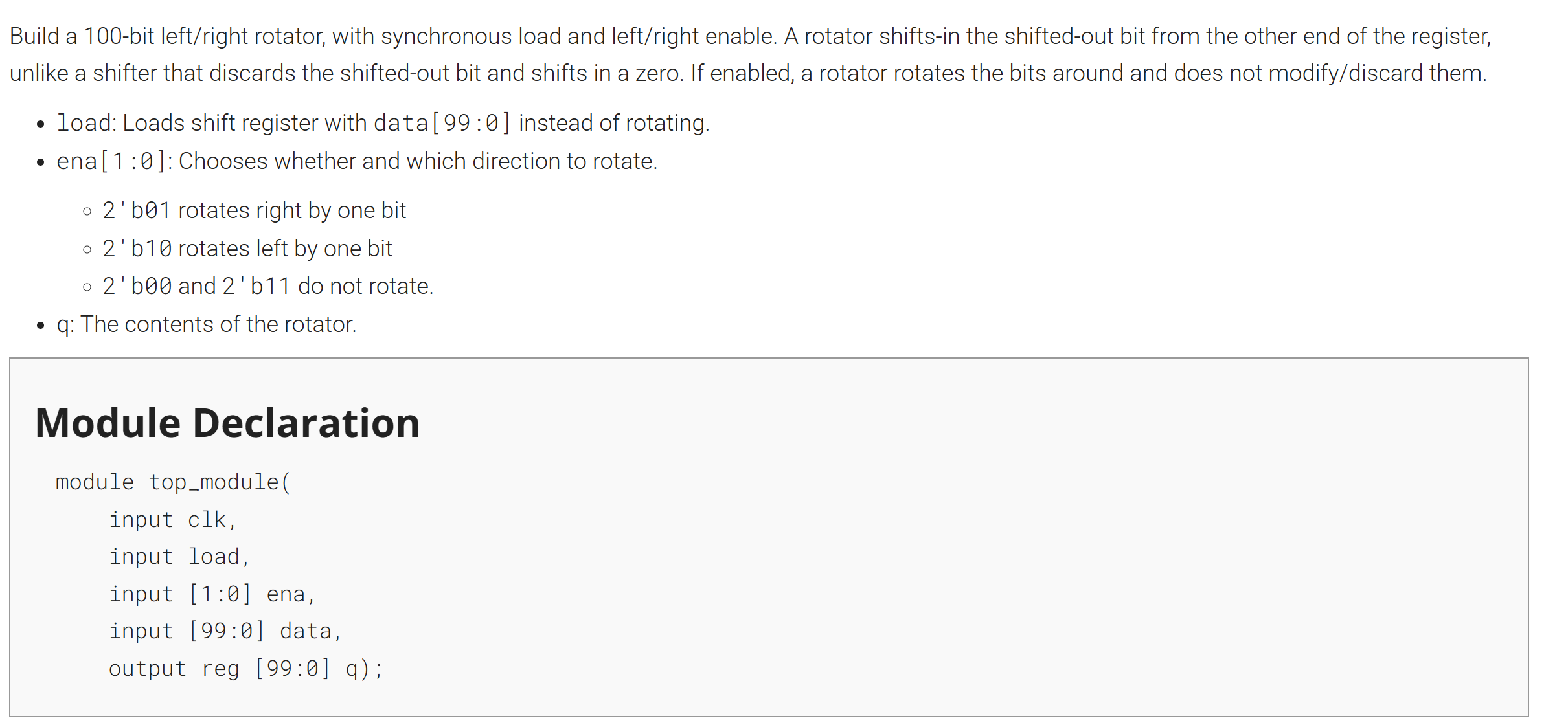

- Rotate100

题目名称

Count clock

module top_module(input clk,input reset,input ena,output pm,output [7:0] hh,output [7:0] mm,output [7:0] ss); wire [7:0] q1,q2,q3;wire ena_m,ena_h;wire pm_in;bcd_h bcd1(.clk(clk),.reset(reset),.ena(ena_h),.hh(q1),.pm(pm_in));bcd_ms bcd2(.clk(clk),.reset(reset),.ena(ena_m),.ms(q2));bcd_ms bcd3(.clk(clk),.reset(reset),.ena(ena),.ms(q3));assign ena_m = (q3 == 8'h59) && ena;assign ena_h = (q2 == 8'h59) && (q3 == 8'h59) && ena;assign pm = pm_in;assign hh = q1;assign mm = q2;assign ss = q3;endmodulemodule bcd_h(input clk,input reset,input ena,output [7:0] hh, // BCD tens[7:4], ones[3:0]output pm // 0=AM, 1=PM

);reg [7:0] q; // 1..12(二进制)reg pm1;always @(posedge clk) beginif (reset) beginq <= 8'd12; // 12:00:00 AMpm1 <= 1'b0; // AMend else if (ena) beginif (q == 8'd11) begin// 11 -> 12 时翻转 AM/PMq <= 8'd12;pm1 <= ~pm1;end else if (q == 8'd12) begin// 12 -> 1(不翻转)q <= 8'd1;end else begin// 1..10 -> +1q <= q + 8'd1;endendend// 输出 BCD(各取低4位,避免位宽变成16位)wire [3:0] tens = q / 10;wire [3:0] ones = q % 10;assign hh = {tens, ones};assign pm = pm1;

endmodulemodule bcd_ms(input clk,input reset,input ena,output [7:0] ms

);reg [7:0] q;always @(posedge clk) beginif(reset)q<=8'd0;else if(ena & q==8'd59)q<=8'd0;else if(ena & q!=8'd59)q<=q+1; endwire [3:0] tens = q / 10;wire [3:0] ones = q % 10;assign ms = {tens, ones};

endmodule

撰写思路:

(1)一开始不要管pm的问题,专注于实现clock功能;

(2)写完后发现题目要求的8位寄存器是通过高四位和第四位分别表示十进制的十位和个位,所以在不改变我原有的计数结构的情况下,最后的模块的输出加了转换;

Shift4

module top_module(input clk,input areset, // async active-high reset to zeroinput load,input ena,input [3:0] data,output reg [3:0] q); always @(posedge clk or posedge areset) beginif(areset)q<=4'b0;else if(load)q<=data;else if(ena)q<= q>>1;end

endmodule注意同步reset和异步reset的区别,寄存器右移还可以有其他表示方法:

module top_module(input clk,input areset,input load,input ena,input [3:0] data,output reg [3:0] q);// Asynchronous reset: Notice the sensitivity list.// The shift register has four modes:// reset// load// enable shift// idle -- preserve q (i.e., DFFs)always @(posedge clk, posedge areset) beginif (areset) // resetq <= 0;else if (load) // loadq <= data;else if (ena) // shift is enabledq <= q[3:1]; // Use vector part select to express a shift.endendmoduleRotate100

module top_module(input clk,input load,input [1:0] ena,input [99:0] data,output reg [99:0] q); always @(posedge clk) beginif(load)q<=data;else if (ena ==2'b01)q<={q[0],q[99:1]};else if (ena == 2'b10)q<={q[98:0],q[99]};end

endmodule学会了之前移位寄存器的拼接方法