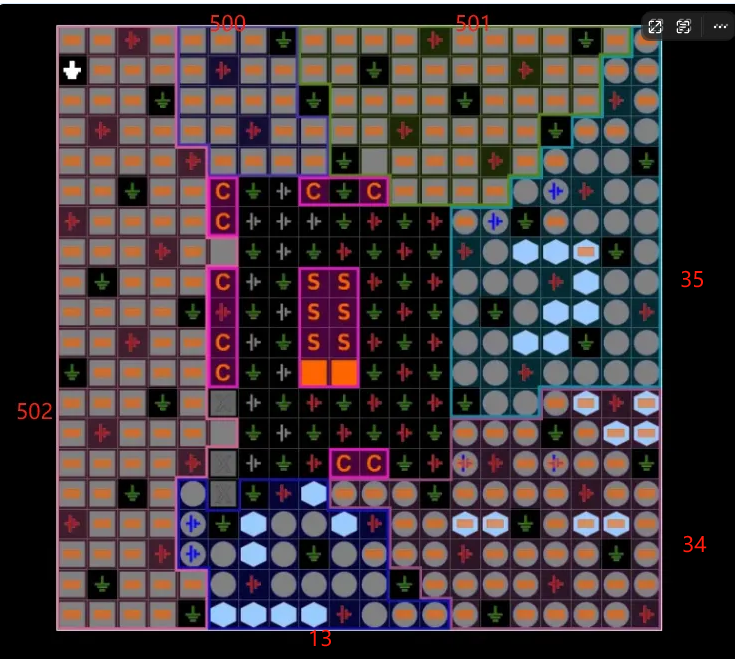

ZYNQ7020 Bank划分

简单来说,Bank0, Bank1, Bank2, Bank3 是 Zynq 芯片架构上的“逻辑功能分区”,而 Bank500, 501, 502, 33, 34, 35, 13, 14 等是芯片物理引脚布局上的“物理电气分组”。

它们之间的关系是映射和包含的关系。下面我为你详细解释:

1. 逻辑功能分区 (Bank 0, 1, 2, 3)

这源自Zynq-7000的芯片设计架构。Zynq本质上是两个主要部分在一个芯片上的融合:

- 处理系统 (PS - Processing System): 即双核ARM Cortex-A9及其相关外设(如DDR控制器、外设控制器等)。

- 可编程逻辑 (PL - Programmable Logic): 即传统的FPGA逻辑部分。

根据这个架构,芯片的I/O Bank被分为了四大组:

逻辑Bank | 所属部分 | 主要功能与特点 |

Bank 0 | PS | 专用MIO引脚。直接连接到PS部分的外设,如UART, SPI, I2C, USB, SDIO等。这些引脚的功能是固定的,用户只能在有限范围内通过软件配置复用。 |

Bank 1 | PS | 专用MIO引脚。同上,是PS外设的另一部分引脚。 |

Bank 2 | PS | 专用MIO引脚。同上,是PS外设的另一部分引脚。 |

Bank 3 | PL | EMIO 和 PL 引脚。这个Bank比较特殊,它位于PS端,但专门用于通过EMIO方式将PS信号路由到PL端,或者连接PS和PL之间的专用接口(如AXI GP端口)。 |

小结: Bank 0, 1, 2, 3 是从PS的角度来看的,主要用于PS的配置和PS外设的连接。

2. 物理电气分组 (Bank 500, 501, 502, 13, 33, 34, 35...)

这源自FPGA的物理设计。为了管理不同的I/O电气标准(如LVCMOS、LVDS、HSTL等)和电压(如1.8V, 2.5V, 3.3V),FPGA的引脚被分成了多个物理Bank。

- 每个物理Bank有独立的VCCIO供电引脚。同一个物理Bank内的所有引脚必须使用相同的电压标准。

- 这套编号系统是所有Xilinx 7系列FPGA(包括Artix, Kintex, Virtex, Zynq)通用的。

- 对于Zynq-7020芯片,其物理Bank编号通常包括:

- Bank 500, 501, 502: 这三个Bank对应的是PS部分的MIO引脚。

- Bank 13, 14, 33, 34, 35: 这些是PL部分的通用Bank。你的Zynq-7020具体有多少个PL Bank取决于封装型号(如CLG400, CLG484等)。

3. 两者的对应关系(核心答案)

现在我们把这两套系统联系起来:

- PS MIO Banks (Bank 0, 1, 2)

- 逻辑Bank 0 的引脚,在物理上属于 Bank 500。

- 逻辑Bank 1 的引脚,在物理上属于 Bank 501。

- 逻辑Bank 2 的引脚,在物理上属于 Bank 502。

- 这就是为什么你总看到Bank500/501/502,它们就是PS的MIO引脚的物理编号。

- PS-PL接口 Bank (Bank 3)

- 逻辑Bank 3 比较特殊。它没有自己独立的物理Bank。

- 逻辑Bank 3的EMIO信号,在物理上是通过PL端的物理Bank(如Bank 13, 33, 34, 35等) 引出的。

- 当你使用EMIO功能时(例如将PS的GPIO通过EMIO连接到PL的引脚上),你实际上是在配置逻辑Bank 3,但最终需要在XDC约束文件中使用物理Bank(如Bank 35)来分配具体的引脚位置和电气标准。

- PL Banks

- 纯PL的逻辑(你的FPGA设计)使用的引脚,只属于物理Bank,如 13, 14, 33, 34, 35 等。

- 它们没有 0, 1, 2, 3 这样的逻辑Bank编号。对于PL部分,我们只关心物理Bank编号。

总结与类比

逻辑/功能视角 (Zynq架构) | 物理/电气视角 (FPGA布局) | 说明 |

PS Bank 0 | Physical Bank 500 | MIO引脚,用于PS外设 |

PS Bank 1 | Physical Bank 501 | MIO引脚,用于PS外设 |

PS Bank 2 | Physical Bank 502 | MIO引脚,用于PS外设 |

PS Bank 3 | 通过 PL Physical Banks | EMIO信号,通过PL的引脚引出 |

PL | Physical Bank 13, 14, 33, 34, 35... | 纯FPGA逻辑引脚 |

一个简单的类比:

- 把Zynq芯片想象成一栋大楼。

- 逻辑Bank (0,1,2,3) 像是按功能划分的部门:销售部(Bank0)、市场部(Bank1)、财务部(Bank2)。还有一个对外合作部(Bank3),它自己没有独立的办公室。

- 物理Bank (500,501,502,13,35...) 像是大楼里实际的物理楼层:500楼、501楼、502楼、13楼、35楼。

- 销售部、市场部、财务部分别独占500、501、502楼。

- 对外合作部没有自己的楼,它的员工在13楼和35楼办公。

- 13楼和35楼除了有对外合作部的人,还有其他纯PL部门的员工。

在实际应用中的体现:

- 你在Zynq的PS配置界面(如Vivado中的Block Design或Xilinx SDK)配置MIO/EMIO时,操作的是逻辑Bank (0,1,2,3)。

- 当你在Vivado中为设计添加引脚约束(XDC文件)时,你必须使用物理Bank编号,例如:

set_property PACKAGE_PIN F17 [get_ports {my_led}](F17是物理引脚号)set_property IOSTANDARD LVCMOS33 [get_ports {my_led}](这个电气标准由该引脚所在的物理Bank的VCCIO电压决定)