江科大《STM32入门教程》

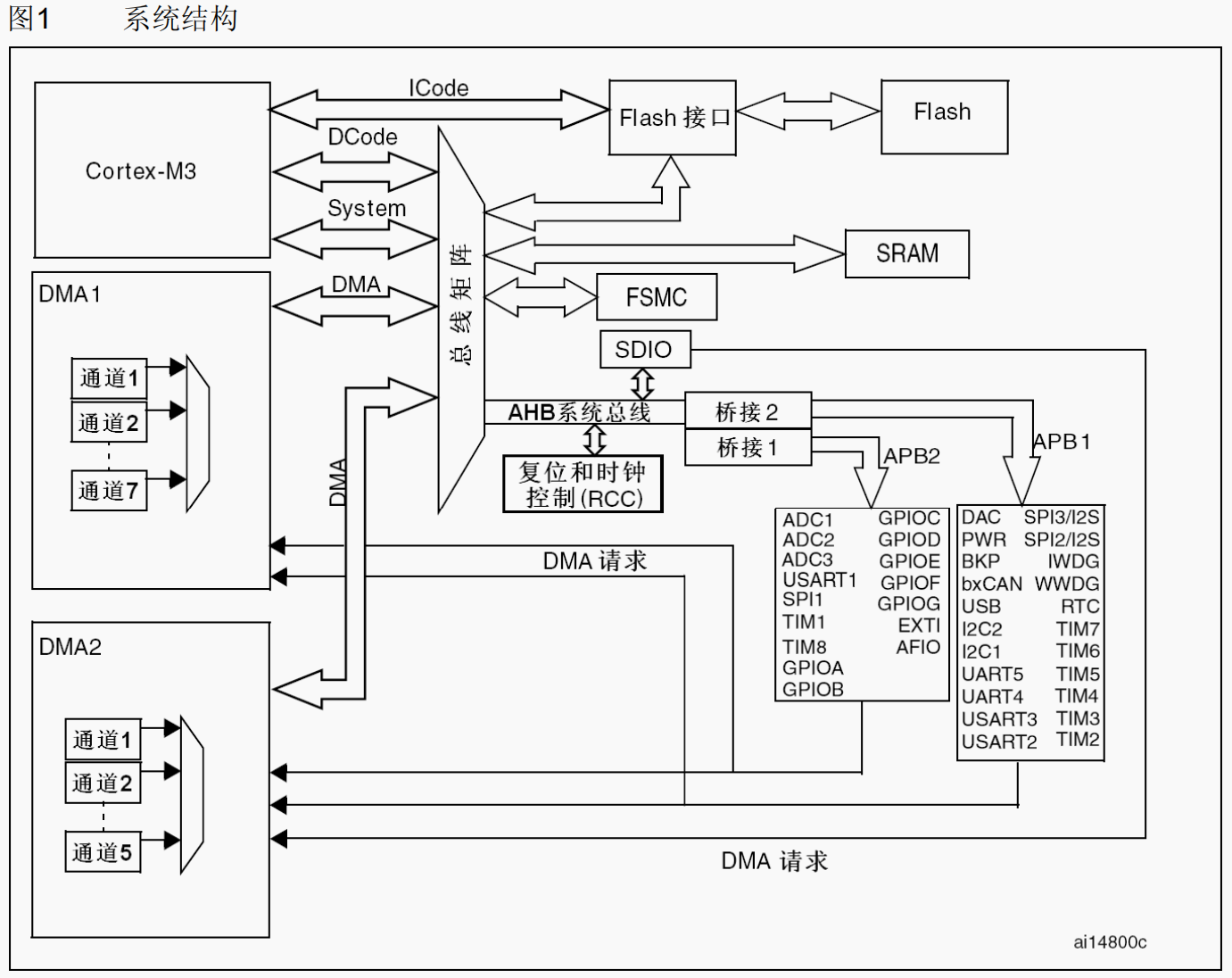

STM32主系统主要由四个驱动单元和四个被动单元构成。

四个驱动单元是:内核DCode总线;系统总线;通用DMA1;通用DMA2;

四被动单元是:AHB到APB的桥:内部FIASH闪存:内部SRAM:FSMC;

具体解释:

①ICode总线:该总线将M3内核指令总线和闪存指令接口相连,指令的预取在该总线上面完成。

②DCode总线:该总线将M3内核的DCode总线与闪存存储器的数据接口相连接,常量加载和调试访问在该总线上面完成。

③系统总线:该总线连接M3内核的系统总线到总线矩阵,总线矩阵协调内核和DMA间访问。

④DMA总线:该总线将DMA的AHB主控接口与总线矩阵相连,总线矩阵协调CPU的DCode 和DMA 到 SRAM,闪存和外设的访问。

⑤总线矩阵:总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法。

⑥AHB/APB桥:这两个桥在AHB和2个APB总线间提供同步连接,APB1操作速度限于36MHz,APB2操作速度全速。

3)复位电路:复位目的是将系统强制定位在一个可知状态。要求:准确,可靠

STM32F10xxx支持三种复位形式,分别为:

①系统复位

除了时钟控制器的RCC_CSR寄存器中的复位标志位和备份区域中的寄存器以外,系统复位将复位所有寄存器至它们的复位状态。当发生以下任一事件时,产生一个系统复位:

1、NRST引脚上的低电平(外部复位)

2、窗口看门狗计数终止(WWDG复位)

3、独立看门狗计数终止(IWDG复位)

4、软件复位(SW复位)

5、低功耗管理复位

②电源复位

当以下事件中之一发生时,产生电源复位:

1、上电/掉电复位(POR/PDR复位)

2、从待机模式中返回

3、电源复位将复位除了备份区域外的所有寄存器。

③备份区域复位。

备份区域拥有两个专门的复位,它们只影响备份区域。

1、软件复位,备份区域复位可由设置备份域控制寄存器(RCC_BDCR))中的BDRST位产生。

2、在VDD和VBAT两者掉电的前提下,VDD或VBAT上电将引发备份区域复位。

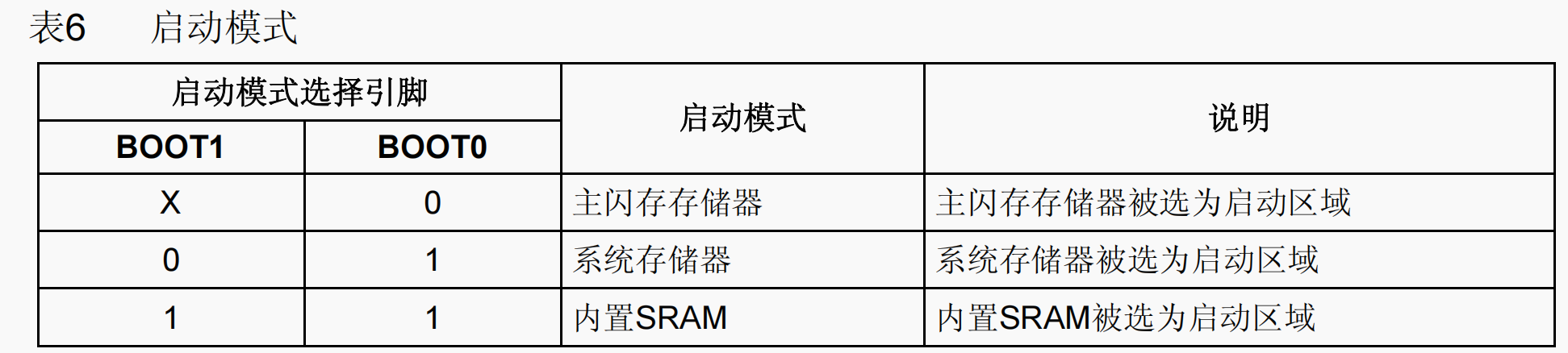

3 GPIO通用输入输出口

3.1 GPIO 简介

在每个GPIO模块内,组要包含了寄存器和驱动器,寄存器就是一段特殊的存储器,内核可以通过APB2总线对寄存器进行读写, 这样就可以完成输出电平和读取电平的功能了,寄存器的每一位对应一个引脚,其中,输出寄存器写1,对应的引脚就会输出高电平,写0就会输出低电平,输入寄存器读取为1,就证明对应的端口目前是高电平,读取为0,就是低电平

因为STM32是32位单片机,所以STM32内部的寄存器都是32位的,但这个端口只有16位,所以这个寄存器只有低16位对应的有端口,高16位是没有用的;

驱动器是用来增加信号的驱动能力,寄存器只负责存储数据, 如果要进行点灯这样的操作,还是需要驱动器来负责增大驱动能力。

3.2 GPIO 位结构图

GPIO位结构图如下所示,左边三个就是寄存器,中间部分是驱动器,右边是某一个IO口的引脚。整体结构可以分为两个部分,上面是输入部分,下面是输出部分

施密特触发器的作用:是对输入电压进行整形。它的执行逻辑是:如果输入电压大于某一阈值,输出就会瞬间升为高电平,如果输入电压小于某一阈值,输出就会瞬间降为低电平。

施密特触发器的特点是具有滞后特性的数字传输门,主要用于波形整形、变换、比较、鉴幅等。它的抗干扰能力在各类比较器中首屈一指,能有效地抑制由输入信号或外部干扰引起的微小变化。施密特触发器的滞回特性,即具有惯性,使其在电路状态转换时,通过电路内部的正反馈过程,使输出电压边沿变得很陡,从而将边沿变化缓慢的信号波形整形为边沿陡峭的矩形波,同时也能有效地清除矩形脉冲信号高、低电平上的噪声。

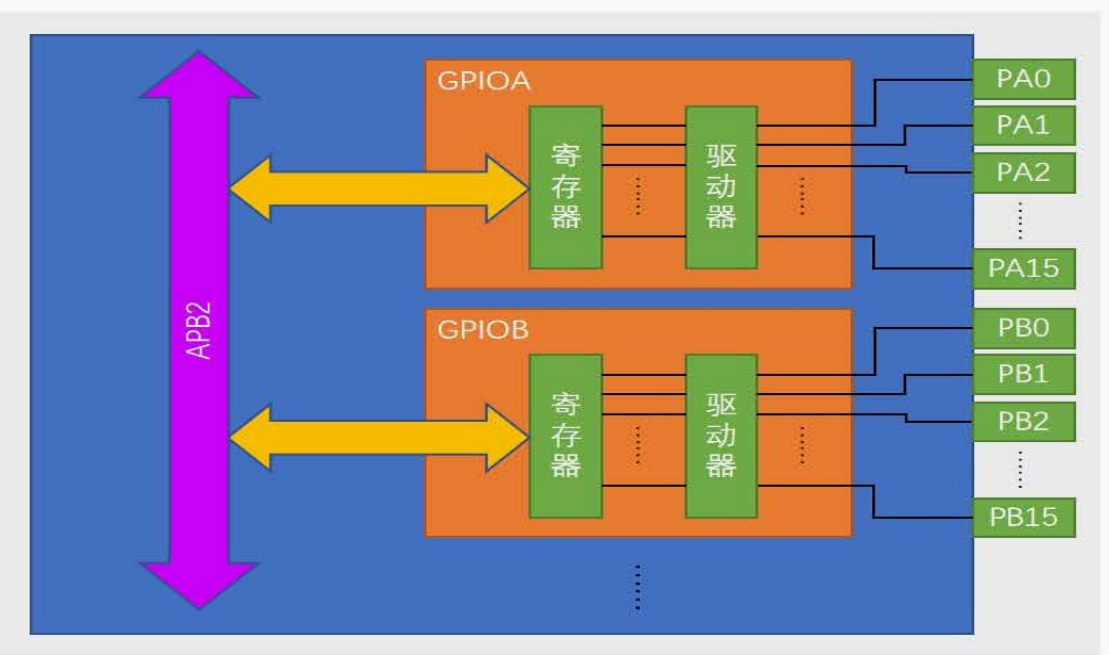

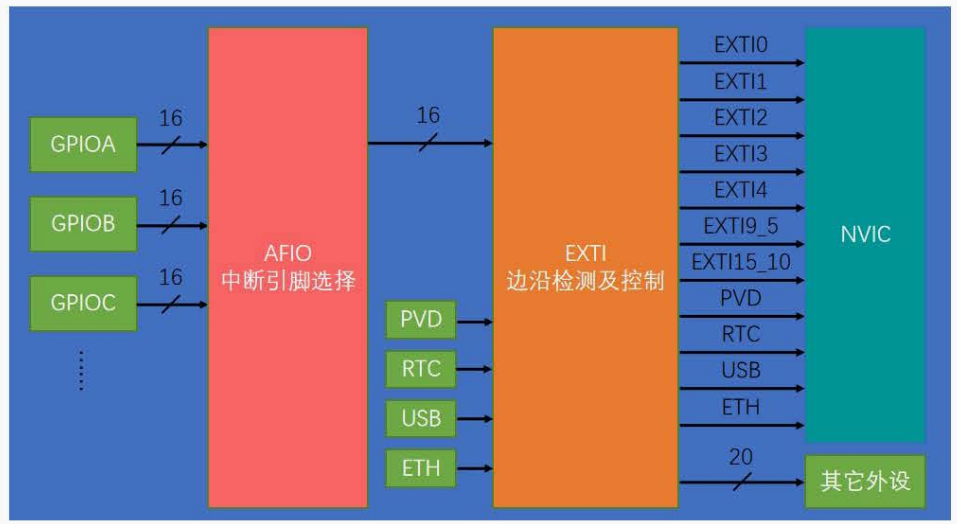

5.4 EXTI 简介

- 支持的触发方式:上升沿/下降沿/双边沿/软件触发

- 支持的GPIO口:所有GPIO口,但相同的Pin不能同时触发中断。(比如PA0和PB0

不能同时使用,智能选一个作为中断引脚;所以如果有多个中断引脚要选择不同的pin引脚,

比如PAO和PA1、PB3就可以) - 通道数:总共有20个中断线路。16个GPIO_Pin(对应GPIOpin0到15,是外部中断

的主要功能),外加PVD输出、RTC闹钟、USB唤醒、以太网唤醒(这4个中断线路,是

因为外部中断有个功能是从低功耗模式的停止模式下唤醒STM32;对于PVD电源电压检

测,当从电源从电池过压恢复时就需要PVD借助一下外部中断的退出停止模式;对于RTC

闹钟来说,有时候为了省电,RTC定一个闹钟之后,STM32回进入停止模式,等到闹钟响

的时候再唤醒,这叶需要借助外部中断,剩余USB唤醒、以太网唤醒也是类似的作用) - 触发响应方式:中断响应(引脚电平触发中断,申请中断,让CPU执行中断函数)/

事件响应(不会触发中断,而是触发别的外设操作,属于外设之间的联合工作。外部中断的

信号不会通向CPU而是通向其它外设,用来触发其它外设的操作,比如触发ADC转换、

触发

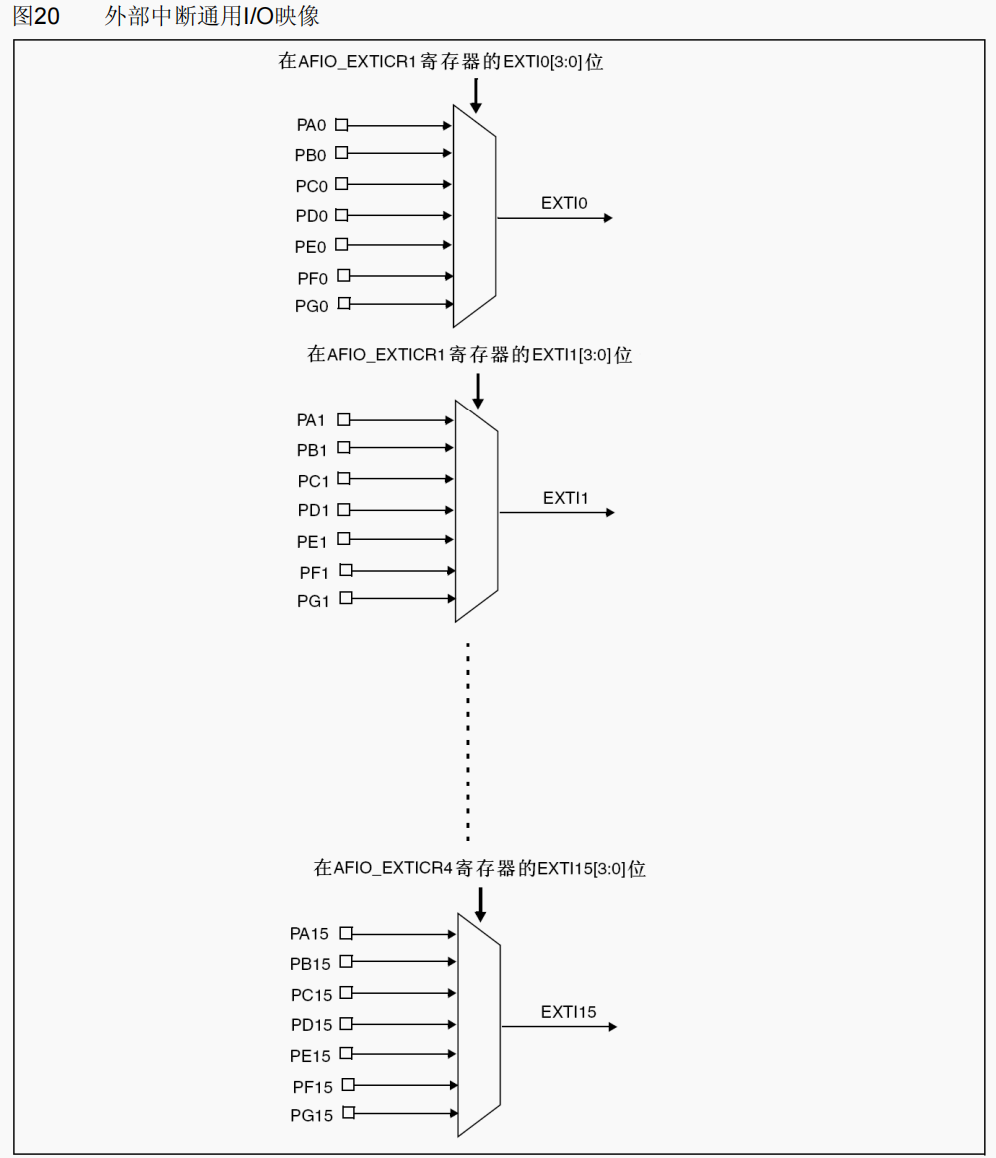

EXTI基本结构:

AFIO复用IO口内部电路:

内部电路就是一系列的数据选择器,如下图的最上面输入是PA0\PB0\PC0等尾号都是0,

然后通过数据选择器最终选择一个,连接到EXTI0上,上面写的文字是说配置这个寄存器

的哪一个位就可以决定选择哪一个输入,图中后面部分内容都雷同。

AFIO主要用于引脚复用功能的选择和重定义(也就是数据选择器的作用)。在STM32

中,AFIO主要完成两个任务:复用功能引脚重映射(就是最开始提到的引脚定义表,当想

把默认复用功能换到重定义功能时,就是用AFIO来完成的,这也是AFIO的一大主要功能)

中断引脚选择。

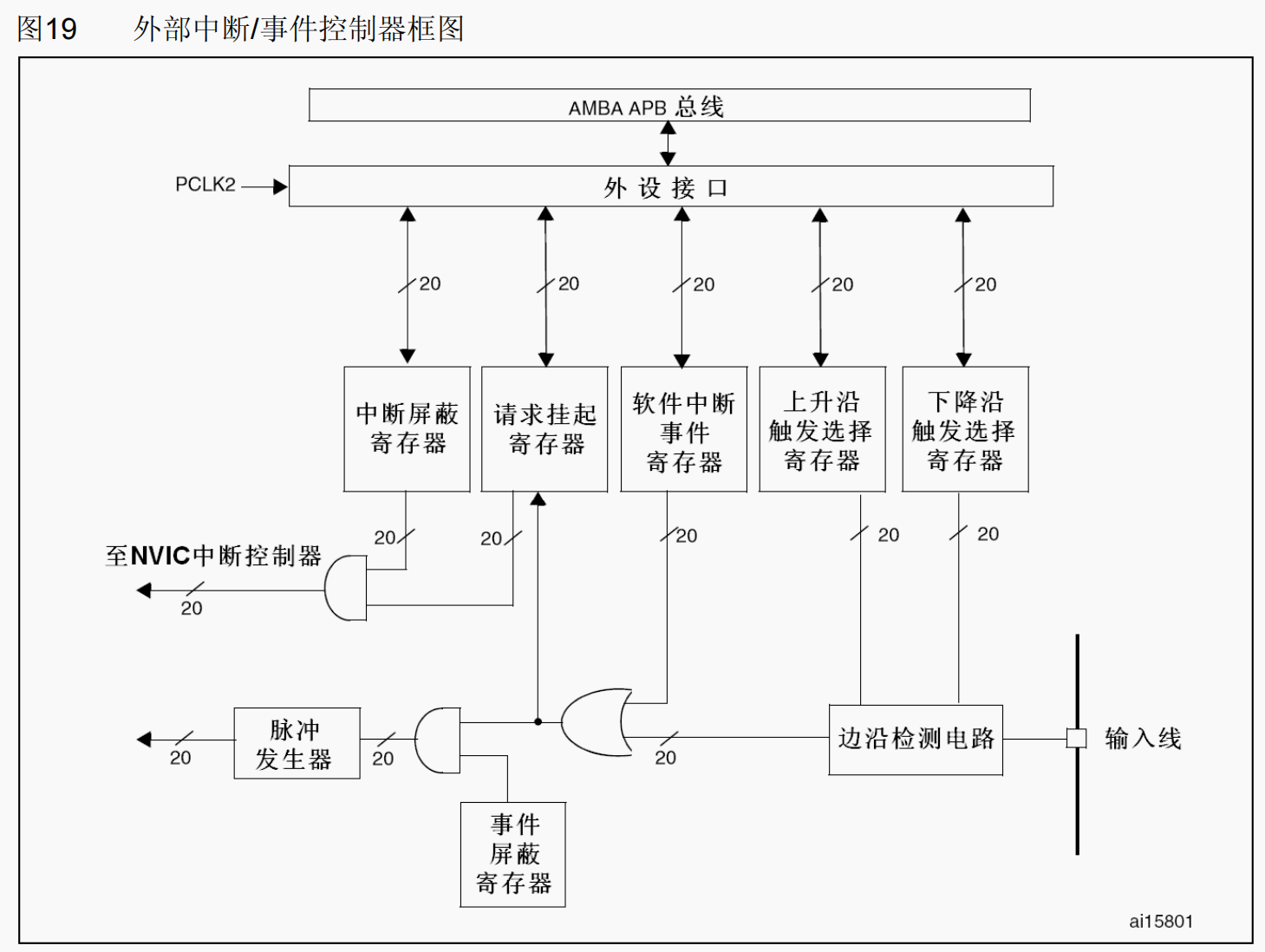

EXTI框图:

(脉冲发生器就是给一个电平脉冲,用来触发其它外设的动作)

EXTI项目应用

- 1)对射式红外传感器

- 2)旋转编码器计次

6 TIM定时器

6.1TIM定时器简介

16位计数器、预分频器、自动重装寄存器的时基单元,在72MHz计数时钟下可以实现

最大59.65s的定时。

- 定时器的计数频率 = 时钟频率/(PSC+1)

- 最大定时时间 = (ARR+1)/定时器的计数频率

- 即,最大定时时间 = (ARR+1)*(PSC+1)/时钟频率

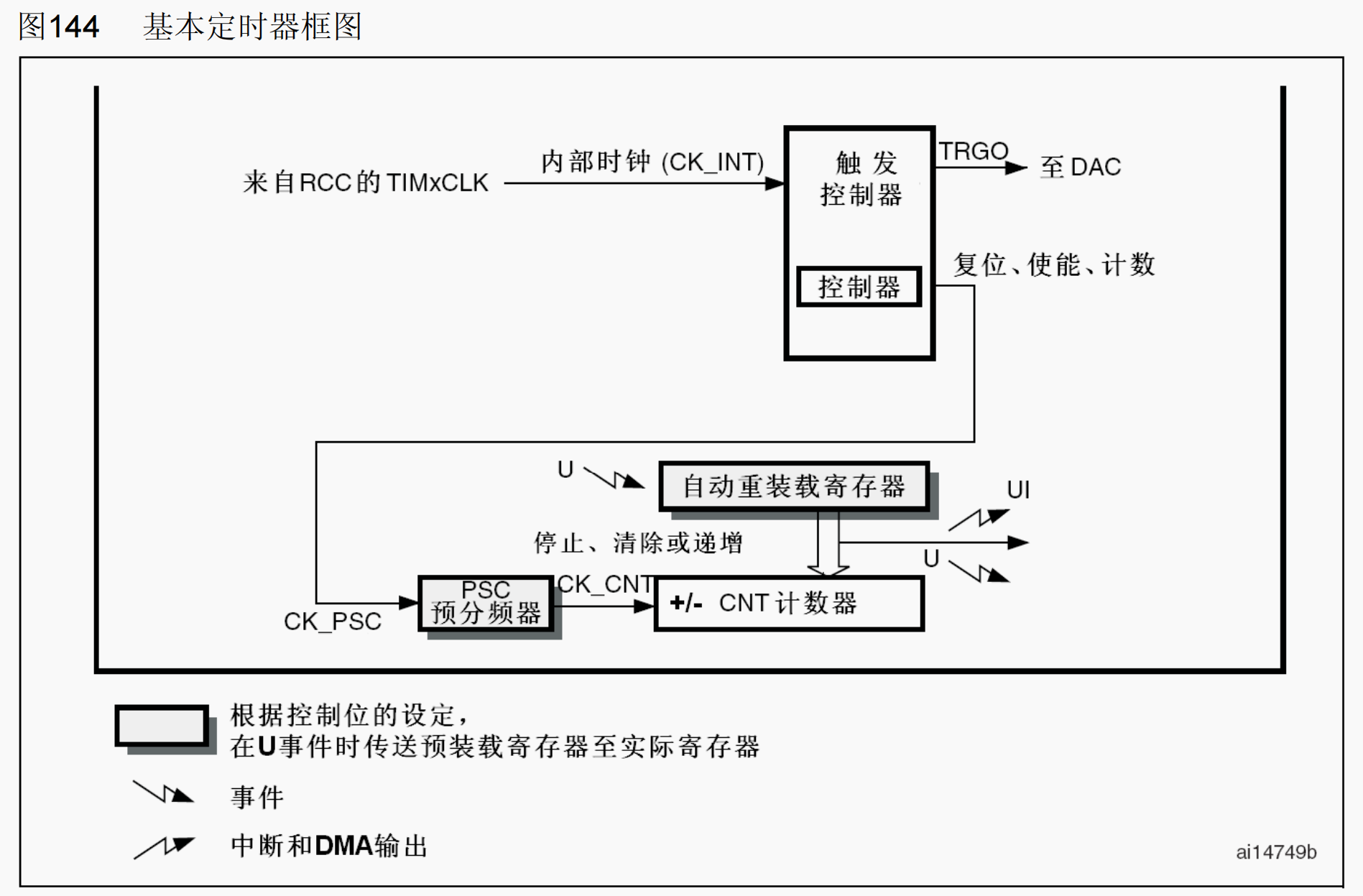

6.2基本定时器

基本定时器框图如下:

上图中下面三个部分构成了最基本的计数计时电路,这一块电路就叫做时基单元。时基单元:预分频器(PSC)、自动重装载寄存器(ARR)、计数器(CNT)。

总结定时器产生中断的全部流程:从基准时钟到预分频器再到计数器,计数器计数自增,同时不断地与自动重装寄存器进行比较,值相等时,即计时时间到,这时就会产生一个更新中断和更新事件,CPU响应更新中断,就完成了我们定时中断的任务了。

如上图所示,有两个箭头,其中向上的折线箭头,就代表这里会产生中断信号,像这种计数值等于自动重装值产生的中断,叫做“更新中断”;

向下的折线箭头,代表的是产生一个事件,这里对应的事件就叫做“更新事件”,更新事件不会触发中断,但可以触发内部其它电路的工作。

6.2.2主模式触发DAC的功能

主模式触发DAC的功能是利用 STM32定时器的主从触发模式来减少 CPU负担。 在主模式下,定时器的更新事件会直接触发DAC的转换,而无需通过中断手动触发。这样,定时器的更新事件通过TRGO(Trigger Out)输出连接到DAC,自动触发DAC输出波形,避免了频繁中断对主程序的干扰,实现了硬件自动化操作。

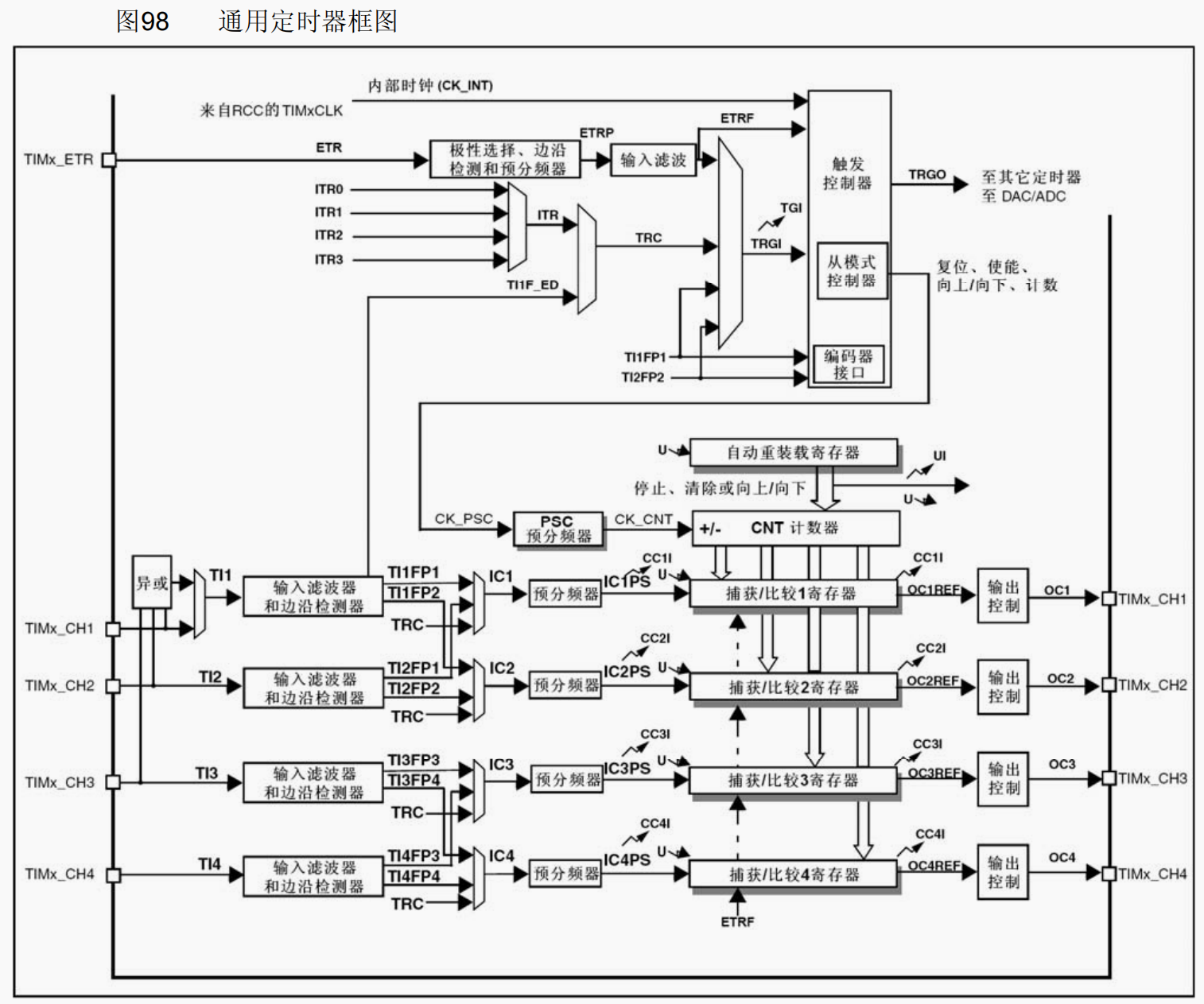

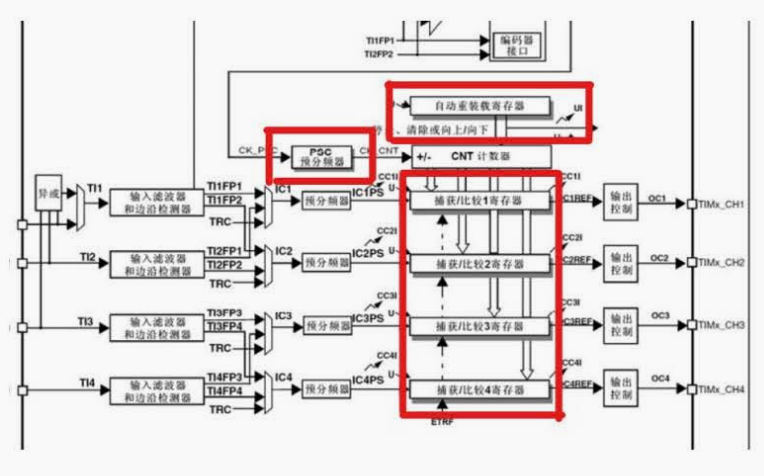

6.3通用定时器

6.3.1通用定时器与基本定时器异同

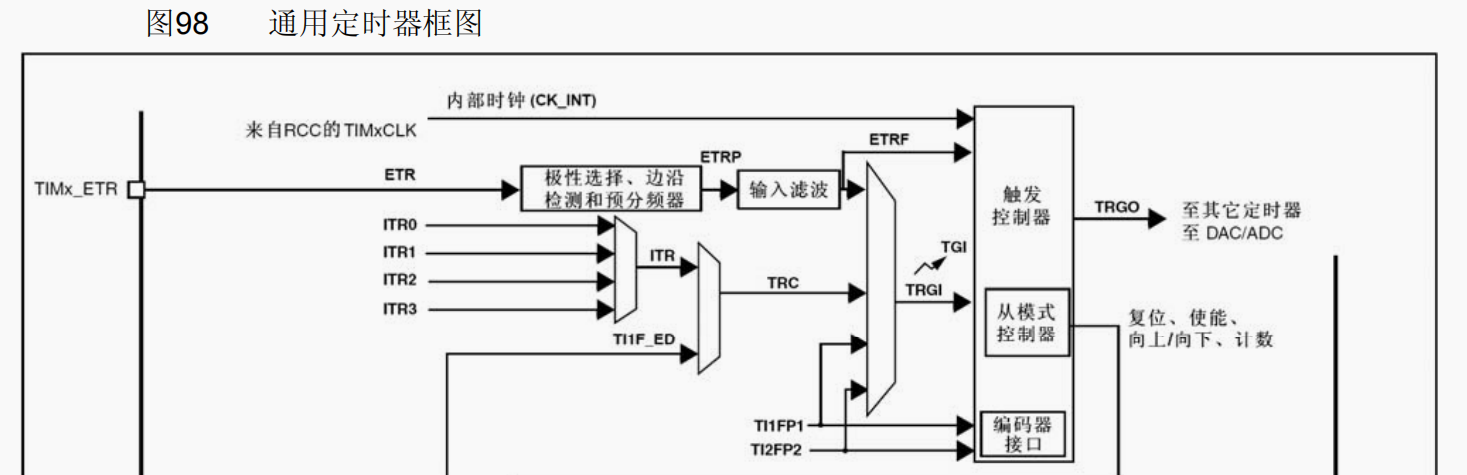

基本定时器只支持向上计数模式,最常用的还是向上计数模式,而 通用定时器和高级定时器支持向上计数、向下计数和中央对齐模式。 向下计数模式从重装值开始递减,减到0时重新加载;中央对齐模式则先向上计数到重装值,再向下计数到0,交替进行,申请中断并循环。通用定时器框图,如下所示:

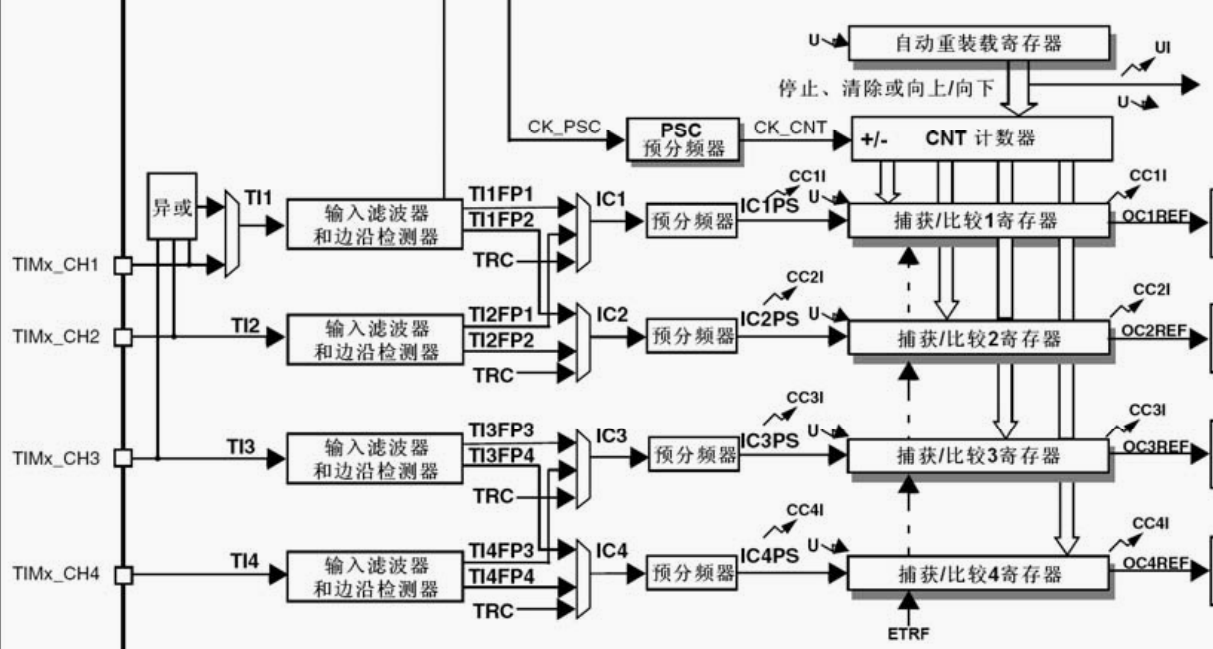

6.3.2内外时钟源选择功能

如下,是内外时钟源选择和主从触发模式的结构。

内外时钟源选择:对于基本定时器,定时只能选择内部时钟,也就是系统频率72MHz;对于通用定时器,时钟源可以选择内部时钟或者外部时钟.

外部时钟的选择有如下四种:

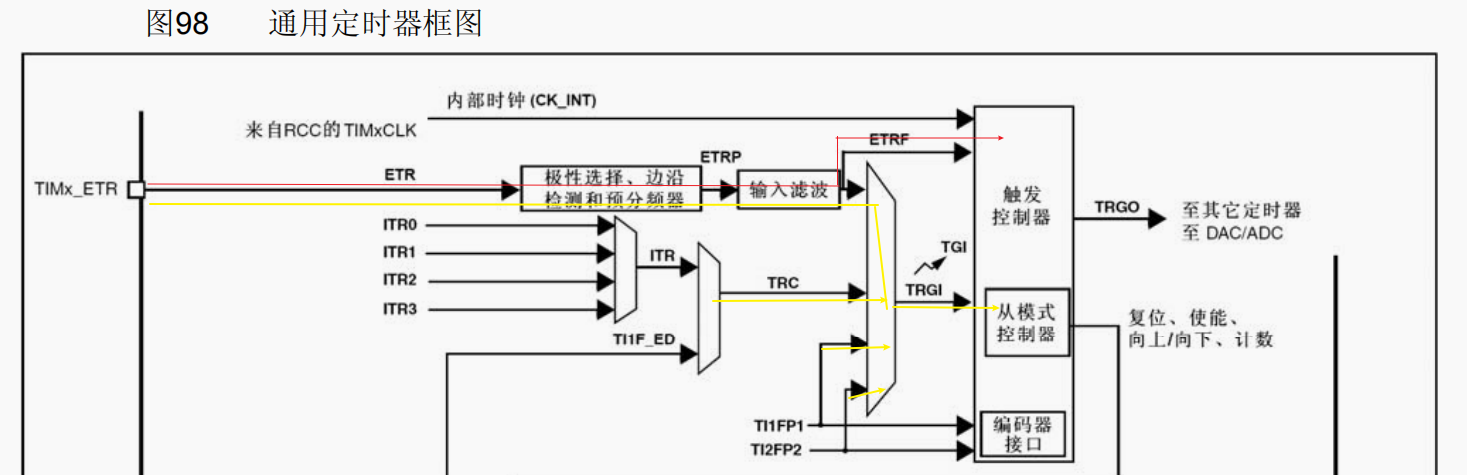

1)第一个外部时钟就是来自 TIMx_ETR 引脚上的外部时钟,可以在 TIM2 的ETR引脚也就是PAO上接一个外部方波时钟,然后配置一下内部的极性选择、边沿检测和预分频器电路,再配置一下输入滤波电路,这两块电路可以对外部时钟进行一定的整形(因为是外部时钟,所以难免会有毛刺,这些电路就可以对输入的波形进行滤波),同时也可以选择一下极性和预分频器,最后滤波后的信号,兵分两路,上面一路ETRF进入触发控制器,紧跟着就可以选择作为时基单元的时钟了,在STM32中,这一路也叫做外部时钟模式2’(如图中红线);另一路与其他信号通过一个数据选择器输出TRGI(Trigger In,触发输入),当这个TRGI当作外部时钟来使用时,这一路就称为外部时钟模式1(如图中黄线所示)。后者从名字上看,它主要是作为触发输入来使用的,这个触发输入可以触发定时器的从模式。关于从模式的内容之后再涉及,本节主要考量把这个触发输入当作外部时钟来考虑的情况。

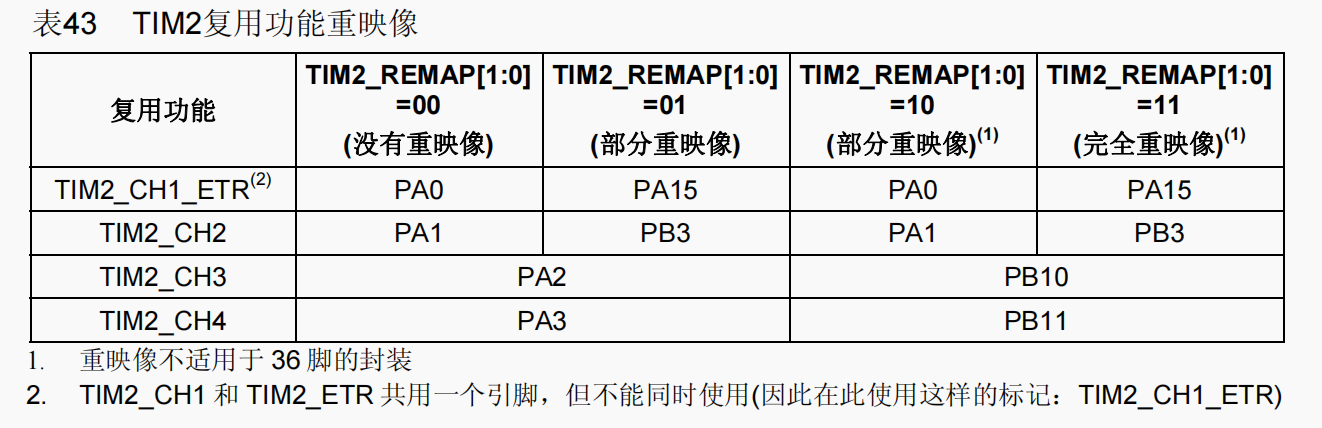

TIMxETR引脚的位置可以参考引脚定义表中关于默认复用功能和重定义功能的定义,如下图所示。可以看到TIM2的CH1 和ETR都复用在了引脚PAO上。其他定时器的引脚也可以在表中找到。

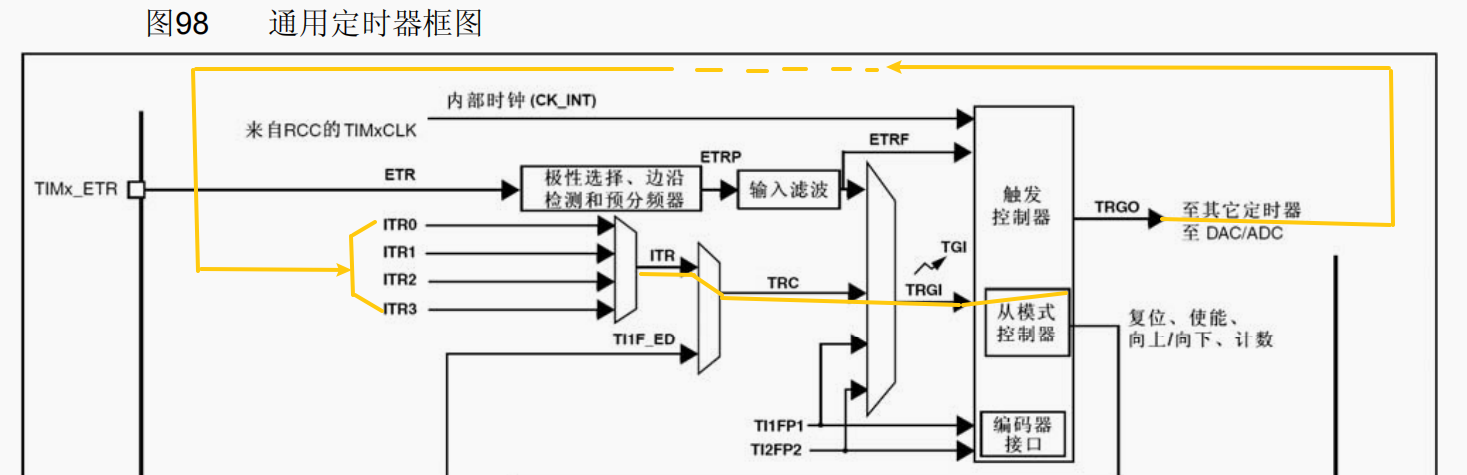

2)第二个外部时钟可以是来自其他定时器的信号ITR。主模式的输出TRGO可以通向其他定时器,实际上通向的就是ITR引脚,通过这一路就可以实现定时器级联的功能。如下图黄线所示,ITRO到ITR3分别来自其他4个定时器的TRGO输出,具体的连接方式如下表所示,

这就是ITR和定时器的连接关系。

实现定时器级联功能例如,可以先初始化TIM3,然后使用主模式把它的更新事件映射到TRGO上,接着再初始化TIM2,选择ITR2对应的就是TIM3的TRGO,然后后面再选择时钟为外部时钟模式1,这样TIM3的更新事件就可以驱动TIM2的时基单元,也就是实现了定时器的级联。

3)第三个外部时钟可来自TIMx_CH1的TI1_ED,CH1 引脚的边沿,即从 CH1引脚连接的输入捕获模块获得时钟,ED意为Edge,意为通过这一路的时钟,上升沿和下降沿均有效。

4)第四个外部时钟可来自TIMx_CH1的TI1FP1 和来自TIMx_CH2的TI2FP2.总结:外部时钟模式1的输入可以是ETR引脚、其他定时器、CH1引脚的边沿、CH1引脚和CH2引脚;外部时钟模式2的输入只能是ETR引脚。如果要使用外部时钟,首选ETR引脚外部时钟模式2的输入,这一路最简单最直接。

6.3.3编码器接口功能

编码器接口可以读取正交编码器的输出模型。编码器接口可接收增量(正交)编码器的信号,根据编码器旋转产生的正交信号脉冲,自动控制CNT自增或自减,从而指示编码器的位置、旋转方向和旋转速度。每个高级定时器和通用定时器都拥有1个编码器接口两个输入引脚借用了输入捕获的通道1和通道2.

6.3.4主从触发模式功能

上图中的TRGO与基本定时器类似,它可以将定时器内部的一些事件映射到其他电路,从而完成其他电路的功能。

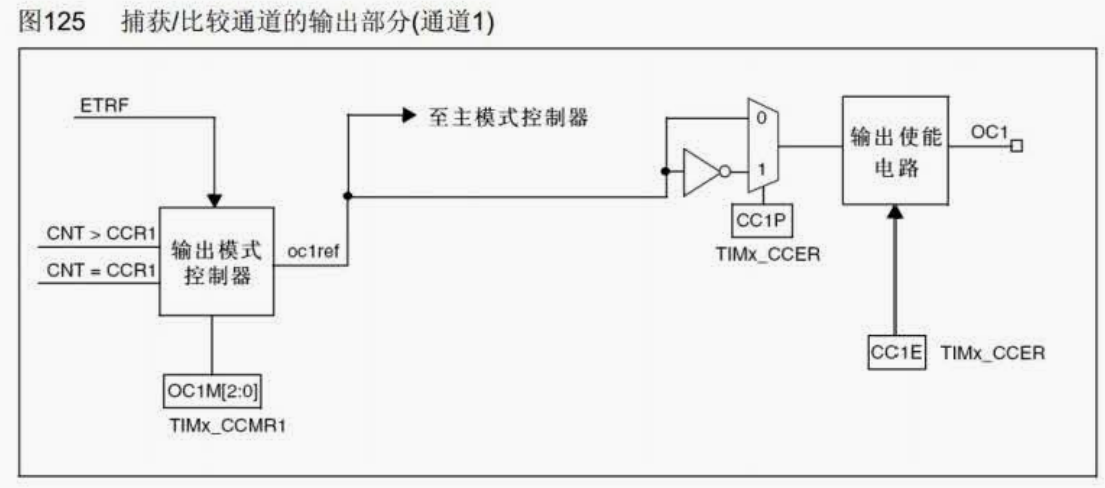

6.3.5输出比较功能

输出比较简介:OC(OutputCompare)输出比较;输出比较可以通过比较CNT与CCR寄存器值的关系,来对输出电平进行置1、置0或翻转的操作,用于输出一定频率和占空比的PWM波形;每个高级定时器和通用定时器都拥有4个输出比较通道;高级定时器的前3个通道额外拥有死区生成和互补输出的功能。

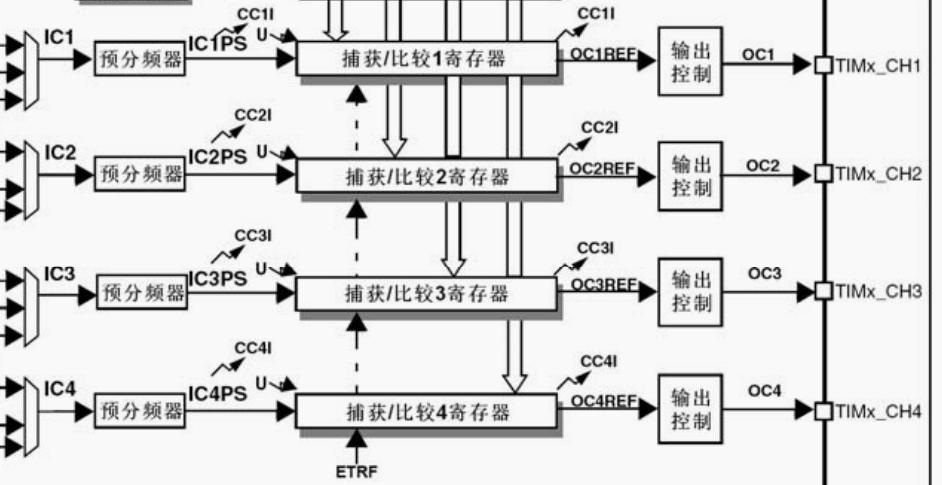

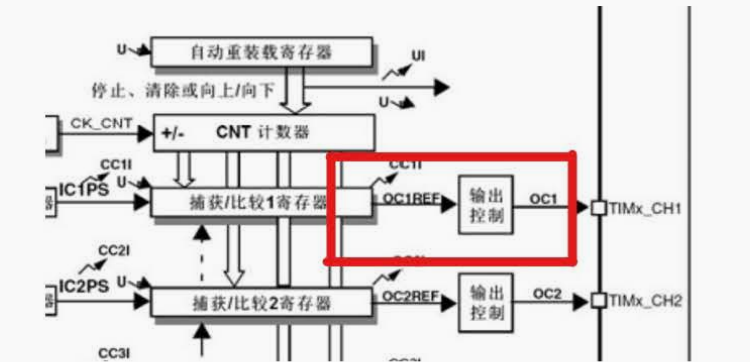

通用定时器结构图的右下角即为定时器的输出比较功能的结构,如下图所示。有四个输出通道,分别对应CH1到CH4的引脚,可以用来输出PWM波形,驱动电机。

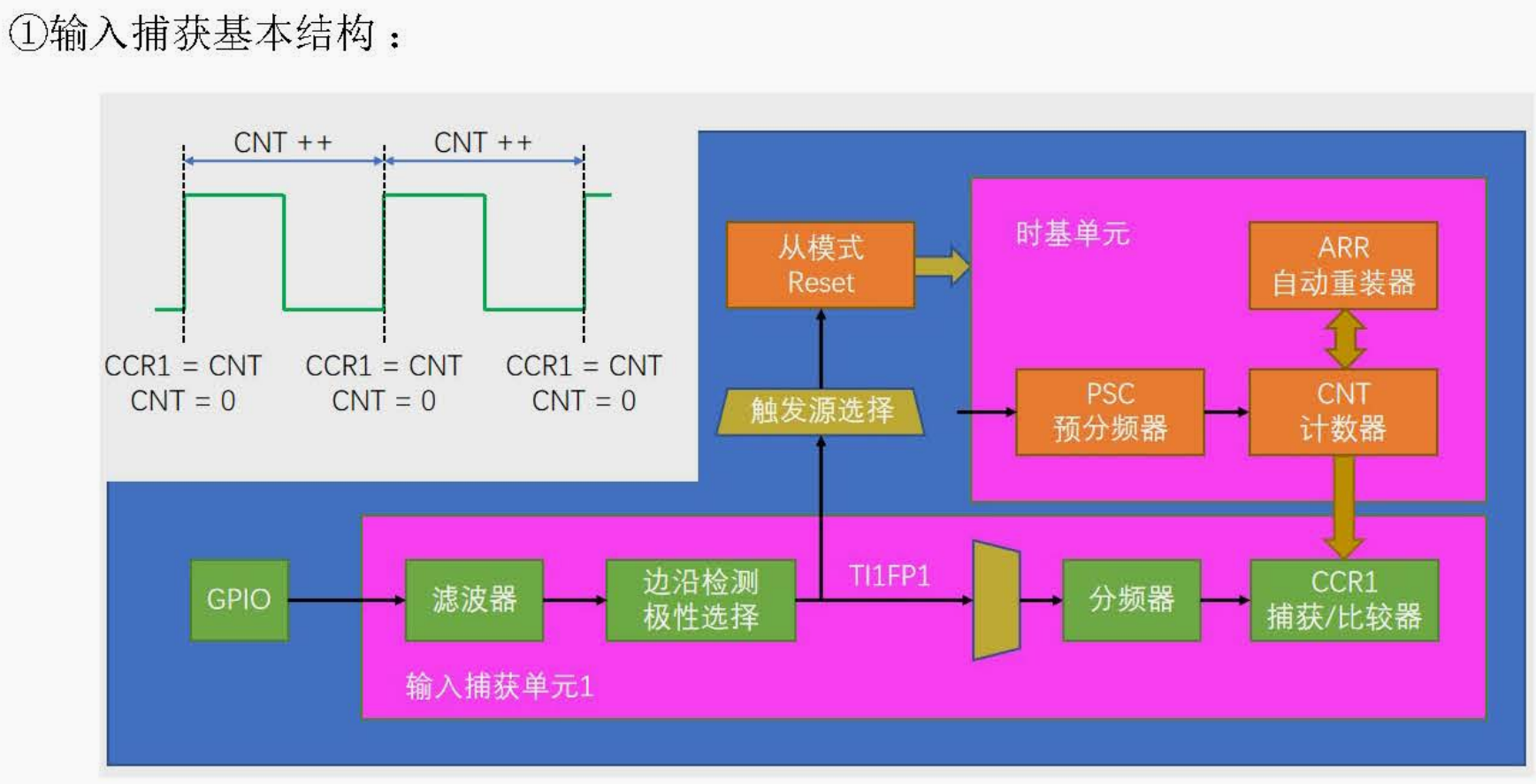

6.3.6输入捕获电路

输入捕获,即InputCapture,英文缩写为IC。输入捕获模式下,当通道输入引脚出现指定电平跳变瞬间(可以定义为上升沿、下降沿),当前CNT的值将被锁存到CCR中(检测电平跳变,然后执行动作(作用和外部中断差不多,区别是外部中断执行的动作是向CPU申请中断,输入捕获执行的是控制后续电路)),可用于测量PWM波形的频率、占空比、脉冲间隔、电平持续时间等参数。在这里,脉冲间隔和频率差不多、电平持续时间和占空比也是互相对应的关系。

每个高级定时器和通用定时器都拥有4各输入捕获通道,且二者没有区别。基本定时器没有输入捕获的功能。

输入捕获模块可以配置为PWMI(PWM输入)模式和主从触发模式。PWMI模式是PWM的输入模式,专门用来同时测量PWM波形的频率和占空比的。主从触发模式可以实现对频率或占空比的硬件的全自动测量。把这两个功能结合起来,测量频率和占空比就是硬件全自动执行,软件不需进行任何干预,也不需进中断,需要测量的时候,直接读取CCR寄存器就行了,使用非常方便且极大地减轻了软件的压力。

通用定时器的左下角即为输入捕获电路的结构图,它同输出比较功能一样有四个通道,对应CH1到CH4。可以用于测量输入方波的频率。因为 输入捕获和输出比较不能同时使用,故中间的捕获/比较寄存器是输入捕获和输出比较电路共用的,CH1到CH4的引脚也是共用的 。

输入捕获的各部分电路分析如下:

上图中最左边是四个通道的引脚;引脚进来,有一个三输入的异或门,这个异或门的输入接在了通道1、2、3端口,异或门的执行逻辑是,当三个引脚的任何一个有电平翻转时,输出引脚就产生一次电平翻转,3个引脚电平都相同为0,3个引脚中有高有低为1.

其次输出通过数据选择器,到达输入捕获通道1,数据选择器如果选择上面一个,那输入捕获通道1的输入就是三个引脚的异或值;若选择下面一个,异或门就没有用。设计异或门,其实还是为了三相无刷电机服务的,无刷电机有三个霍尔传感器检测转子的位置,可以根据转子的位置来进行换相。

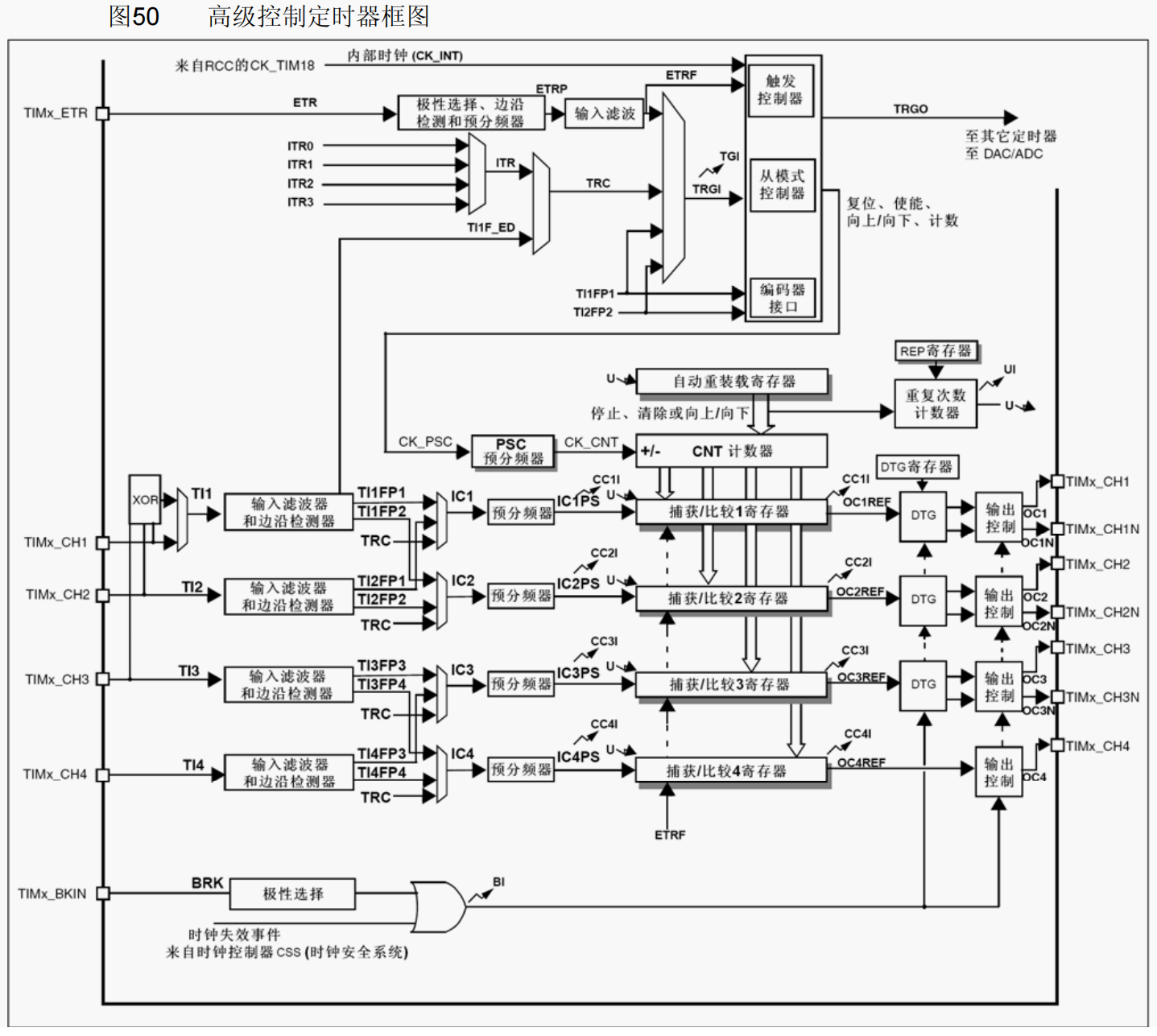

6.4高级定时器

高级定时器拥有通用定时器全部功能,并额外具有重复计数器、死区生成、互补输出、刹车输入等功能。高级定时器的大部分结构和通用定时器相同,只在部分作了功能拓展。相比于通用定时器,拓展了框图右边部分的内容。高级定时器框体如下:

6.4.1重复次数计数器

在申请中断的的信号输出处,增加了一个重复次数计数器,它的作用是:可以实现每隔几个计数周期,才发生一次更新事件和中断。 原来的结构是每个计数周期完成后就都会发生更新,现在这个计数器实现每隔几个周期再更新一次,相当于对输出的更新信号又作了一次分频。(对于高级定时器,我们之前计算的最大定时时间59秒多,在这里就还需要再乘一个65536,也就是提升了很多的定时时间)

6.4.2死区生成电路与三相无刷电机

上图中的 DTG和DTG寄存器组成死区生成电路 ,右侧的引脚TIMx_CH1/CH2/CH3由原来的每路一个变成了两个互补的输出引脚(TIMxCH1/CH2/CH3和TIMx_CH1N/CH2N/CH3N),可以输出一对互补的PWM波。这些电路是为了驱动三相无刷电机设计的。在四轴飞行器、电动车后轮、电钻中都可以发现三相无刷电机。三相无刷电机的驱动电路需要三个桥臂,每个桥臂需要2个大功率开关管来控制,总共需要6个大功率开关管控制。所以输出的PWM引脚的前三路就变为了互补的输出引脚,而第四路TIMx_CH4没有变化。三相电机只需要三路。

为了防止互补输出的PWM驱动桥臂时,在开关切换的瞬间,由于器件的不理想,造成短暂的直通现象,故添加了死区生成电路。 在开关切换的瞬间,产生一定时长的死区,让桥臂的上下管全部关断,防止出现直通现象。

6.4.3刹车输入

刹车输入的主要作用是给电机驱动提供安全保障。 如果外部引脚BKIN(Break In)产生了刹车信号,或者内部时钟失效,产生了故障,控制电路就会自动切断电机的输出 ,防止意外的发生。

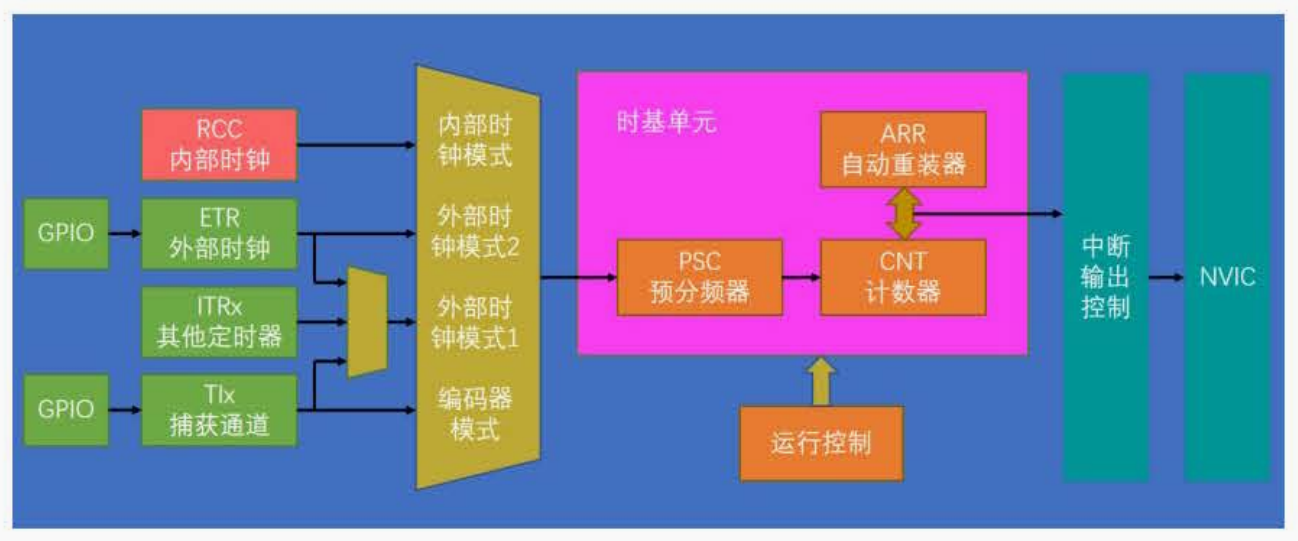

6.5定时中断基本结构

在定时器中最核心的部分是时基单元。下图中的“运行控制"就是控制寄存器的一些位,用来启动或停止计数器,配置向上向下计数方式等,操作这些寄存器就能控制时基单元的运行了。时基单元左边关于时钟源选择的部分,在上文都有详细的叙述。

计时时间到后,产生的中断信号会先在状态寄存器中置一个中断标志位,这个标志位会通过中断输出控制,到NVIC申请中断。这个中断输出控制存在的原因是:定时器模块有很多地方都要申请中断,如果需要该中断,就允许输出;如果不需要这个中断,就禁止输出。

简单来说,中断输出控制就是中断输出的允许位。定时中断基本结构图如下所示:

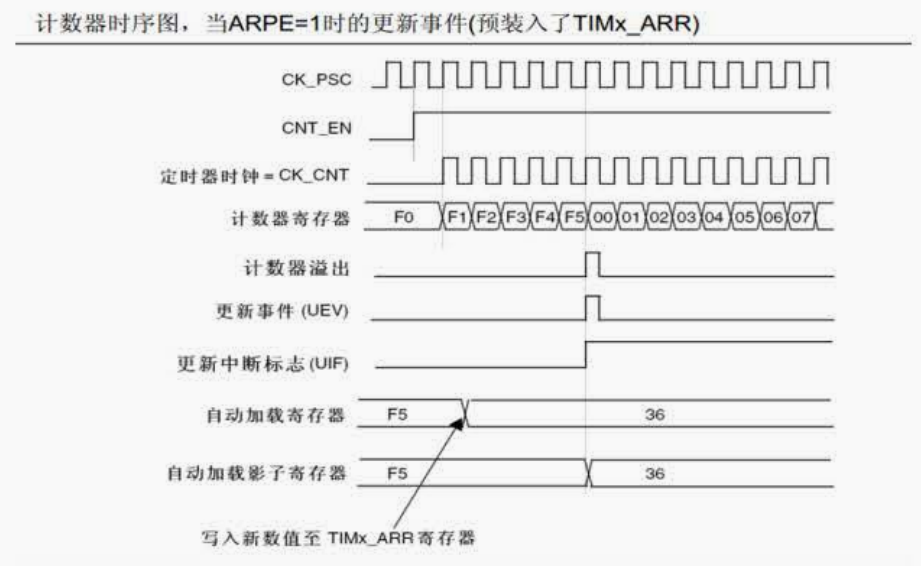

6.6时基单元运行时序

6.6.1缓冲(影子)寄存器

结构图中如下红圈中,带黑色阴影的寄存器,都是有 影子寄存器这样的缓冲机制,包括预分频器,自动重装载寄存器和捕获比较寄存器;这个缓冲寄存器是用还是不用,是可以自已设置的。

STM32在设计之初,为了保证能适用于多种多样的情况,故对时序运行过程中突然手动更改寄存器对时序的影响作了严谨的设计。 这里引入缓冲(影子)寄存器,主要目的就是同步,即可以让寄存器设定的某些目标值的变化和更新事件同时发生,防止在运行途中更改造成错误。 在定时器结构图中,有些寄存器的画法采用了方框下加阴影的方式,就说明该寄存器不是只有一个寄存器,而是有两个寄存器来形成缓冲机制。实际上,真正使时序电路状态发生更改的都是影子寄存器。

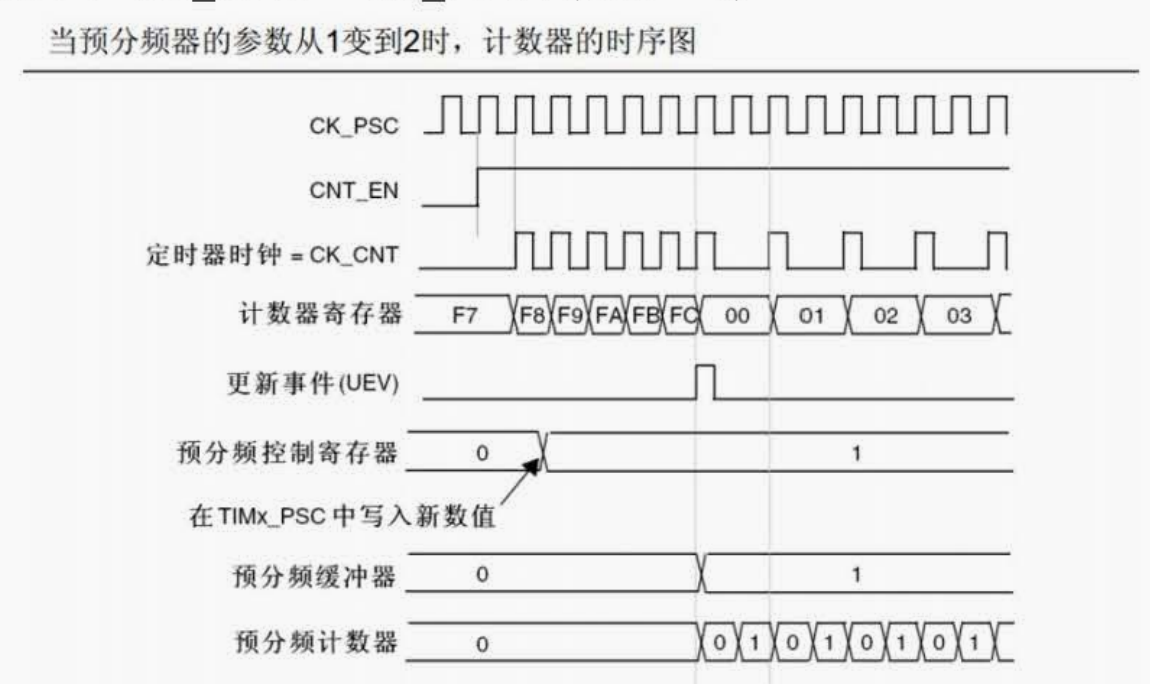

6.6.2预分频器时序分析

下图描述了当预分频器的分频系数从1变为2时,计数器的时序图。第一行是CK_PSC是预分频器的输入时钟,这个时钟在不断运行;下面的CNT_EN是计数器使能,高电平计数器正常运行,低电平计数器停止,再下面是CK_CNT是计数器时钟既是预分频器的时钟输出也是计数器的时钟输入。开始时,计数器未使能,计数器时钟不运行;然后使能后,前半段,当计数器使能信号CNT_EN变为高电平后的下一个CK_PSC的高电平,定时器时钟CK_CNT接收CK_PSC。且此时预分频器的分频系数为1,PSC=0,预分频器完成一分频,计数器时钟等于预分频前的时钟,即,CK_PSC=CK_CNT;后半段,预分频系数变为2,计数器时钟变为预分频前时钟的一半。

在计数器时钟的驱动下,下面的计数器寄存器也跟随时钟的上升沿不断自增;当计数器寄存器的值依次递增达到0xFC后立即跳变为0x00,说明重装载寄存器ARR设计的目标计数值就是0xFC,此时电路产生一个更新事件脉冲信号UEV,并产生中断信号,计数值清0.这就是一个计数周期的工作流程。然后是最下面的三行时序,描述的是预分频寄存器的一种缓冲机制,也就是这个预分频寄存器实际上是有两个:一个是倒数第三行的预分频控制寄存器,供读写用并不直接决定分频系数;另一个是倒数第二行的预分频缓冲寄存器(影子寄存器),才是真正起作用的寄存器,

在更新事件信号之前在TIMxPSC中写入新数值,将预分频器的分频系数从1改为2,但是由于缓冲寄存器的存在,CK_CNT不会立即变为CK_PSC/2,而是在下一次更新中断产生的同时,由预分频缓冲器(影子寄存器)修改分频系数为2,PSC=1.由预分频计数器时序可以看到,预分频的分频功能实际上也是通过计数器来实现的。当分频系数变为2后,预分频计数器按0、1、0、1依次计数,每当预分频计数器回到0时,预分频器输出信号,CN_CNT输出一个脉冲。

计数器计数频率:CK_CNT=CK_PSC/(PSC+1)

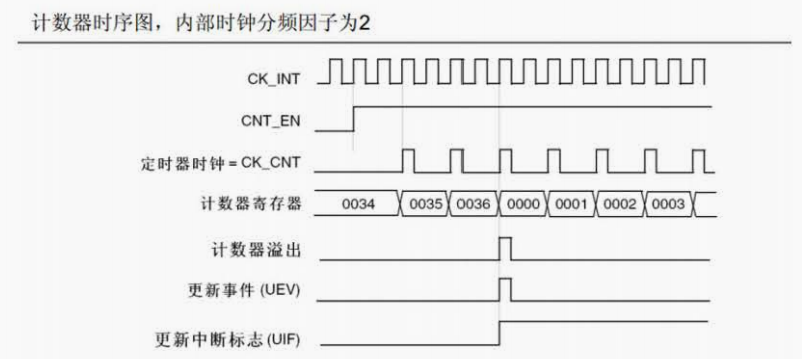

6.6.3计数器时序分析

1)计数器工作时序图如下:

内部分频因子为2,就是分频系数为2。第一行是内部时钟72MHz,第二行是时钟使能,高电平启动,第三行是计数器时钟,因为分频系数为2,所以这个频率是上面CKINT除2,然后计数器在这个时钟每个上升沿自增,当增到0036时发生溢出,之后再来一个上升沿,计数器清零,产生一个更新事件脉冲,另外还会置一个更新中断标志位UIF,标志位UIF只要置1就会去申请中断,然后中断响应后,需要在中断程序中手动清零,以上就是计数器的工作流程。

计数器溢出频率:CK_CNT_OV=CK_CNT/(ARR+1)=CK_PSC/(PSC+1)/(ARR+1)

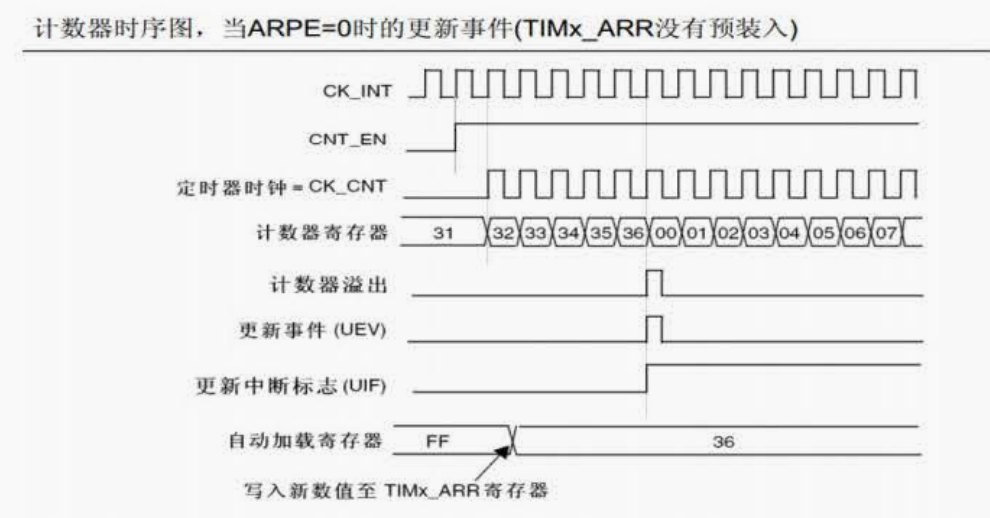

2)计数器无预装时序图(缓冲机制失效APRE=0)

计数器无预装时序就是没有缓冲寄存器的情况。在计数器正在进行自增计数,突然更改了自动加载寄存器,就是自动重装载寄存器由FF改成了36,即计数值的目标值就由FF变成了36,所以计数器寄存器计到36之后,就直接更新,开始下一轮计数。

23)计数器有预装时序(缓冲机制有效APRE=1)

计数器有预装时序就是有缓冲寄存器的情况。通过设置ARPE位,就可以选择是否使用预装功能。在有预装的情况下,在计数中途,若突然将自动加载寄存器计数目标由F5改成了36,下面影子寄存器才是真正起作用的,它还是F5,所以现在计数的目标还是计到F5,产生更新事件,同时,要更改的36才被传递到影子寄存器,在下一个计数周期这个更改的36才有效(类似10086,本月更改,下月生效),所以 引入影子寄存器的目的实际上是为了同步,就是让值的变化和更新事件同步发生,防止在运行途中更改造成错误。 在上面这个例子中,若不用影子寄存器的话,更改TIMx_ARR寄存器的值有一种不严谨情况:当F5改到36立即生效,但此时计数器已经到了F1,已经超过36了,F1只能增加,但它的目标值却是36比F1小,此时计数器寄存器的值只能递增,故该寄存器会一直递增到最大值0xFFFF之后回到0x0000,再依次递增,再加到36,才能产生更新。这里就可以看出,如果不使用缓冲机制,可能会给电路时序的工作造成一些问题。

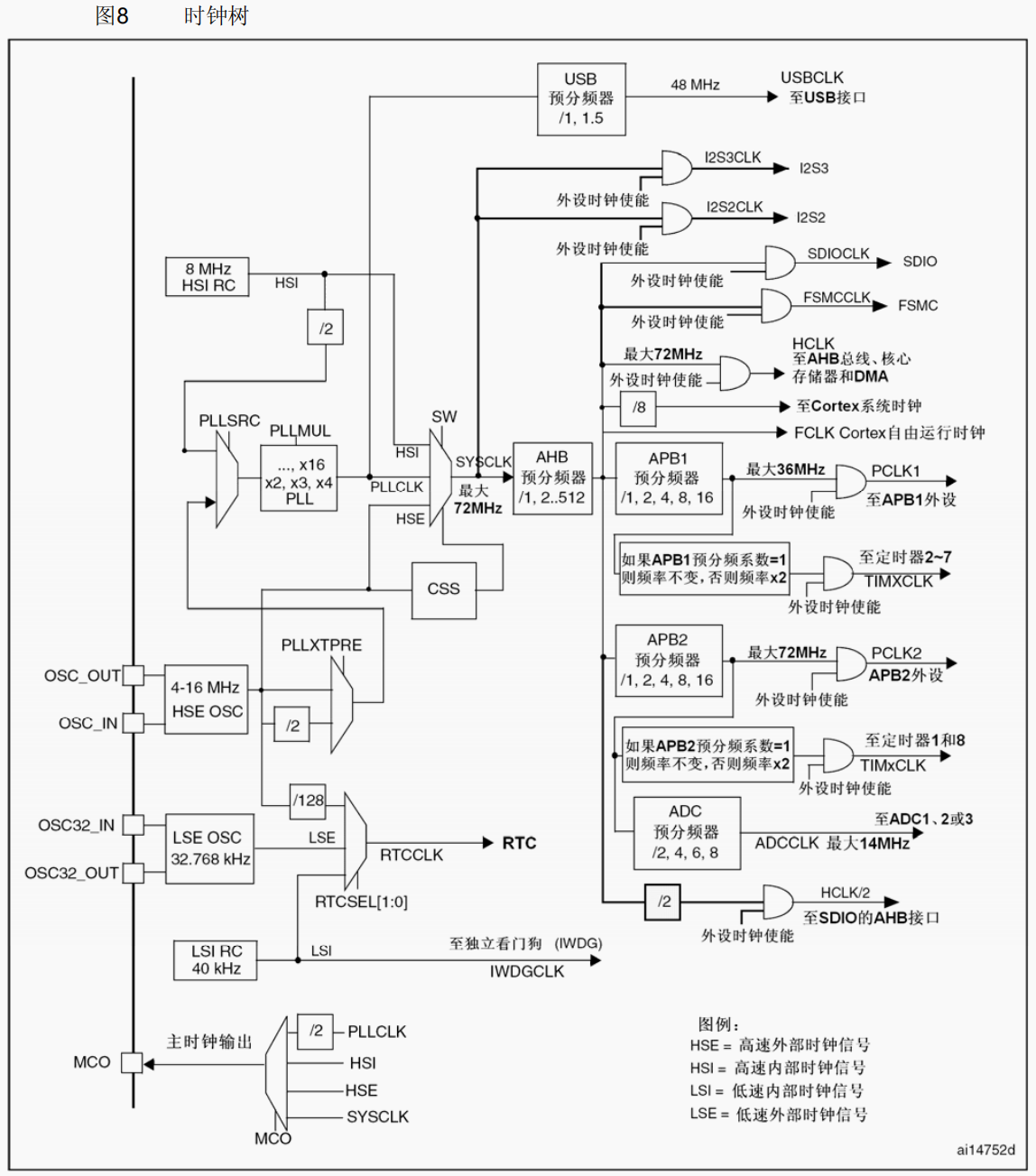

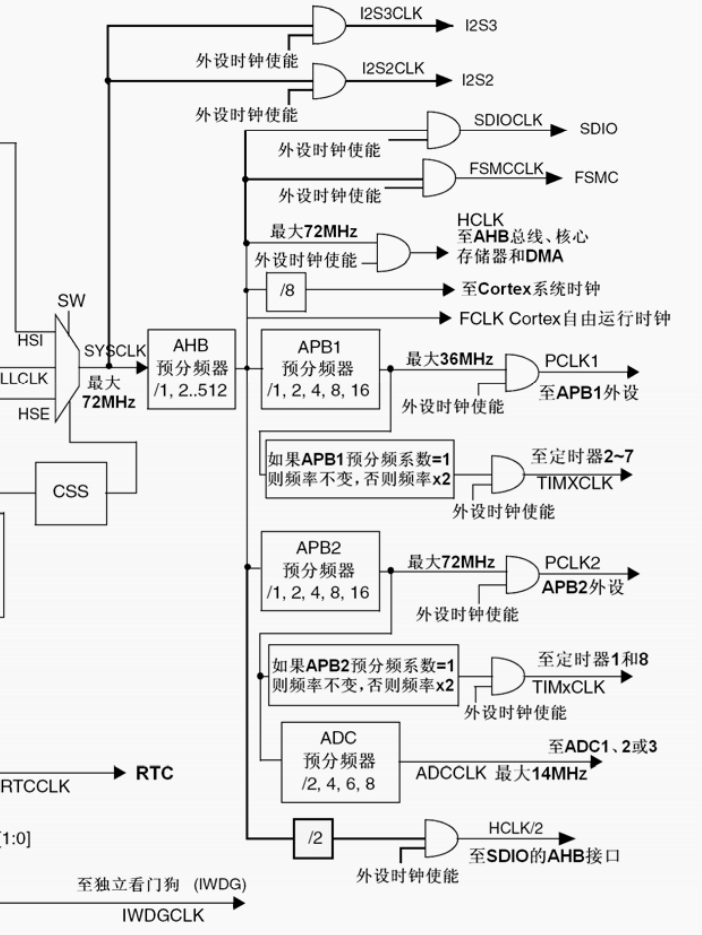

6.6.4RCC 时钟树简介

RCC时钟树:在STM32中用来产生和配置时钟,并且把配置好的各个外设都发射到各个外设的系统。时钟是所有外设运行的基础,所以时钟是最先配置的东西。在程序执行时,在执行主程序之前还会执行一个SystemInit函数,这个函数的作用就是配置RCC时钟树。

RCC时钟树可以分为左右两部分:时钟产生电路(左)和时钟分配电路(右)。中间的SYSCLK就是系统时钟72MHz。时钟树如下图所示:

1)。时钟产生电路

在时钟产生电路,有四个振荡源,分别是内部的8MHz高速RC振荡器、外部的4-16MHz高速晶振振荡器(也就是晶振,一般都外接8MHz)、外部的32.768kHz低速晶振振荡器(一般给RTC提供时钟)、内部的40kHz低速RC振荡器(给看门狗WDG提供时钟)。上面的连个该高速晶振是用来提供系统时钟的,AHB\APB2\APB1的时钟都是来源于这两个高速晶振。内部和外部都有一个8MHz的晶振,只不过外部的石英振荡器比内部的RC振荡器更加稳定,所以一般都用外部晶振。如果系统非常简单,且不需要过于精确的时钟,就可以使用内部的RC振荡器,这样可以省下外部的晶振电路。

在SystemInit函数中是这样来配置时钟的:首先会启动内部的8MHz高速RC振荡器产生时钟,选择该时钟为系统时钟,暂时以8MHz的内部时钟运行;然后再启动外部时钟。

图中的CSS称为时钟安全系统,它同样负责切换时钟。 CSS可以检测时钟的运行状态,一旦外部时钟失效,它就会自动把外部时钟切换为内部时钟,从而保证程序可以正常运行,不会卡死造成事故。另外在高级定时器的刹车输入功能中,一旦CSS检测到外部时钟失效,通过或门就会立刻反应到输出控制器,让输出控制的电机立刻停止,防止意外。(即切断输出控制引脚,切断电机输出,防止发生意外。)

2)时钟分配电路

首先系统时钟72MHz进入AHB总线,在AHB总线上有一个预分频器,在SystemInit函数配置的默认分频系数为1,所以AHB总线的时钟自然是72MHZ.

之后信号进入APB1总线,APB1上同样有预分频器,这里SystemInit默认配置的分频系数为2,输出为36MHz,所以APB1总线的时钟为36MHz。通用定时器和基本定时器是接在APB1上的,但是APB1(APB2同理)连接定时器还有如图所示的以下结构:

6.8 TIM 输出比较

6.8.1 PWM 简介

PWM(Pulse Mi dth Modul ati on)脉冲宽度调制,PWM 波形是一个激字输出信号,是由高低电平组成的,是一种对模拟电平信号进行数字编码的方法,在具有惯性的系统中,可以通过对一系列脉冲的宽度进行调制,来等效地获得所需要的模拟参量,常应用于电机控速等领域。也就是说,使用PWM波形,是用来等效地实现一个模拟信号的输出。(例如,led呼吸灯,电机调速,如下解释)

需要注意的是:只有在具有惯性的系统中,才能用 PWM 对模拟信号进行编码。

从下图可以看出,高低电平跳变的数字信号可以被等效地表示为中间虚线所表示的模拟量。当上面电平时间长一点,下面电平短一点的时候,等效地模拟量就偏向于上面:当下面电平时间长一点,上面电平时间短一点的时候,等效地模拟量就偏向于下面。也就是说,占空比越大,等效的模拟量就越趋近于数字量的高电平;占空比越小,等效的模拟量就越趋近于数字量的低电平,且这个等效关系一般而言是线性一一对应的。使用 PWM 波形,就可以在数字系统等效输出模拟量,就能实现LED控制亮度、电机控速等功能了。

6.8.2输出比较通道(通用)

通用定时器的输出比较部分电路如下图所示:

上图对应的是通用定时器电路里的下图红框部分电路,左边是CNT和CCR比较的结果,右边是输出比较电路,最后通过 TIM_CH1输出到GPIO引脚上。

上图红框部分所示,图的左边是CNT计数器和CCR1第一路的捕获/比较寄存器,它俩进行比较,当CNT=CCR1或者CNT>CCR1时,输出模式控制器就会收到一个信号,输出模式控制器就会改变它输出的OC1REF的高低电平。REF是Reference 的缩写,意为参考信号。

6.8.3输出模式控制器的工作流程

6.8.4PWM基本结构及参数介绍

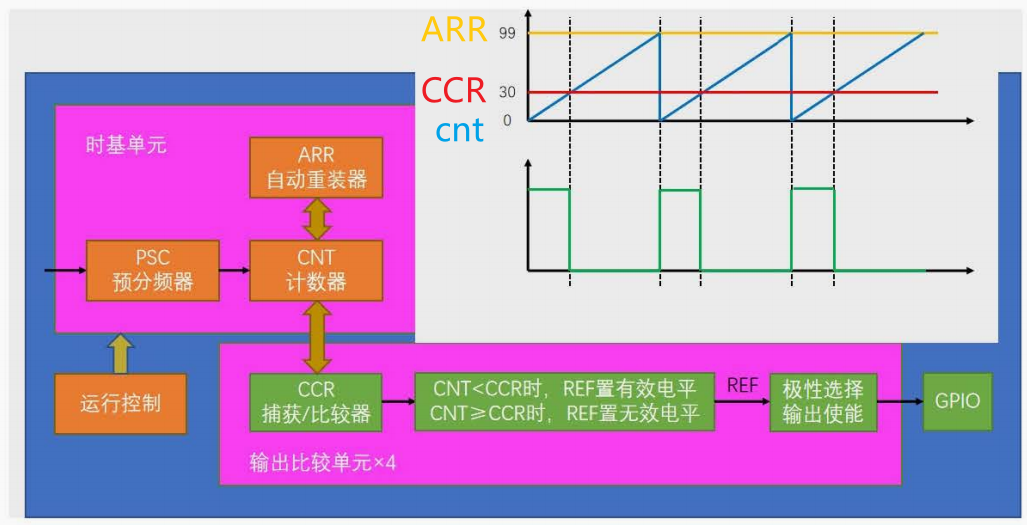

以PWM模式1、向上计数模式为例,PWM波形产生原理(输出PWM的基本结构)

如下图所示:

上图中,左上角是时间单元和运行控制部分,再左边是时钟源选择。配置好了时基单元,这里的CNT就可以开始不断地自增运行了。然后,下面粉红区域就是输出比较单元了,总共有四路,输出比较单元的最开始是CCR捕获/比较寄存器,CCR是我们自已设定的,CNT不断自增运行,同时它俩还在不断进行比较;CCR捕获/比较寄存器后面是输出模式控制器。

在这里以PWM模式1的执行逻辑为例,其输出PWM波形的过程如下:右上角图中,蓝色线是CNT的值,黄色线是ARR的值,蓝色线从0开始自增,一直增到ARR也就是99,之后清0继续自增,在这个过程中红色线是CCR,比如设置CCR为30,执行输出模式控制器里的逻辑,下面的绿色线就是输出,可以看到CNT<CCR时置高电平,之后CNT>=CCR就变为低电平,当CNT溢出清O后,CNT又小于CCR所以置高电平这样一直持续下去,REF的电平就会不断变化,并且它的占空比是受CCR 的值的调控的,如果 CCR 的值设置的高一些,输出的占空比就会变大,CCR设置的低一点,输出的占空比就会变小,以上就是PWM的工作流程。(这里REF就是一个频率可调,占空比也可调的PWM波形),最终再经过极性选择,输出使能,最终通向GPIO口,这样就能完成PWM波形的输出了。需要注意的是:设置的CCR值越接近ARR,输出的PWM波形的占空比就越大。

参数计算结果如下:

PWM 频率:Freq=CK_PSC /(PSC+1)/(ARR+1)

PWM 占空比:Duty=CCR/(ARR+1)

PWM分辨率:Reso=1/(ARR+1)

6.9TIM输入捕获

输入捕获对比输出比较:

输出比较,引脚是输出端口,根据CNT和CCR的大小关系来执行输出动作

输入捕获,引脚是输入端口,接收到输入信号执行CNT锁存到CCR的动作

6.9.1输入捕获通道

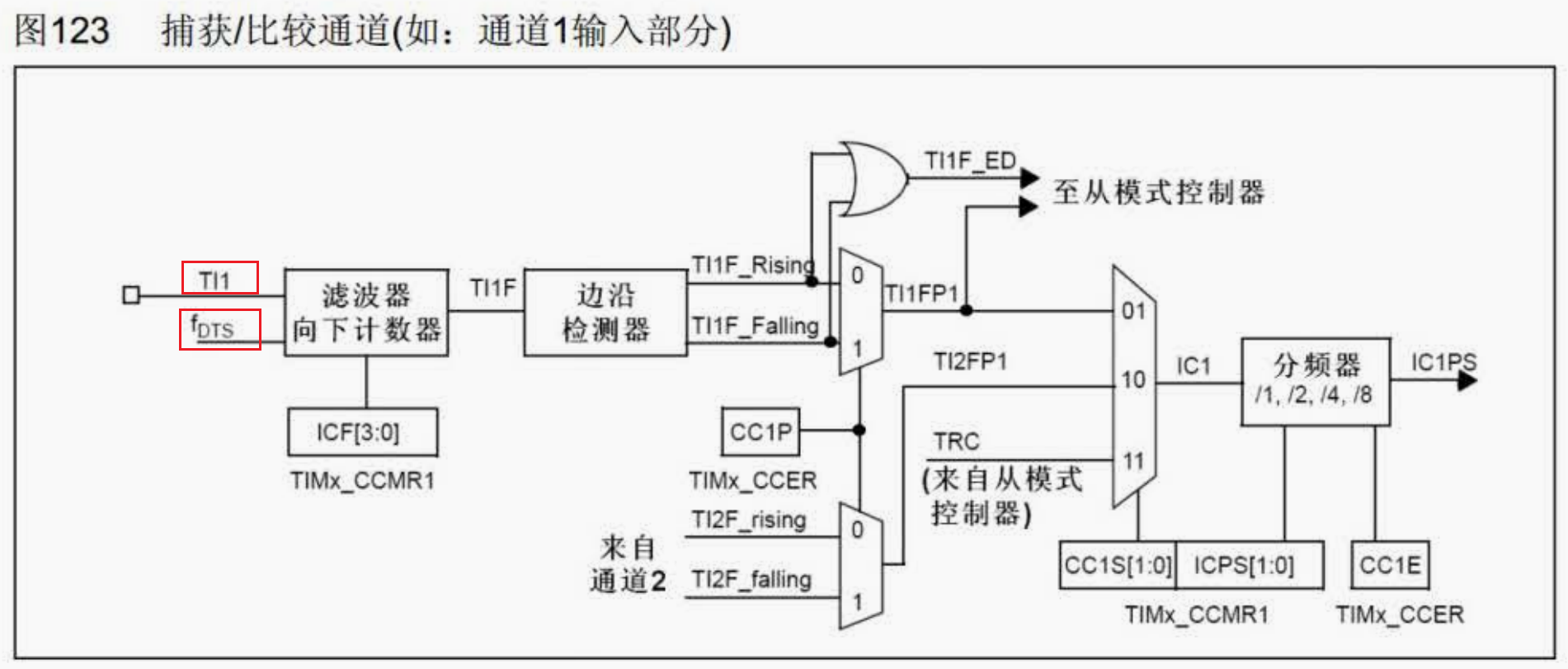

输入捕获通道1的详细框图如下所示:

上图电路细节内容如下:

引脚进来,先经过一个滤波器,滤波器的输入是TI1就是CH1的引脚,输出的TI1F就是滤波后的信号;FDTS是滤波器的采样时钟来源,CCMR1寄存器里的ICF位可以控制滤波器的参数。

滤波器的工作原理就是:以采样频率对输入信号进行采样,当连续N个值都为高电平,输出才为高电平,当连续N个值都为低电平,输出才为低电平,如果信号出现高频抖动,导致连续采样N个值不全都一样,那输出就不会变化,这样就可以达到滤波的效果。采样频率越低,采样个数N越大,滤波效果就越好。在实际应用中,如果波形噪声比较大,就可以把IC1F位参数设置大一点来过滤噪声。滤波之后的信号通过边沿检测器。捕获上升沿或者下降沿,CCER寄存器里的CC1P位可以进行极性选择,最终得到TI1FP1触发信号通过数据选择器,进入通道1后续的捕获电路。

同时还有一样的电路得到TI1FP2触发信号,连通到通道2的后续电路,上图并没有画出来,同样,通道2有TI2FP1连通到通道1的后续,通道2也有TI2FP2连通到通道2的后续,总共有四种连接方式,然后经过数据选择器,进入后续捕获部分电路,CCMR寄存器的CC1S位可以对数据选择器进行选择。

之后,CCMR寄存器的ICPS位可以配置分频器,可以选择不分频、2分频、4分频、8分频;CCMR寄存器的CC1E位,控制输出使能或失能。如果使能了输出,输入端产生指定边沿信号,经过层层电路,就可以最后将CNT的值转运到CCR里来,每捕获一次CNT的值,都要把CNT清一下,以便于下一次的捕获,从模式控制器就可以在捕获之后自动完成CNT的清零工作。TI1FP1信号和TI1F_ED边沿信号,都可以通向从模式控制器,比如TI1FP1信号的上升沿触发捕获,还可以同时触发从模式,这个从模式里就有电路,可以自动完成CNT的清零。从模式就是完成自动化操作的利器。

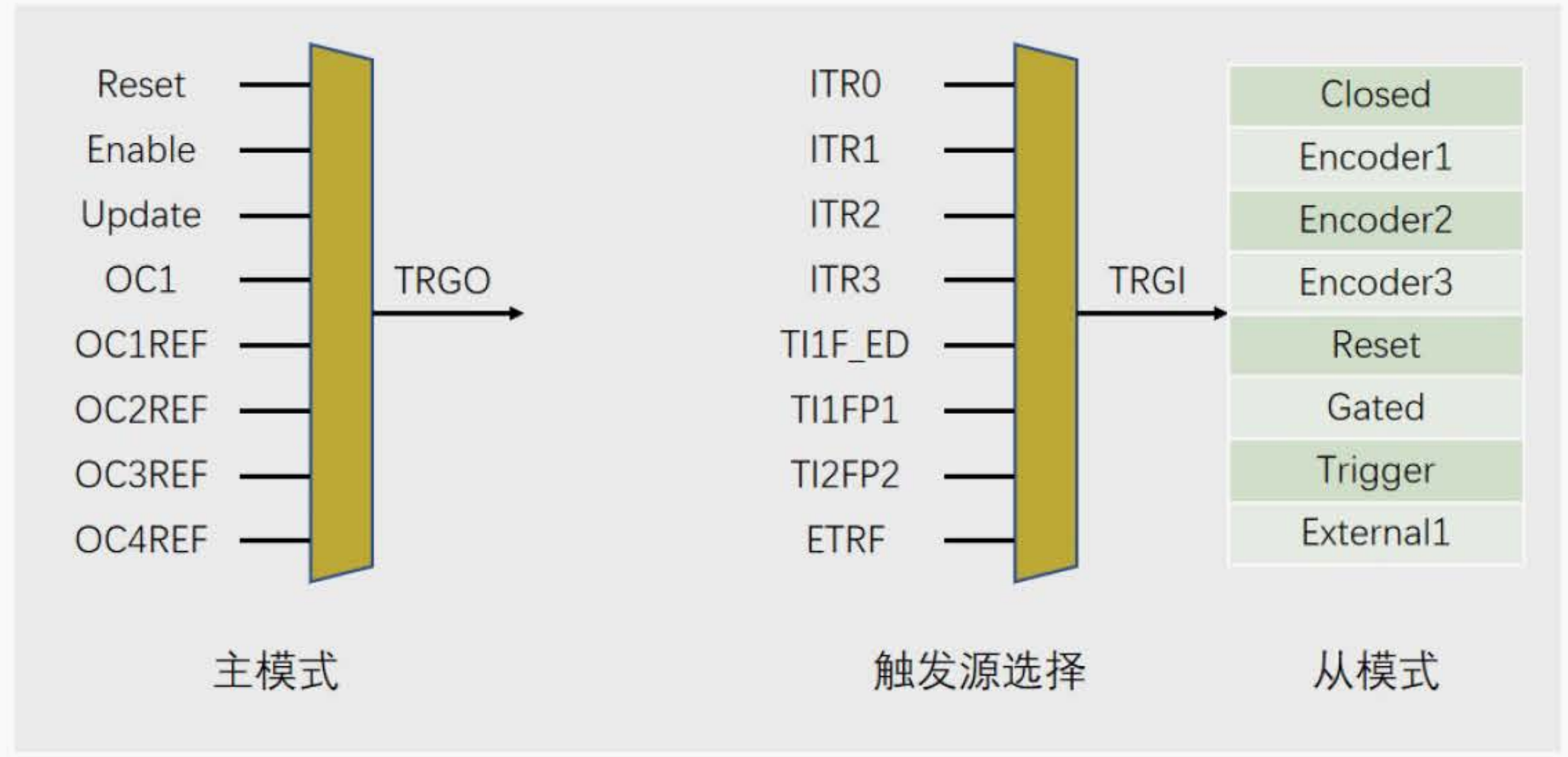

6.9.2输入捕获的主模式、从模式、触发源选择

CCR对 CNT进行捕获之后,需要对CNT进行一次清O操作,这样每次捕获得到的值才是测周法,两个上升沿(下降沿)之间的时间间隔。这个清0操作,就需要用到主从触发模式来自动完成。由输入捕获通道1的详细框图可得:经过滤波和极性选择的TI1FP1信号和经过滤波的边沿信号TI1F_ED都可以通向从模式控制器,之后便可以通过硬件电路自动完成 CNT的清0操作。

主从触发模式,即主模式、从模式和触发源选择三个功能的简称。主模式可以将定时器内部的信号映射到TRGO引脚,用于触发其他外设的操作;从模式可以接收其他外设或自身外设的一些信号,用于触发自已的一些操作(定时器的运行);触发源选择,即选择从模式的触发信号源功能,也可以认为它是从模式的一部分。

在从模式下,可以通过触发源选择功能选择一个信号产生TRGI信号,之后去触发从模式,从模式可以在上面列表中选择一项操作来自动执行。

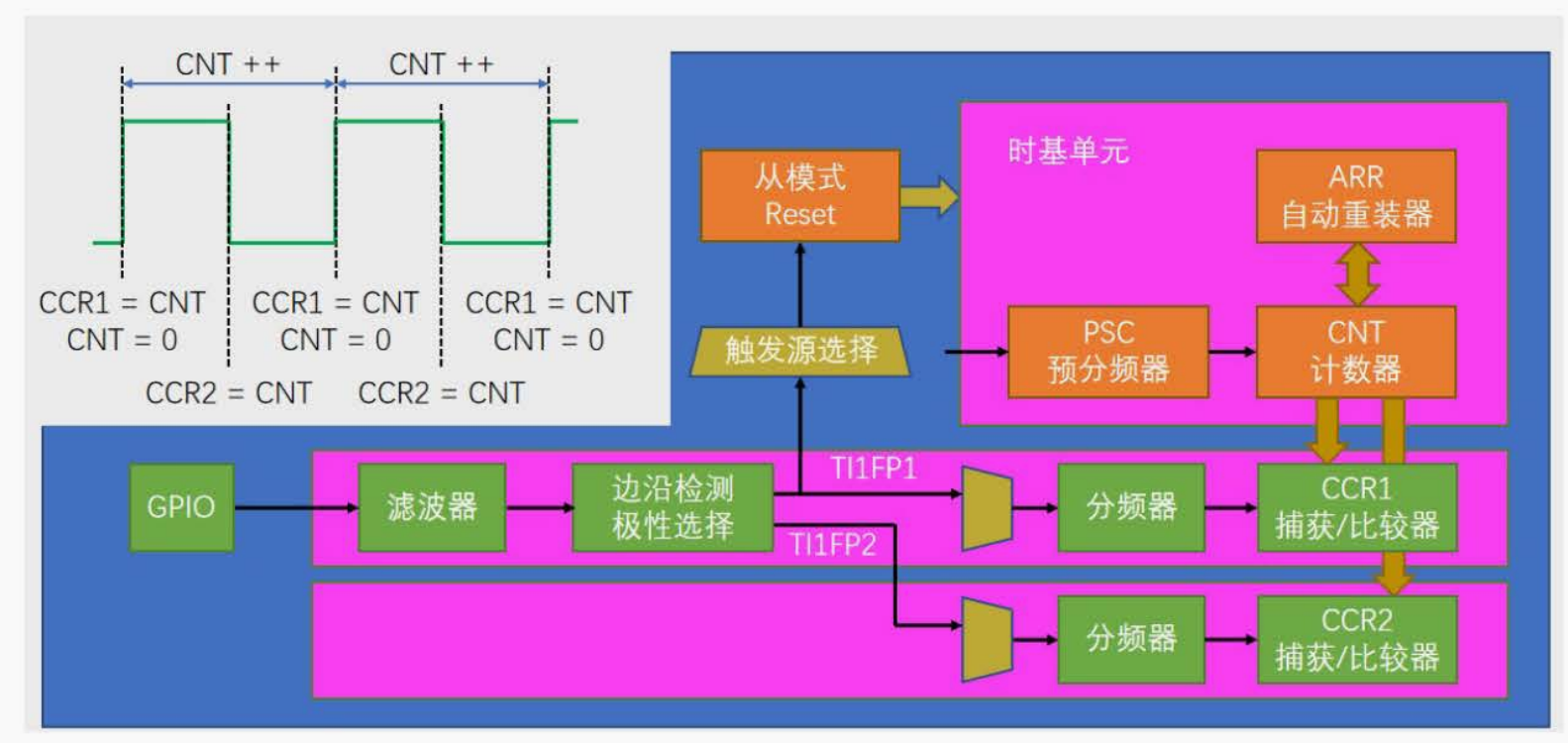

上图清晰地展示了输入捕获模式测量频率的过程,同时也是编程的逻辑基础。在这里我们只使用了一个通道,所以它只能测量频率。

首先,配置时基单元,启动寄存器,则CNT就会在预分频之后的时钟驱动下不断自增。 测周法用CNT来计数,间接实现计时的功能。经过预分频后的时钟频率,就是测周法的标准频率fc。之后,GPIO输入一个待测的方波信号,经过经过滤波器和边沿检测选择TI1FP1为上升沿触发,之后数据选择器选择直连通道,分频器选择不分频。当TI1FP1出现上升沿之后,CNT的值就会被CCR1转运捕获;同时触发源选择模块选择TI1FP1为触发信号,从模式选择复位操作,触发CNT清零(先后顺序是:先转运CNT的值到CCR,再触发从模式给CNT清零。或者是非阻塞的同时转移:CNT的值转移到CCR,同时0转移到CNT里面去,总之是先捕获,再清零)。当电路不断工作时,CCR1中的值始终是最新一个周期的计数值,即测周法的计次数N。所以,当读取信号的频率时,只需要读取CCR1得到N,再计算fc/N就得到频率了。当不需要读取时,整个电路全自动的测量,不需要占用任何软件资源。

这里需要注意以下两点:

1)CNT的计数值是有上限的。由于ARR最大为65535,故CNT最大也只能计65535个数。如果信号频率太低,CNT的计数值可能会溢出。

2)从模式的触发源选择中有TI1FP1和TI2FP2,但是没有TI3和TI4的信号。所以如果要使用从模式自动清零CNT,就必须使用通道1或通道2作为输入。对于通道3和通道4,就只能开启捕获中断,在中断中手动清0了(程序会处于频繁中断的状态,比较占用软件资源)。

②PWM1的基本结构

PWMI模式使用两个通道同时捕获一个引脚,可以同时测量周期和占空比,相比前面输入捕获,下面多了一个TI1FP2的通道。

首先TI1FP1配置上升沿触发,触发捕获和清零CNT,正常的捕获周期,再来一个TI1FP2,配置为下降沿触发,通过交叉通道去触发通道2的捕获单元(最开始上升沿CCR1捕获同时清零CNT,之后CNT一直加,然后在下降沿时刻触发CCR2捕获,这时CCR2的值就是CNT从上升沿到下降沿的计数值也就是高电平期间的计数值,CCR2捕获并不触发CNT清零,所以CNT继续加,直到下一次上升沿,CCR1捕获周期并CNT清零,这样执行之后CCR1就是一整个周期的计数值,CCR2就是高电平期间的计数值,用CCR2/CCR1就是占空比,以上就是PWMI模式使用两个通道来捕获频率和占空比的思路。另外也可以两个通道同时捕获第一个引脚的输入)

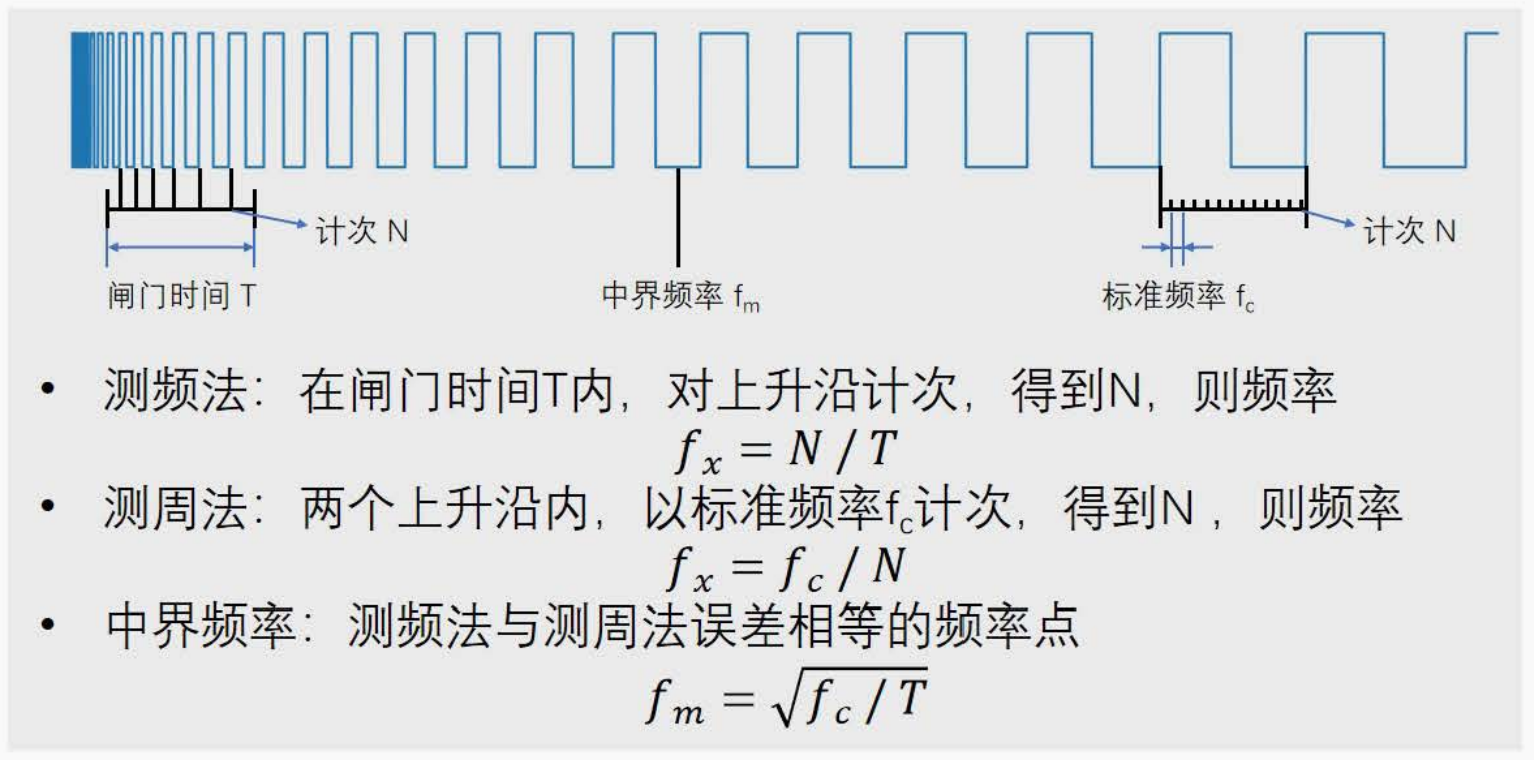

③频率测量方法

上图是频率逐渐降低的方波波形,越往左频率越高,越往右频率越低,这里信号都是只有高低电平的数字信号,对于STM32测频率而言,它也是只能测量数字信号的。如果需要测量一个正弦波则需要搭建一个信号预处理电路,最简单的就是用运放搭建一个比较器,把正弦波转换为数字信号再输入给STM32就行了:如果测量的信号电压非常高,那还要考虑隔离的问题,比如使用隔离放大器、电压互感器等元件,隔离高压端和低压端,保证电路的安全。总之,经过处理最终输入给STM32的信号是如上图的高低电平信号,高电平3.3V,低电平OV.

为了测量频率,有两种方法可以选择:测频法、测周法

1)测频法:定时器中断,并记录捕获次数;

在闸门时间T内,对上升沿(也可以是下降沿)计次,得到N,则待测信号频率f为:

f=N/T

2)测周法:捕获中断,并记录定时器次数。

两个上升沿内,以标准频率fc计次,fc=72M/(psc+1),得到N(就是读取CCR的值),则测量频率f为:

f =fc/N

对于测频法和测周法的一个共同点是:N越大,误差就越小。在两种方法中,计次都可能会产生正负1误差。在测频法的一个闸门时间内,并不是每一个被测信号的周期都是完整的;测周法的标准计数信号的信号也不一定是被测信号的整数倍,所以它也不一定是每一个都完整的。对于上述的两种情况,都会出现多计一个数或者少计一个数的情况,所以会产生正负1误差。

如何在不同情况下正确选择测频法和测周法呢?所以多高算高频,多低算低频,我们有以下一个参数来考量:中界频率,测频法和测周法误差相等的频率点。由于两种方法的误差都与N的正负1误差有关,所以当两种方法计次的N相同时,两种方法的误差也就相同。消去两种方法公式中的N,将测频法和测周法的N提出来,令两个方法N相等,将fm解出来,可得:

fim=Vfe/T

式中,T是测频法的闸门时间,fc是测频法的标准频率。

当待测信号频率小于中界频率时,测周法误差更小,选择测周法更合适;当待测信号频率大于中界频率时,测频法误差更小,选择测频法更合适。

7ADC模数转换器

7.1AD简介

1)ADC(Analog-Digital Converter)模拟-数字转换器。

2)ADC可以将引脚上连续变化的模拟电压转换为内存中存储的数字变量,建立模拟电路到数字电路的桥梁。①STM32主要是数字电路,数字电路只有高低电平,没有几v电压的概念,所以想读取电压值,就需要借助adc模数转换器来实现,adc读取引脚上的模拟电压转换为一个数据存在寄存器里,我们再把这个数据读取到变量里来就可以进行显示、判断、记录等操作了;②.数字到模拟的桥梁是DAC数字模拟转换器, 使用DAC就可以将数字变量转换为模拟电压,PWM也是数字到模拟的桥梁,PWM实现的就是DAC的功能,同时PWM只有完全导通和完全断开两种状态,在这两种状态上都没有功率损耗, 所以在直流电机调速这种大功率的应用场景使用pwm来等效模拟量是比DAC更好的选择并且pwm电路更加简单更加常用,所以pwm还是挤占了dac很多的应用空间,目前dac的应用主要是在波形生成领域比如信号发生器、音频解码芯片等这些领域pWm还是不好代替的)

3)12位逐次逼近型ADC,1us转换时间。(逐次逼近型是ADC的工作模式;12位和1us涉及到adc的俩个关键参数,第一个是分辨率,一般用多少位来表示,12位ad值表示范围就是0~2^12-1就是量化结果的范围0~4095,位数越高量化结果就越精细,对应分辨率就越高;第二个是转换时间就是转换频率,ad转换是需要花一小段时间的,这里1us就是表示从ad转换开始到产生结果需要花1us的时间,对应ad转换的频率就是1MHz(1MHz的周期是1微秒,是STM32的adc最快转换频率),如果转换一个频率非常高的信号那就需要考虑一下这个转换频率是不是够用,如果信号频率比较低那这个最大1MHz的转换频率也完全够用)

4)输入电压范围:0~3.3V,转换结果范围:0~4095. adc的输入电压一般要求是在芯片供电的负极和正极之间变化的,0v对应0,3.3v对应4095,中间都是一一对应的线性关系。

5)18个输入通道,可测量16个外部和2个内部信号源。外部信号源就是16个gpio口,在引脚上直接接模拟信号就行了,不需任何额外的电路,引脚就直接能测电压;2个内部信号源是内部温度传感器和内部参考电压,温度传感器可以测量cpu的温度:内部参考电压是一个1.2v左右的基准电压,这个基准电压是不随外部供电电压变化而变化的。

6)规则组和注入组两个转换单元。 是STM32adc的增强功能,普通的ad转换流程是启动一次转换读一次值然后再启动再读值这样的流程,STM32的adc可以列一个组,一次启动一个组连续转换多个值并且有两个组,一个是用于常规使用的规则组,一个是用于突发事件的注入组。

7)模拟看门狗自动监测输入电压范围。"一般可以用于测量光线强度,温度这些值。就是如果光线高于某个值/低于某个阈值或者温度高于某个阈值/低于某个阈值执行一些操作,这个高于某个阈值/低于某个阈值的判断就可以用模拟看门狗来自动执行,模拟看门狗可以监测指定的某些通道,当ad值高于设定的上阈值或低于下阈值时它就会申请中断,就可以在中断函数里执行相应的操作,这样就不用不断地手动读值再用if进行判断了,

8)STM32F103C8T6ADC资源:ADC1、ADC2,10个外部输入通道。对于单片机的普通GPIO来说,只能读取引脚的高低电平,要么是高电平,要么是低电平,只有两个值,而使用了ADC之后,我们就可以对高电平和低电平之间的任意电压进行量化,最终用一个变量来表示,读取这个变量就可以知道这个引脚的具体电压到底是多少了,所以ADC其实就是一个电压表,把引脚的电压测出来放在一个变量里,这就是ADC的作用。

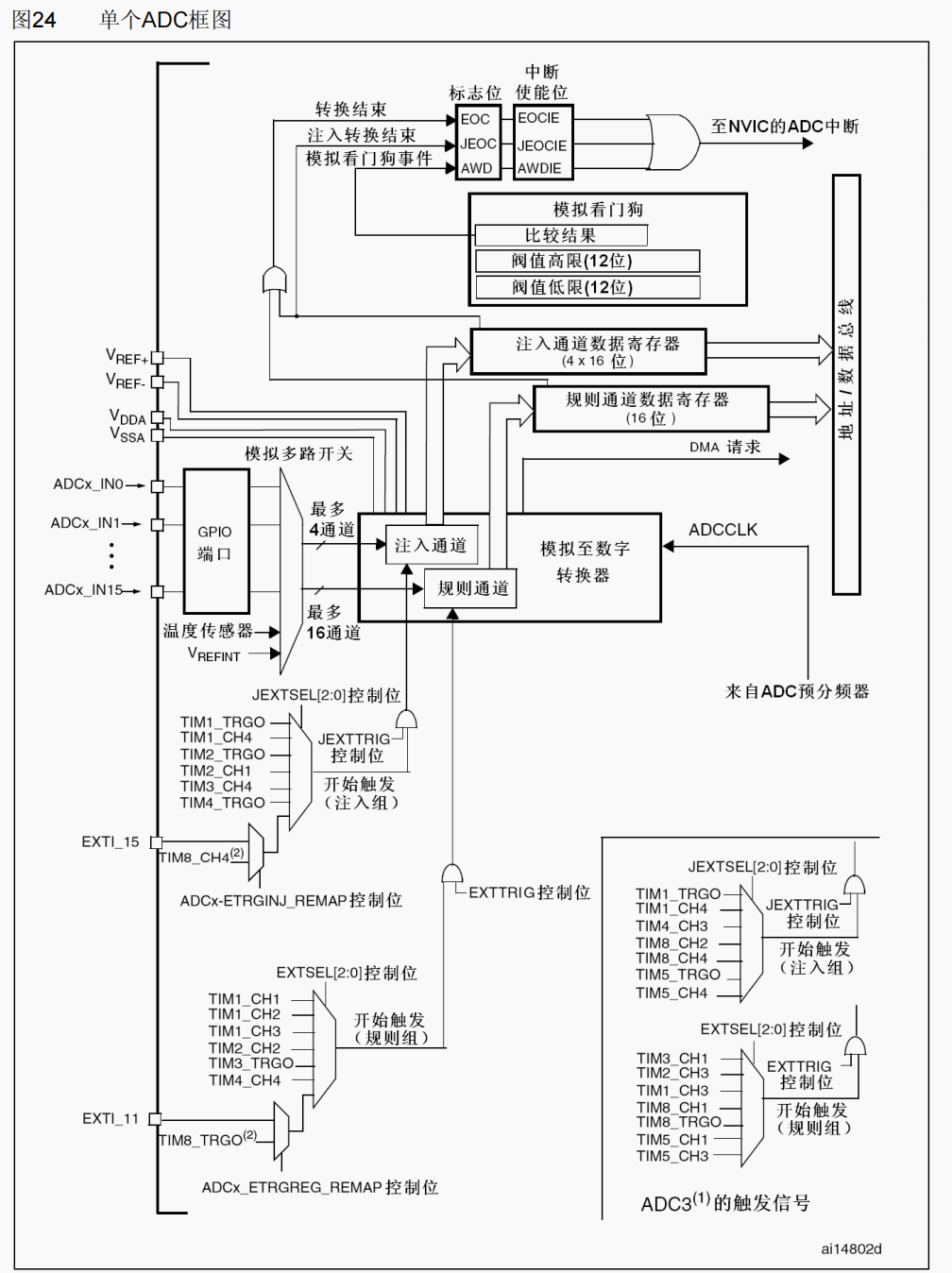

7.2逐次逼近型ADC

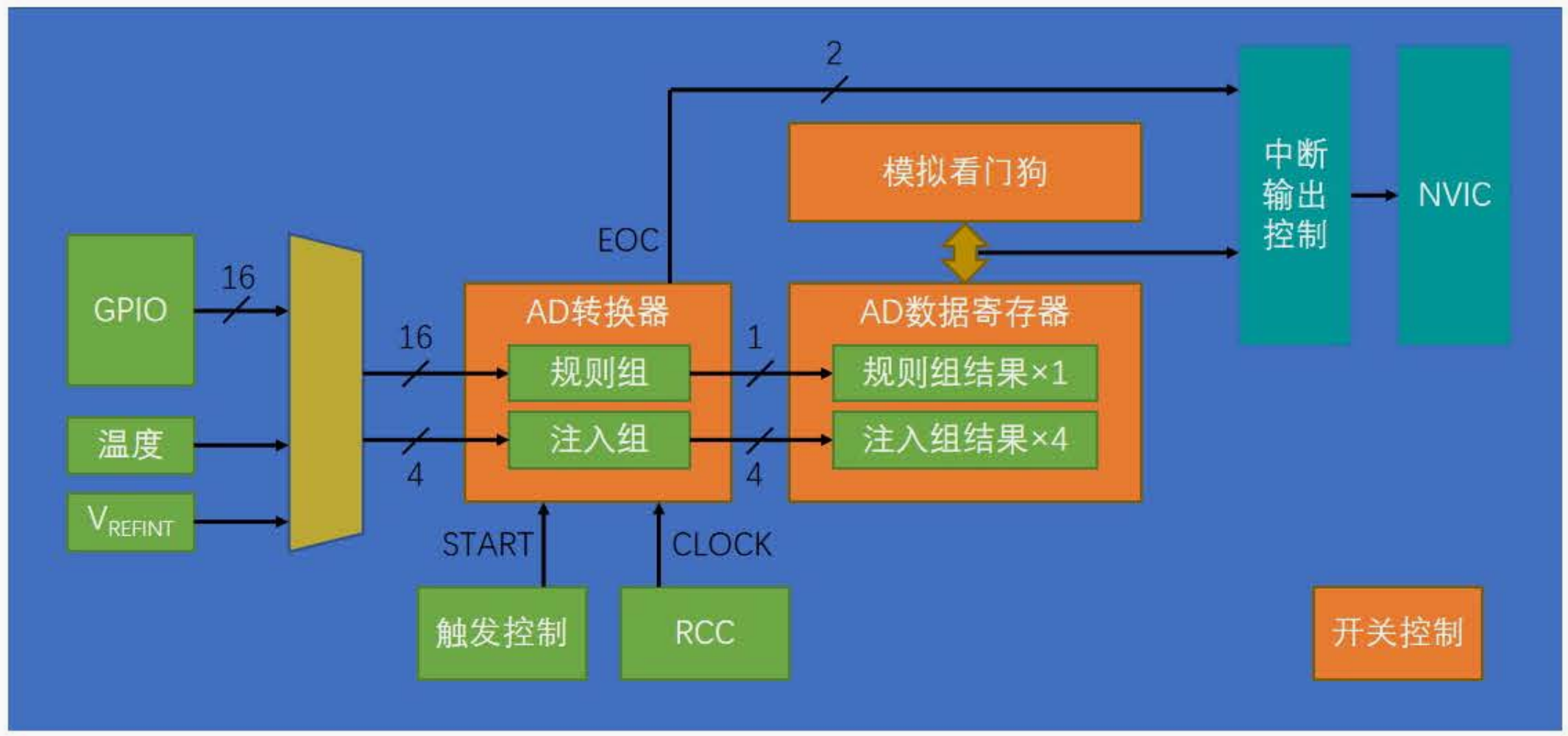

7.2.1STM32的ADC框图

STM32中ADC的结构框图如上图所示。总共有18个输入通道包括16个gpio口和2个内部通道(内部温度传感器和内部参考电压)。模拟多路开关可以指定我们想要的通道,右边是多路开关的输出,进入到模数转换器(这里模数转换器就是执行刚讲的逐次比较的过程),转换结果会直接放在数据寄存器里,读取寄存器就能知道adc转换的结构了。

对于普通的adc,多路开关一般都是只选中一个(就是选中一个通道、开始转换、等待转换完成、读取结果,这是普通的流程)。而STM32的多路开关就比较高级,可以同时选中多个,而且在转换的时候还分成了两个组 (规则组和注入组) ,其中规则组可以一次性最多选中16个通道,注入组最多可以选中4个通道。

1)普通的ADC多路开关一般只选中一个,STM32的ADC可以同时选中多个通道进行转换,规则组最多同时选中16个通道,注入组一次最多可以选中4个通道。

2)STM32中的ADC的转换结果会被存储在对应的数据寄存器中。对于规则组通道,其只有一个数据寄存器,后转换的数据会将之前转换的数据覆盖,之前转换的数据就会丢失。对于规则组通道,要想实现同时转换的功能,最好配合DMA来将转换后的数据及时转运,DMA可以在读取一个数据之后,把这个数据挪到其它地方去,防止被覆盖,就可以保证转换的数据不会丢失了。对于注入组通道,它拥有4个数据寄存器。对于注入组而言,就不用担心数据覆盖的问题了。一般情况下,使用规则组和DMA就可以满足大部分的使用需求。

3)STM32的触发转换信号来源有两种:软件触发和硬件触发。软件触发就是在程序中手动调用一条代码就可以启动转换了。硬件触发信号可以来自于定时器的各个通道、定时器TRGO定时器主模式的输出,外部中断EXTI.

4)ADC可以通过DMA请求信号触发DMA转运数据。

5)模拟看门狗的功能是监测指定的通道。可以设置模拟看门狗的阈值高限(12位)、值底限(12位)和指定“看门”的通道。只要通道的电压值超过阈值范围,模拟看门狗就会“乱叫”,申请一个模拟看门狗的中断,之后通向NVIC.

6)ECC是规则组的完成信号,JEOC是注入组完成信号,这两个信号会在状态寄存器里置一个标志位,读取这个标志位就能知道是不是转换结束了,同时这两个标志位也可以去到NVIC 申请中断,如果开启了NVIC对应的通道就会触发中断

定时器可以通向DAC、ADC这些外设用于触发转换,因为ADC经常需要过一个固定时间段转换一次,比如每隔1ms转换一次(正常思路就是用定时器每隔1ms申请一次中断,在中断里手动开始一次转换)但是频繁进中断对程序运行一定影响的,比如当有很多中断都需要频繁进入,那肯定会影响主程序的执行并且不同中断之间由于优先级的不同也会导致某些中断不能及时得到响应,如果触发ADC的中断不能及时响应那adc的转换频率就肯定会产生影响,所以对于这种需要频繁进中断,并且在中断里只完成了简单工作的情况,一般都会有硬件支持 (比如可以给tim3定个1ms的时间并且把tim3的更新事件选择为TRGO输出,然后在ADC选择开始触发信号为tim3的TRGO,这样 tim3的更新事件就能通过硬件自动触发adc转换了,整个过程不需进中断,节省了中断资源,这就是定时器触发的作用)

7.2.2STM32的ADC基本结构

如下图,左边是输入通道,16个gpio口外加两个内部通道,然后进行AD转换器,ad转换器里有两个组,一个是规则组、一个是注入组;规则组最多可以选中16个通道,注入组最多可以选择4个通道,然后转换的结果可以存放在AD数据寄存器里,其中规则组有1个数据寄存器,注入组有4个,然后有触发控制提供了开始转换的START信号,触发控制可以选择软件触发和硬件触发,硬件触发主要来自定时器,也可以选择外部中断引脚,然后还有ADC时钟CLOCK来自RCC,adc逐次比较的过程就是由这个时钟推动的,然后可以布置一个模拟看门狗用于检测转换结果的范围,如果超出设定的阈值就通过中断输出控制向NVIC申请中断,另外规则组和注入组转换完成后会有个EOC信号会置一个标志位,当然也可以通向NVIC,最后还有个右下角有个开关控制,在库函数中就是ADCLCmd函数用于给ADC上电,以上就是STM32ADC的内部结构了。

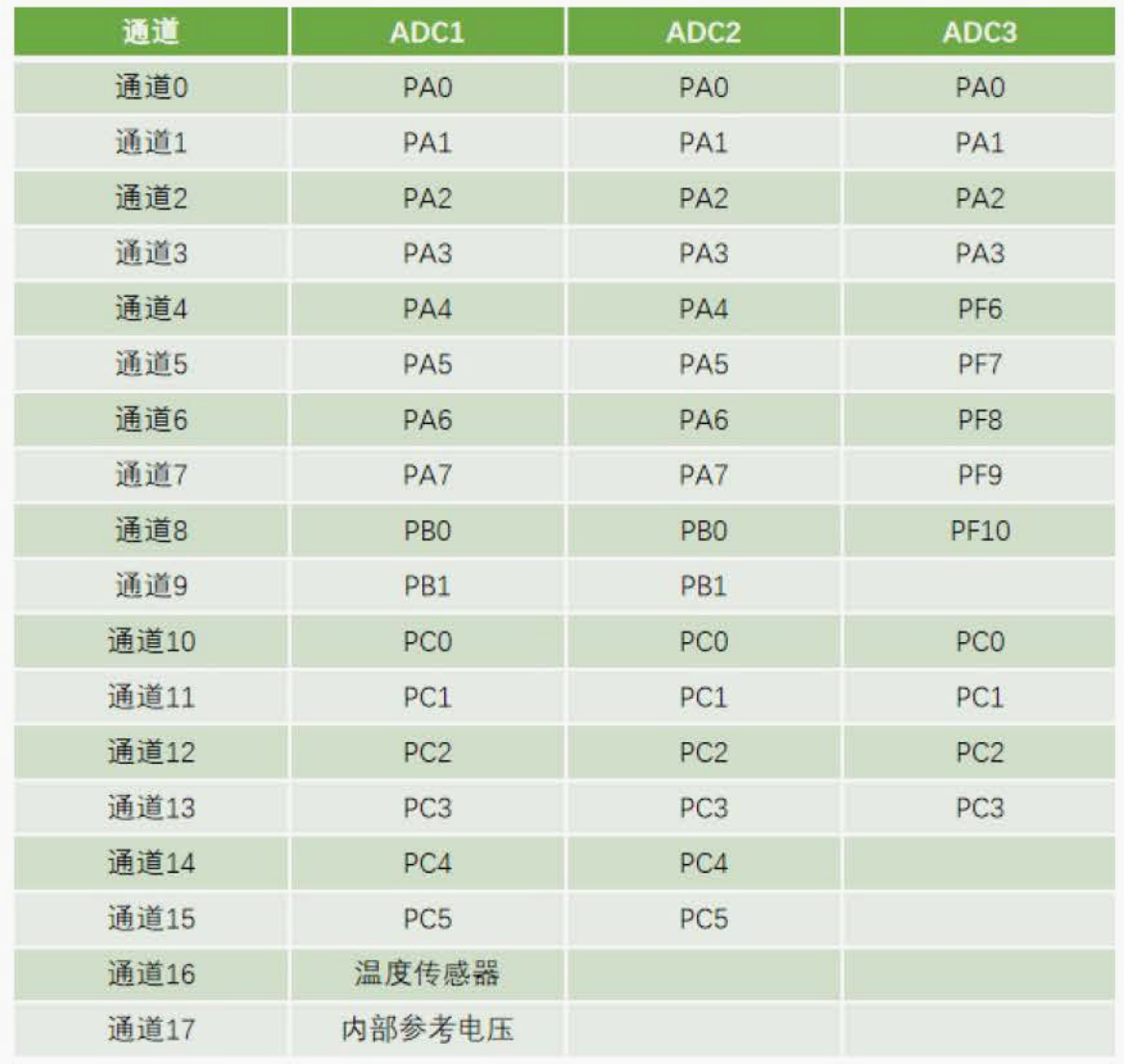

7.2.3STM32的ADC输入通道和引脚的关系

7.2.4 STM32的ADC规则组的四种转换模式

STM32中的ADC规则组的转换模式有以下四种:

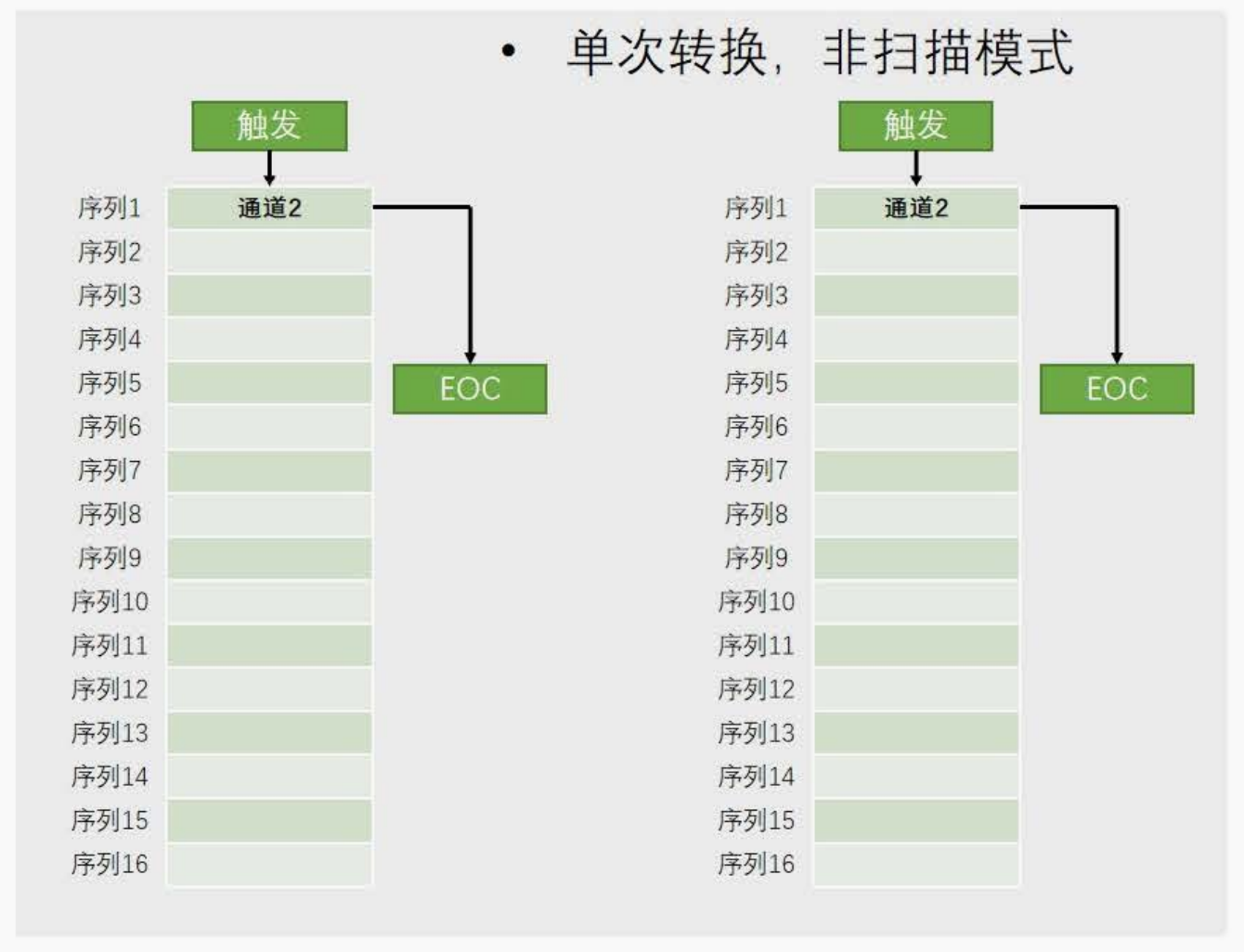

单次转换非扫描模式

单次转换扫描模式

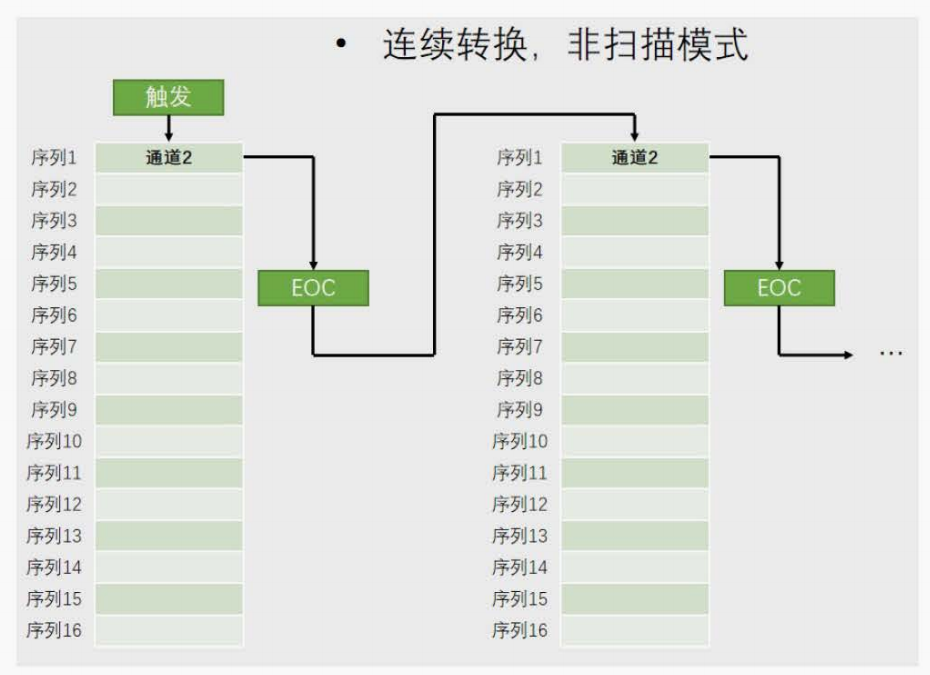

连续转换 非扫描模式

连续转换扫描模式

单次转换:每触发一次,转换结束就会停下来,下次转换就得再触发才能开始。

连续转换:一次转换完成后不会停止,而是立刻开始下一轮的转换,并持续下去。

非扫描模式:只对存放在序列1的通道起作用。

扫描模式:用到“菜单”列表,可以在菜单里点菜,每个菜单列表位置是通道几是可以任意指定的并且可以重复,然后初始化结构体有个通道数目的参数(表明用了几个通道),扫描模式下转换到数据寄存器的过程中,用DMA防止数据被覆盖,DMA进行数据及时转移;在扫描模式的情况下,还可以使用间断模式。它的作用是在扫描的过程中,每隔几次转换就暂停,需要再次触发才能继续。

1)单次转换非扫描模式

如下列表就是规则组的菜单,有16个空位,分别是序列1~16,单次转换非扫描模式下,只有序列1位置有效。通过选择该位置并指定需要转换的通道(如通道2),触发ADC进行模数转换。转换完成后,结果存储在数据寄存器中,并且EOC(转换完成标志位)被置为1。若要进行下一次转换,需要重新触发转换,并在序列1位置更新通道。

2)连续转换非扫描模式

连续转换非扫描模式与单次转换非扫描模式不同,它在一次转换完成后不会停止,而是立即开始下一轮转换,持续进行。只需初次触发转换,之后系统会自动不断转换,无需手动操作或判断是否结束。读取AD值时,直接从数据寄存器中获取即可。

3)单次转换扫描模式

单次转换扫描模式下,每次转换结束后会停止,下一次转换需要重新触发。该模式使用“菜单”列表,可以指定并重复选择不同的通道。在初始化时,结构体会设置通道数量参数,指明使用的通道数。每次触发后,系统会依次对前7个通道进行AD转换,转换结果存放在数据寄存器中。为防止数据被覆盖,需要使用DMA将数据转移。7个通道的转换完成后,产生EOC信号,标志转换结束,随后触发下一轮转换。

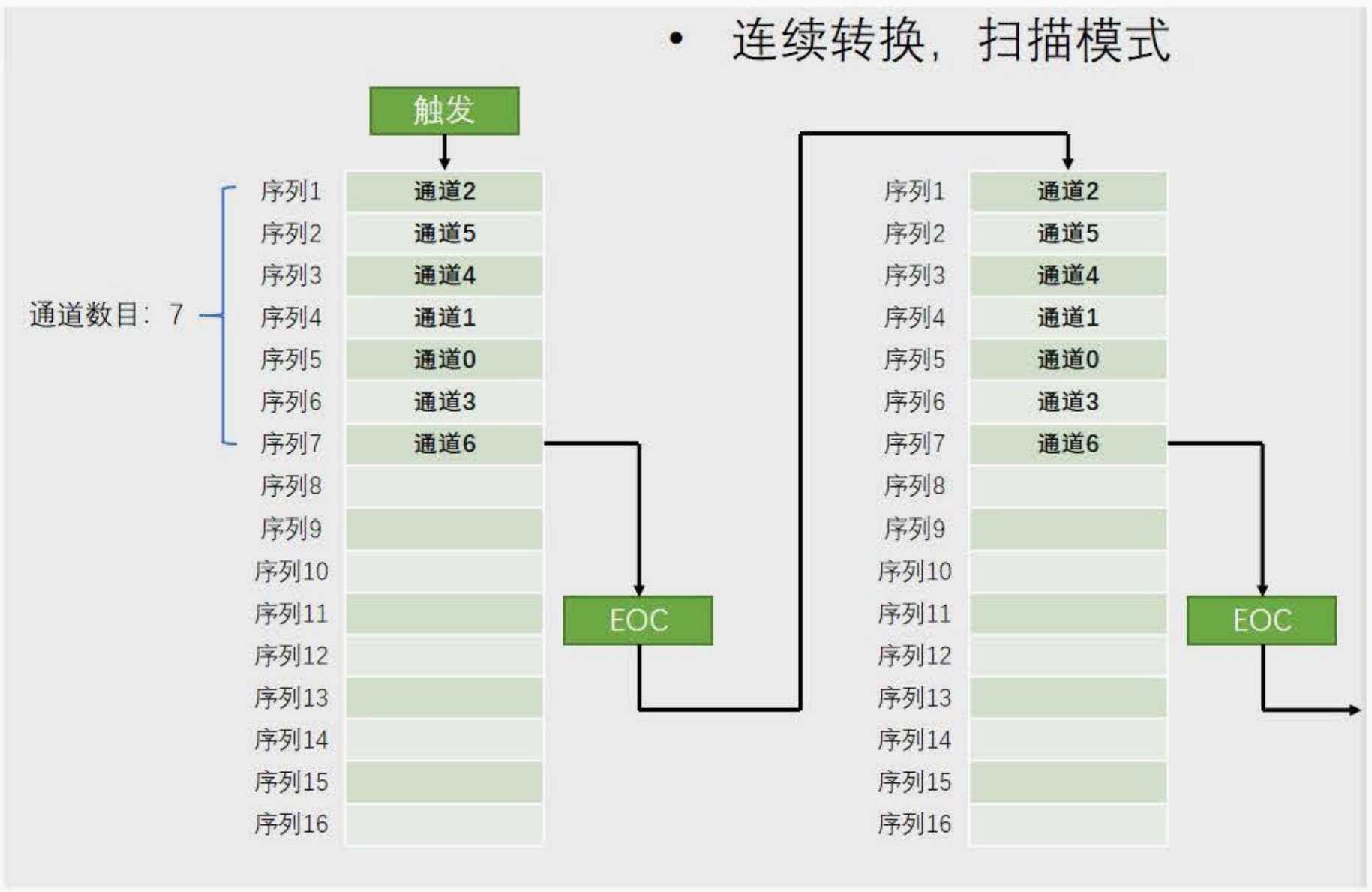

4)连续转换扫描模式

连续转换扫描模式与单次转换扫描模式不同之处就是一次转换完成后,立刻进行下一次的转换

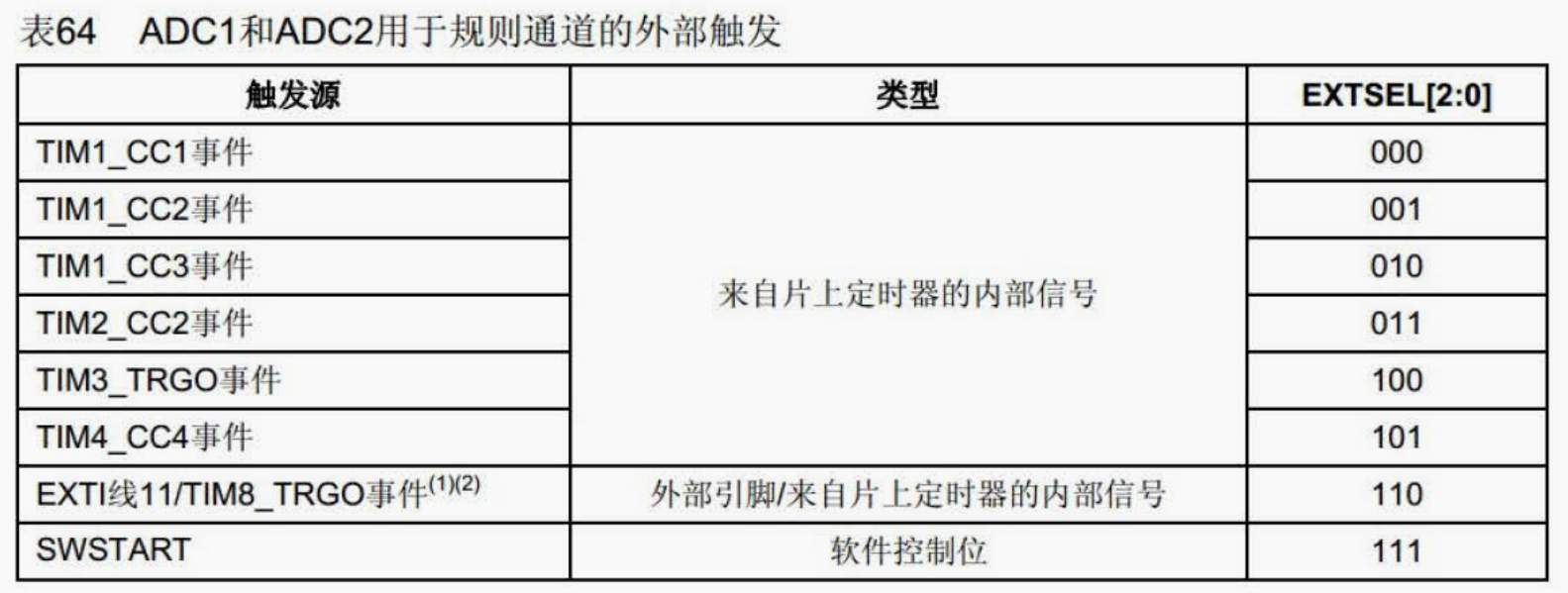

7.2.5STM32的ADC规则组的触发源

规则组的触发源如下表所示

有来自定时器的信号、来自引脚或定时器的信号(具体是引脚还是定时器需要用AFIO重映射来确定)、软件控制位(就是软件触发)。

触发信号的选择可以通过设置寄存器来完成EXTSEL[2:0],当然使用库函数的话直接给一个参数就行了。

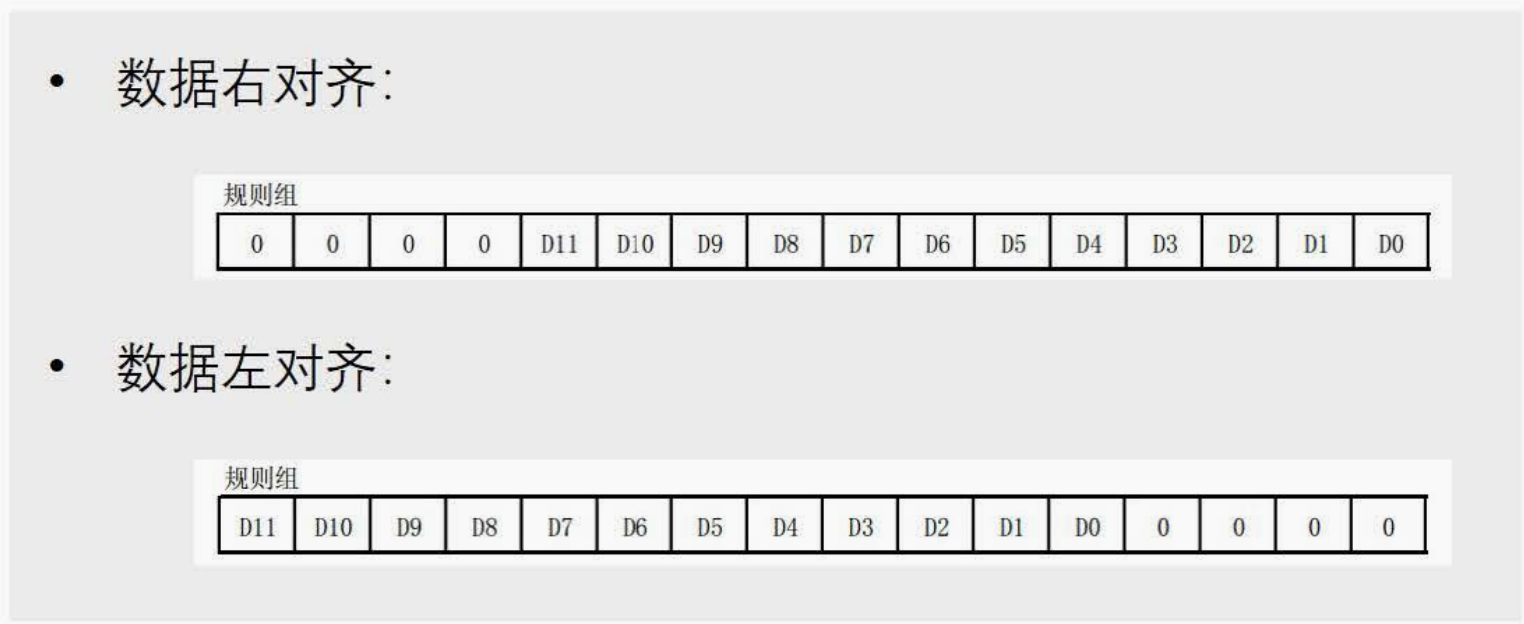

7.2.6数据对齐

STM32中的ADC是12位的,但是数据寄存器拥有16位,故存在数据对齐的问题。

数据右对齐,即作为转换结果的12位数据向右靠,高位补0;

数据左对齐,即作为转换结果的12位数据向左靠,低位补0.

在使用时通常使用数据右对齐,这样在读取时直接读取寄存器即可。如果选择左对齐直接读取,得到的数据会比实际的数据大16倍。当对分辨率的要求不高时(对电压仅作大概的判断即可)可以采用左对齐,将数据寄存器的高8位取出,就相当于舍弃了转换结果的4位的精度,12位的ADC退化位为8位的ADC。

7.2.7AD转换时间

1)AD转换的步骤:采样,保持,量化,编码

采样和保持可以看作是一个过程,量化和编码是另一个过程。量化和编码即为ADC的逐次比较过程,位数越高的ADC转换时间越长。采样和保持的作用是确保在量化和编码时输入电压变化不会过大。在量化和编码前,需要通过采样-保持电路保证电压稳定,这通常通过设置采样开关来实现,开关打开一段时间收集电压,并通过电容存储,收集完成后断开开关,再进行后续的AD转换。这样可以确保电压稳定,避免变化。ADC的采样时间较长,可以在程序中配置。接下来,量化和编码过程花费12个ADC周期,剩余的0.5周期用于完成其他工作。

2)STM32ADC的总转换时间为:

TCONV=采样时间+12.5个ADC周期

例如:当ADCCLK=14MHz,采样时间为1.5个ADC周期

TCONV=1.5+12.5=14个ADC周期=1μs

ADC周期就是从RCC分频过来的ADCCLK,ADCCLK最大是14MHz

最短的转换时间:当ADCCLK=14MHz,采样时间为1.5个ADC周期时:ADC总转换时间为1us。这就是最快1us时间的来源,如果采样周期再长些就达不到lus了。当然,可以通过设置将ADC的转换频率超过14MHz,这样ADC就会工作在超频状态下。超频时转换时间可能会更短,不过电路的稳定性将无法保证。

7.2.8ADC校准

ADC有一个内置自校准模式。校准可大幅减小因内部电容器组的变化而造成的准精度误差。校准期间,在每个电容器上都会计算出一个误差修正码(数字值),这个码用于消除在随后的转换中每个电容器上产生的误差。

建议在每次上电后执行一次校准。

启动校准前,ADC必须处于关电状态超过至少两个ADC时钟周期。

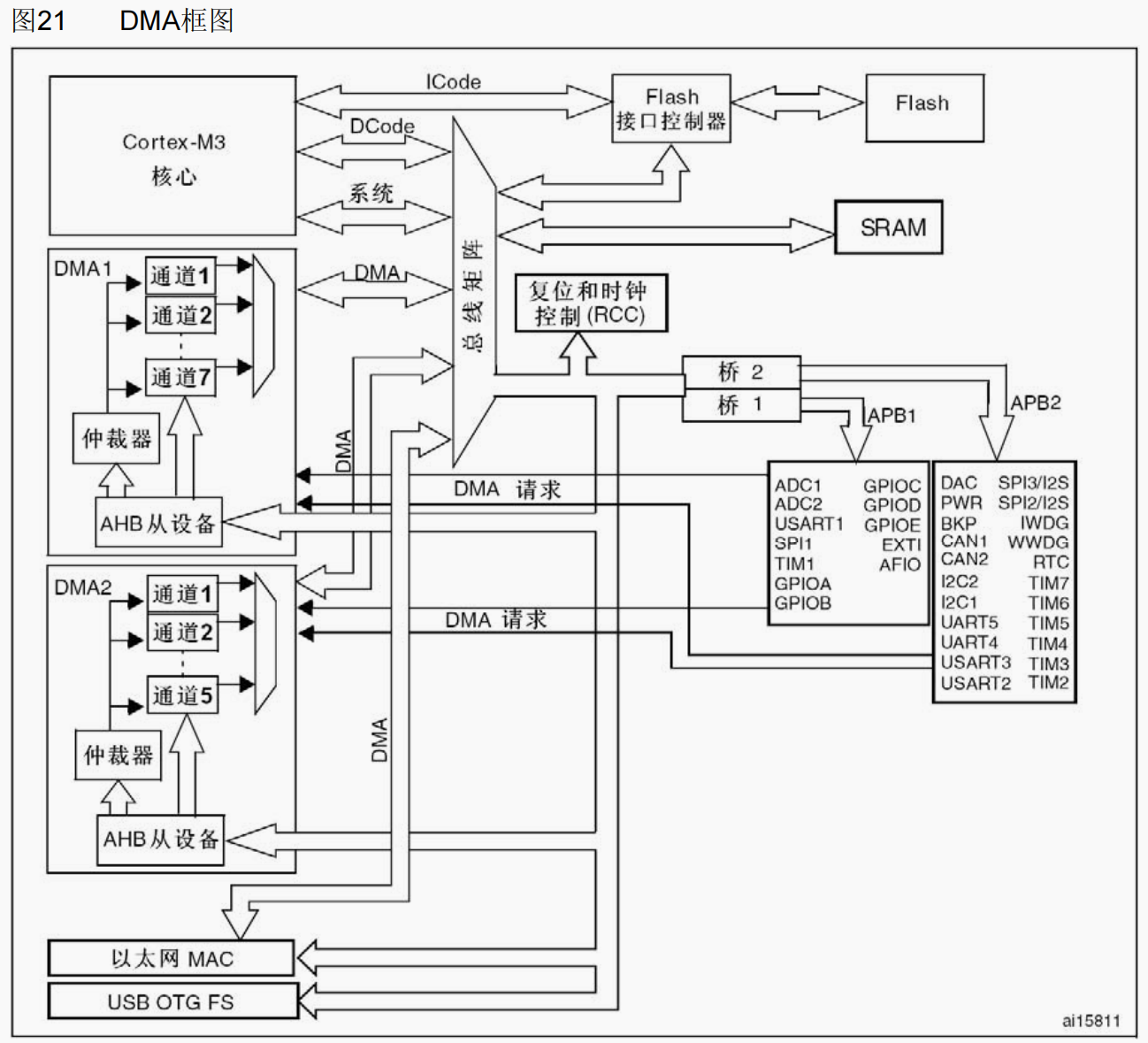

8DMA直接存储器存取

8.1DMA简介

1)DMA(DirectMemoryAccess)直接存储器存取

数据转运小助手,协助CPU完成数据转运工作,DMA可以提供外设和存储器或者存储器和存储器之间的高速数据传输,无须CPU干预,节省了CPU的资源

外设:一般指的是外设的数据计算器DR,dataregister,比如ADC的数据寄存器、串口的数据寄存器等等,

存储器:运行内存SRAM和程序存储器Flash,是存储变量数组和程序代码的地方

2)12个独立可配置的通道:DMA1(7个通道),DMA2(5个通道)

从一个地方移动到另一个地方,需要占用一个通道,DMA多通道进行运转时候,之间可以各转各的互不干扰

3)每个通道都支持软件触发和特定的硬件触发

在存储器到存储器的数据转运中,例如将flash数据转运到SRAM,DMA在软件触发后会快速完成所有数据传输。而在外设到存储器的数据转运中,由于外设数据具有时序要求,必须通过硬件触发来控制传输。例如,在ADC数据传输过程中,DMA需要在每个通道的AD转换完成后由硬件触发一次,才能确保数据传输的正确性。每个DMA通道的硬件触发源不同,因此需要根据外设选择对应的通道,而不能随意选择。

8.3DMA基本结构

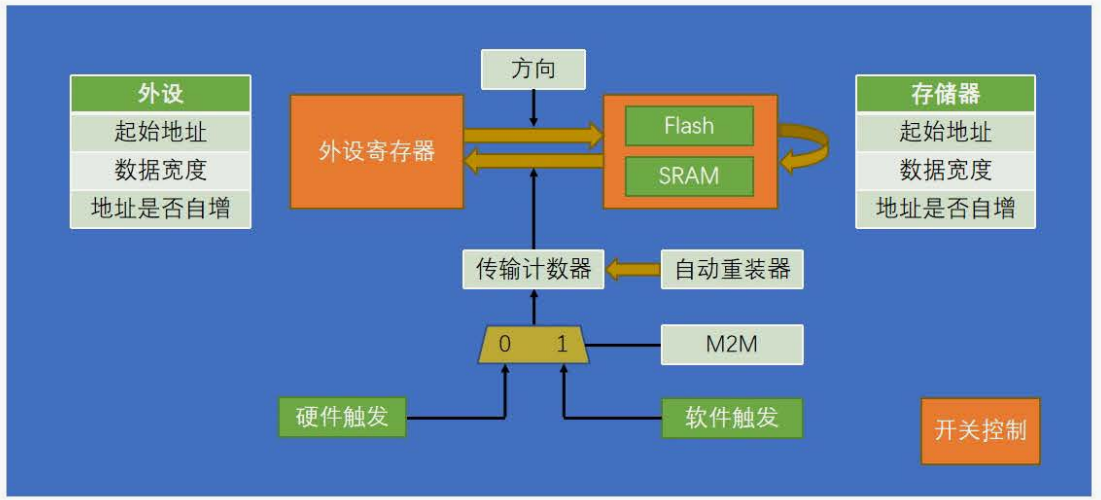

DMA基本结构框图如下所示:

DMA(直接内存存取)在数据传输中的使用和控制如下:

1)两个站点:

外设寄存器站点和存储器站点(如Flash和SRAM)。数据传输只能从Flash到SRAM因为Flash是只读的。

2)外设和存储器的三个参数:

起始地址:外设和存储器的起始地址决定了数据的来源和去向。

数据宽度:确定每次传输的数据大小,支持字节(8位)、半字(16位)和字(32位)。

地址是否自增:指定数据传输完成后,地址是否自动增加。比如,ADC扫描模式下外设地址不需要自增,而存储器地址需要自增,以避免覆盖数据。

3)两个站点的使用:

存储器到存储器的数据传输时,一个存储器的地址可以放在外设寄存器站点中,通过修改站点地址来决定数据来源和去向。

4)传输计数器:指定需要传输的次数,每传输一次自减,计数器为0时停止传输。

5)自动重装器:是否在传输计数器归零后自动恢复到初始值,决定传输是单次还是循环模式。

6)DMA触发控制:

触发源可以是硬件或软件。软件触发适用于存储器到存储器的数据转运,硬件触发适用于外设到存储器的转运。

软件触发:快速完成数据传输,适用于存储器到存储器的转运。

硬件触发:外设(如ADC、串口等)达到时机时触发DMA进行数据传输。

7)DMA进行转运的条件:

必须启用DMA(DMA_Cmd 使能)。

传输计数器大于0.

需要触发信号来启动传输。