Chiplet封装革命:路登多芯片同步固晶治具支持异构集成

Chiplet封装革命:路登多芯片同步固晶治具如何赋能异构集成

Chiplet封装革命:路登多芯片同步固晶治具如何赋能异构集成

◼ 时代的挑战:Chiplet与异构集成的制造难题

传统的单颗芯片(Monolithic)封装模式已逐渐逼近物理和经济的极限。“Chiplet”(芯粒)模式通过将一个大芯片拆分成多个小芯片,再通过先进封装技术集成在一起,已成为半导体行业延续摩尔定律的主流路径。这种“异构集成”带来了巨大优势,但也引入了前所未有的制造挑战:

多芯片、多尺寸:一个封装体内需要集成来自不同工艺节点、不同功能的芯片(如CPU、GPU、IO芯粒、HBM内存等)。这些芯片尺寸、厚度可能各不相同。

共面性要求极高:所有Chiplet的背面必须处于高度一致的同一平面上。任何微小的落差都会导致:

后续键合(Hybrid Bonding/热压键合)失败:连接界面压力不均,造成连接开路或短路。

散热不良:与散热盖接触不均,局部过热。

机械应力:封装后内部应力集中,导致可靠性下降。

效率与精度瓶颈:传统单颗芯片依次固晶的方式效率低下,且多次进出加热环境会导致基板氧化和热应力累积,影响精度和良率。

◼ 技术破局:路登多芯片同步固晶治具的核心创新

◼ 技术破局:路登多芯片同步固晶治具的核心创新

“路登多芯片同步固晶治具”正是为解决上述挑战而生的尖端解决方案。其核心理念是:一次性、同步地完成所有异构Chiplet的贴装。

它的工作原理和关键技术特点包括:

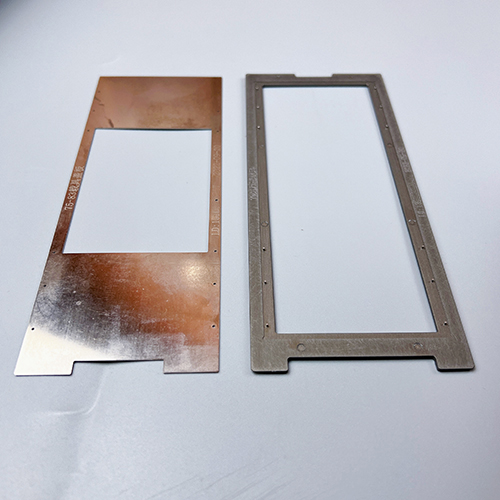

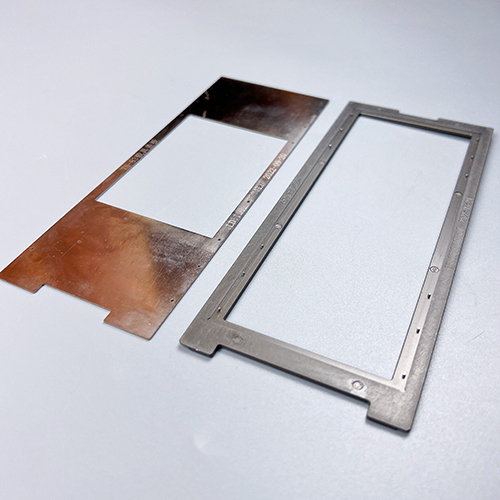

高精度仿形腔体与独立芯片腔位:

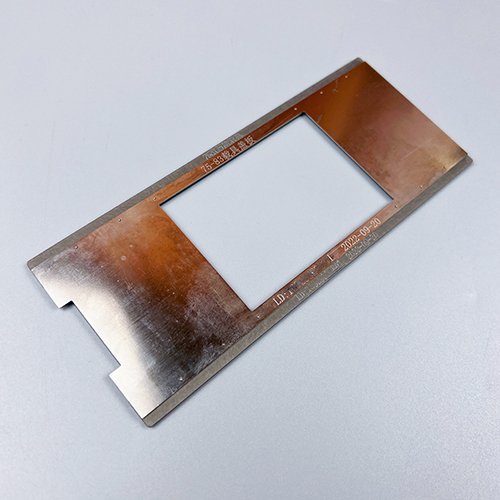

治具本体拥有一个与封装基板(Substrate)精确匹配的型腔。

关键在于,其上盖或压板部分为每一个Chiplet都设计了一个独立的、深度可调的精密腔位(Pocket)。这些腔位的深度是根据每颗Chiplet的目标贴装高度(通常等于芯片厚度 + 焊料/粘结剂厚度)预先精密加工设定的。

多区域独立压力控制:

每个芯片腔位背后可能集成了独立的微压力系统(如气动、弹簧或压电陶瓷驱动)。

这使得治具能够为不同尺寸、不同承压能力的Chiplet提供量身定制的、均匀的贴装压力,避免压碎脆弱的小芯片或对大片施加压力不足。

全局平面度控制与真空吸附:

治具本身由超低热膨胀系数(CTE)材料(如殷钢、高性能合成石)制成,确保在固晶高温环境下保持极高的整体平面度。

强大的真空吸附系统将基板牢牢拉平固定在治具基准面上,消除了基板自身翘曲的影响。

同步贴装工艺:

操作时,将所有Chiplet预先放置在各目的腔位中,涂覆好粘结材料(环氧胶、烧结银浆等)的基板被放入治具。

合上治具并加压加热,所有Chiplet在其独立的腔位引导下,被同步压至目标高度。多余的粘结材料被均匀挤出,最终确保所有芯片背面达到极高的共面性。

◼ 如何支持并推动异构集成革命?

◼ 如何支持并推动异构集成革命?

实现卓越的共面性:这是其最核心的价值。它将不同尺寸的Chiplet的贴装高度差控制在微米级甚至亚微米级,为后续的微凸点(Microbump)连接或混合键合(Hybrid Bonding)提供了完美的界面基础,直接提升了集成良率和可靠性。

提升生产效率和吞吐量:一次性完成所有芯片贴装,大幅减少了生产节拍,相比顺序贴装(Pick & Place)效率可提升数倍,更适合大规模量产。

保护脆弱芯片:独立的压力控制避免了“大芯片压小芯片”的风险,特别适合集成高价值的、易损的芯粒(如HBM)。

兼容多种材料:无论是用于粘接的环氧树脂、烧结银,还是用于热压键合的非导电薄膜(NCF),该治具都能提供均匀的热量和压力环境,确保工艺一致性。

◼ 总结与展望

“路登多芯片同步固晶治具”并非一个简单的工装,它是Chiplet从设计走向高效、高良率制造的关键赋能工具。它解决了异构集成制造中最棘手的“高度差”问题,使得将不同工艺、不同功能、不同尺寸的“乐高积木”芯片完美拼合在一起成为可能。

这项技术创新极大地推动了Chiplet封装技术的成熟和商业化落地,是 behind the scenes 的“幕后英雄”,为下一代高性能计算(HPC)、人工智能(AI)芯片和先进处理器的制造提供了坚实的技术保障。它代表了先进封装设备领域与芯片设计协同进化的重要方向