硬件驱动芯片——I.MX6ULL芯片(1)

I.MX6ULL——cortex —A7架构

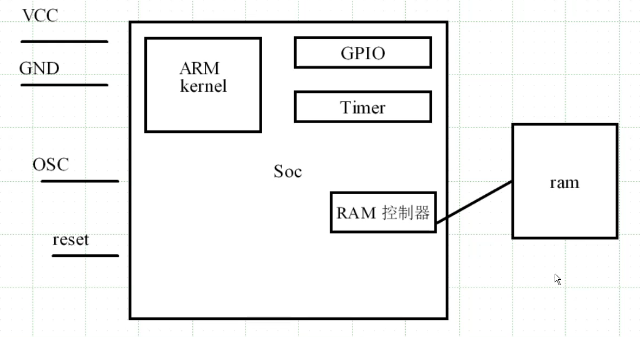

一.ARM内核

ARM——公司名

CPU内核:

CISC(X86系统):complex istruction set computer 复杂指令集电脑 28效应 高能耗,高效率

RISC(RAM):reduced istruction set computer 精简指令集电脑 低能耗高效率

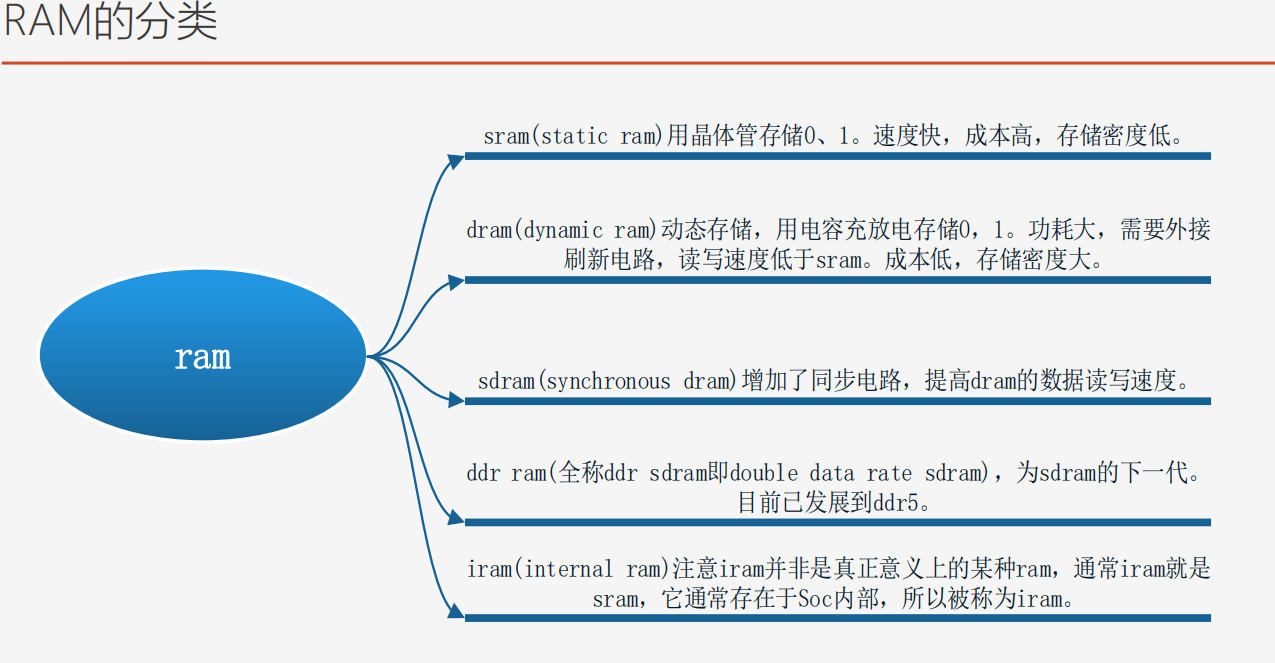

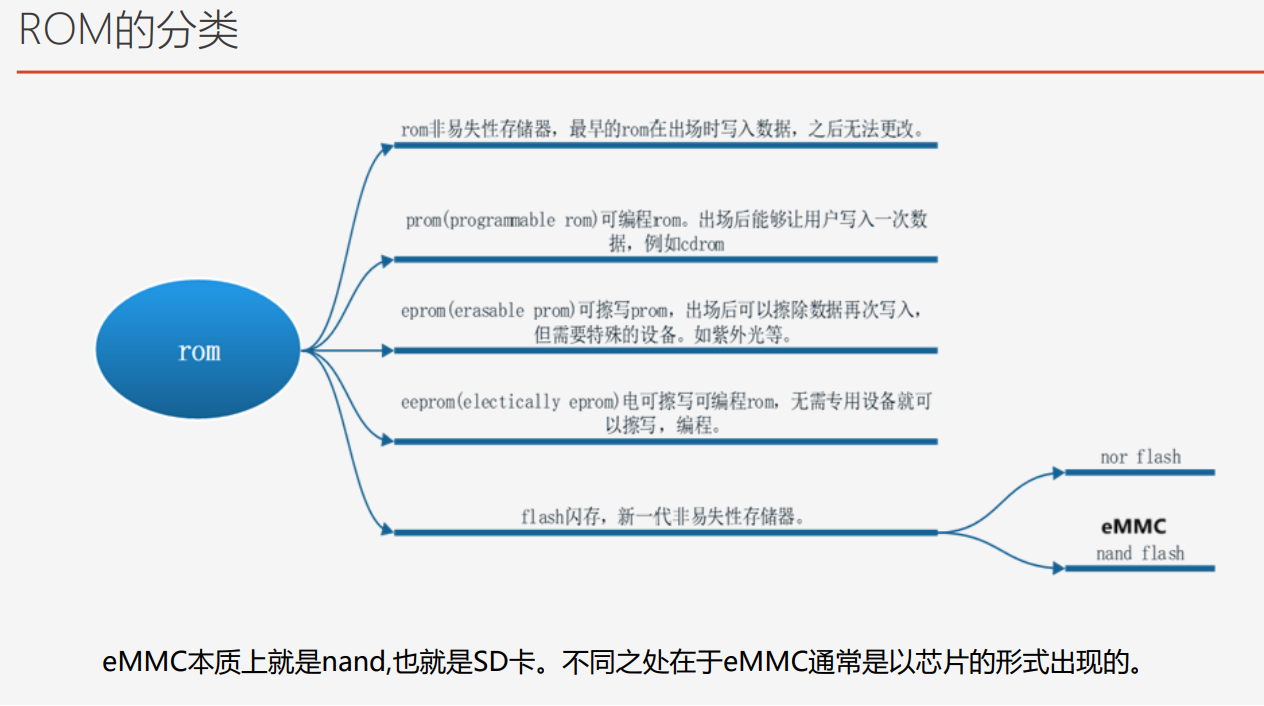

ram:随机访问存储器(易失性存储器) rom:只读存储器(非易失性存储器)

连接kernel和外设通信的线为桥

AHB:先进高速总线 APB(peripherals):先进外设总线

arm公司最先推出的是arm1~11

然后推出cortex系列

cortex系列:A系列:application(应用)手机电脑

M系列:Microcontroller (微控制领域)单片机

R系列:实时 军事,航空,航天

cortex—A7 —>32bit ARM kernel

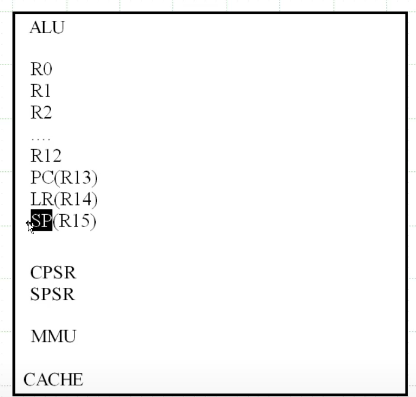

R0~R12:通用寄存器(内核)

ALU:算术逻辑单元

PC(R15):program Couter 程序寄存器(本质是指针)

PC指到那,程序就运行到那

LR(R14):linked rigister 链接寄存器

SP(R13):stack point 栈指针寄存器(栈顶地址)

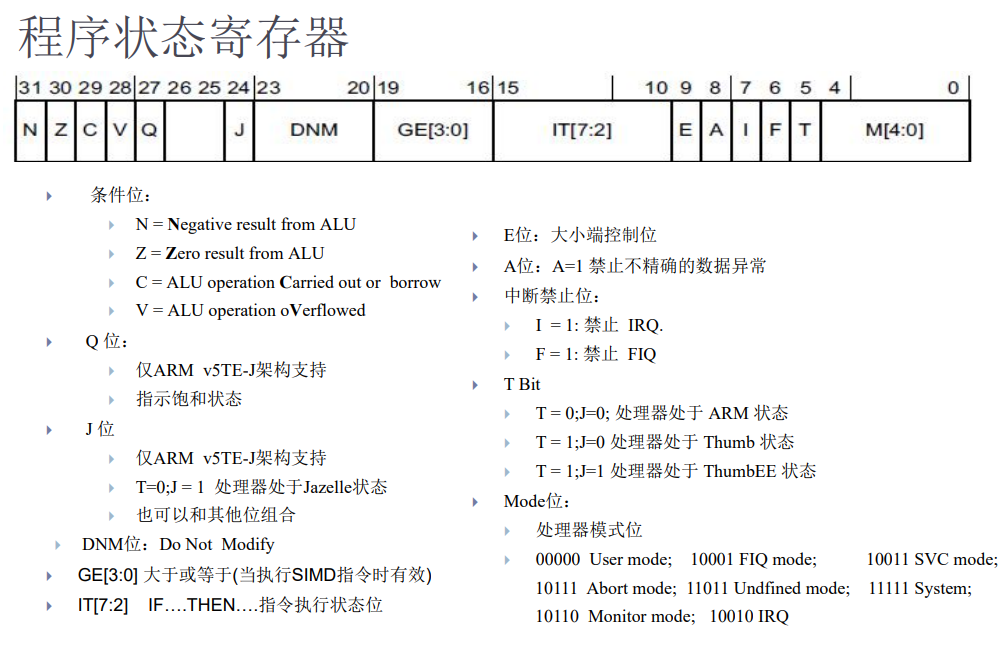

CPSR(当前程序状态寄存器):current program status register

SPSR(保存/备份寄存器):saved program status register

MMU(内存管理单元):mermory management unit 虚拟内存空间和物理内存映射(提高物理内存的使用效率)

CACHE:高速缓存单元(提高效率)

instruction cache:指令cache

data cache:数据cache

冯诺依曼架构:data和instruction放在一块 哈佛架构:data和instruction分开放

二.RAM分类

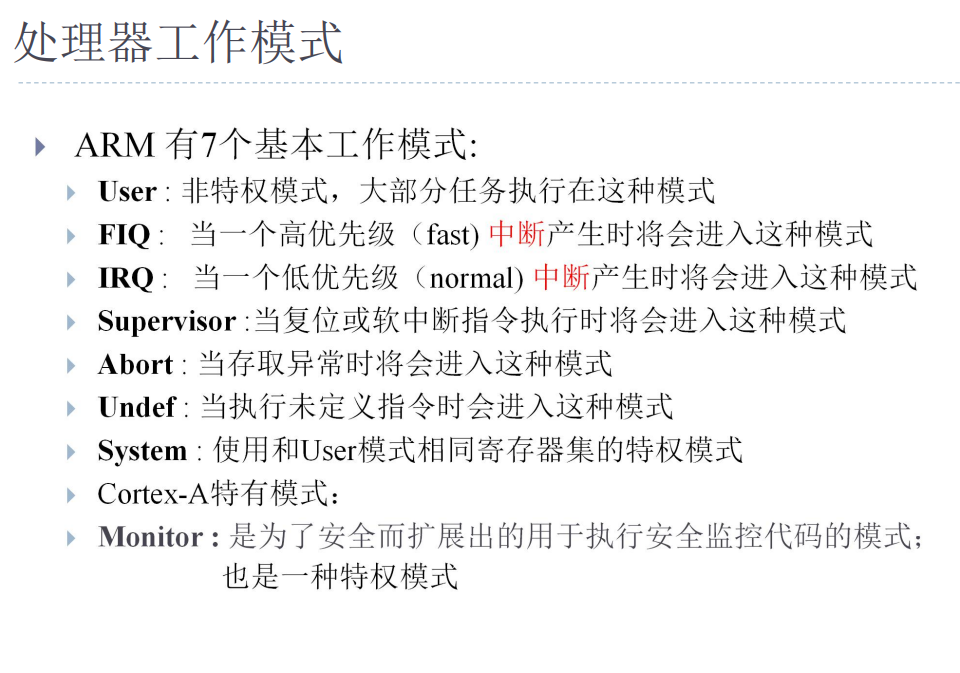

三.ARM的工作模式——>处理器的工作状态

七种工作模式:

软中断=软件中断

cortex有九种工作模式

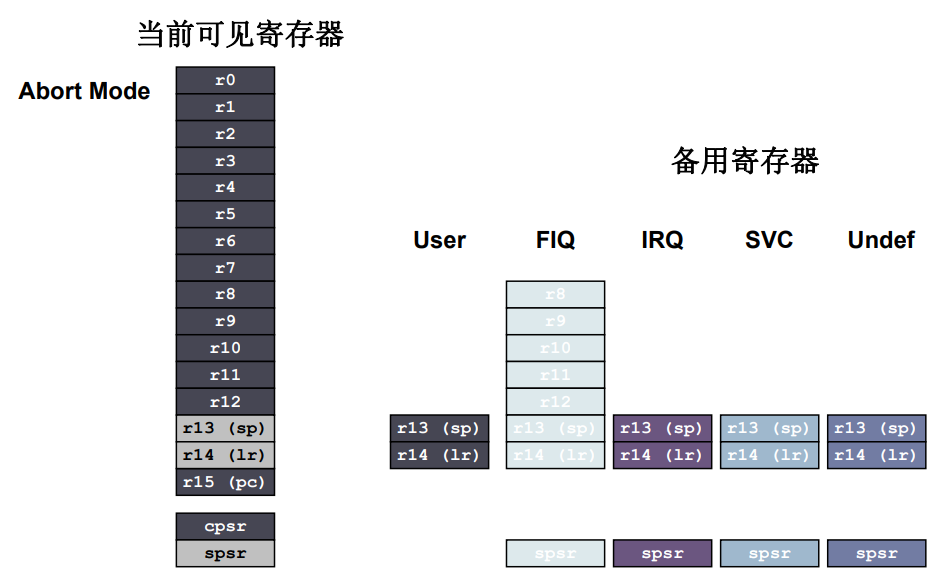

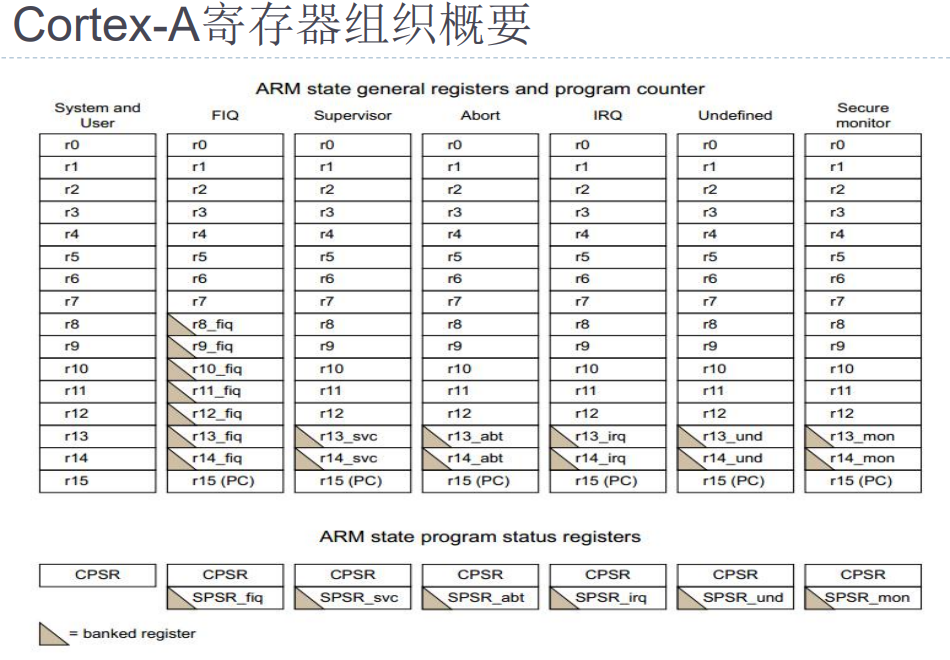

arm中有37个寄存器,cortex-A体系下有40个寄存器

C:整形溢出C位为0

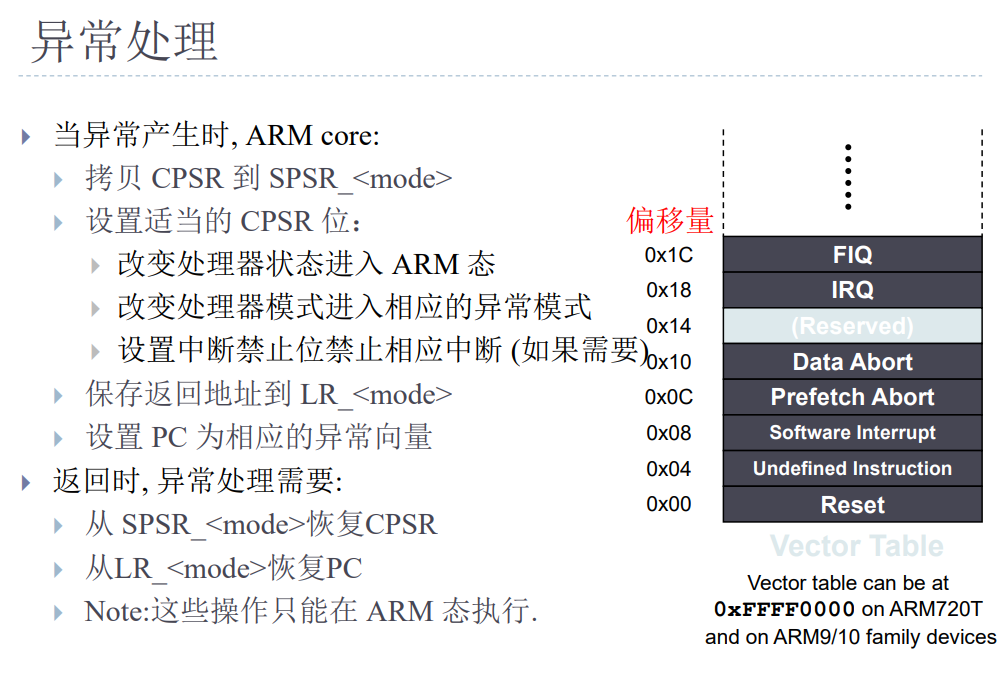

四.异常处理

异常向量表:

异常向量表是内存中一组固定地址的存储单元,每个地址对应一种异常类型(如复位、IRQ、FIQ 等)。当异常发生时,ARM 内核会自动跳转到向量表中对应异常的地址,执行该地址存放的异常处理程序(通常是跳转指令,指向实际处理代码)。

不同 ARM 架构的向量表地址可能不同(如 ARM9 默认从 0x00000000 开始),每个异常的向量地址固定(如复位向量在 0x00,IRQ 向量在 0x18),确保异常能被快速响应

五.ARM编程规则

1.MOV {s}<c> <Rd>, #<imm8>

{s}<c>:可省略 <Rd> 目标寄存器 <imm8> 常量

2.MOV {s}<c> <Rd>,<Rm>

<Rm>为第一操作数

3.MOV {s} <Rd>,<Rm>,ASR #<n>

ASR:算术右移(右移时保留符号位(用最高位填充)) <n>立即数移位(移位的位数) LSL:逻辑左移(左移时低位补0) LSR:逻辑右移(右移时高位补0) ROR:循环右移(右移时移出的位循环填入高位)

4.MOV {s} <Rd>,<Rm>,ASR <Rs>

<Rs>寄存器移位(位移量由寄存器Rs的低8位决定)