【PZ-A735T-KFB】璞致fpga开发板 Artix-7 系列之PA-Starlite-初学入门首选 开发板用户手册

第一章: Artix-7 系列介绍

Artix-7 系列:相对于 Spartan-6 系列而言,Artix-7 系列功耗降低了一半, 成本降低了 35%,采用小型化封装、统一的 Virtex 系列架构,能满足低成本大批量市场的性能要求,这也正是此前 ASSP、ASIC 和低成本 FPGA 所针对的市场领域。新产品系列既能满足电池供电的便携式超声波设备的低功耗高性能需求,又能满足商用数码相机镜头控制的小型、低功耗要求,还能满足军用航空电子和通信设备严格的 SWAP-C(大小、重量、功耗和成本

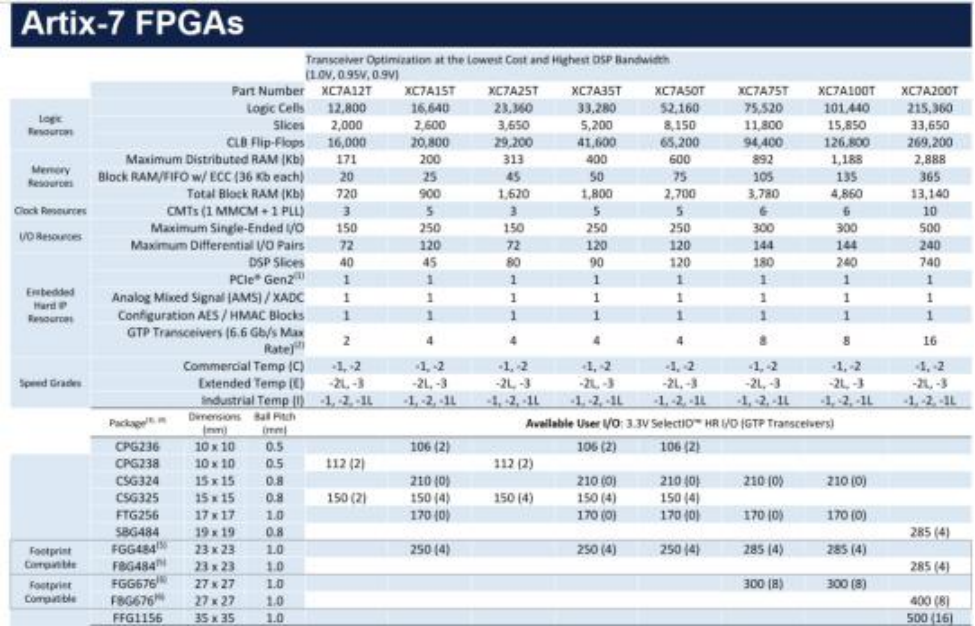

Artix-7 器件资源如下表列出,我们选用35/75/100/200 做为开发板的主控芯片:

第二章: PA-Starlite 开发板概述

2.1.板卡概述

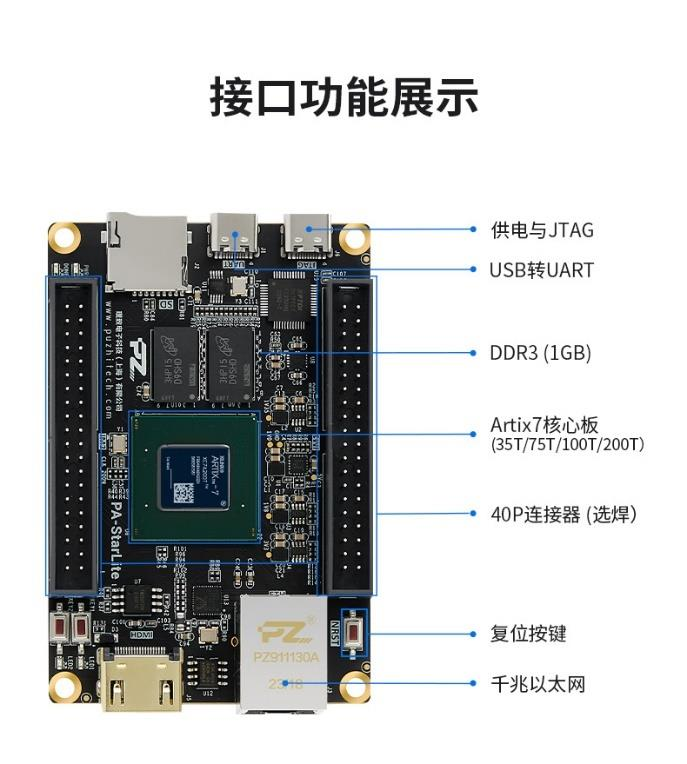

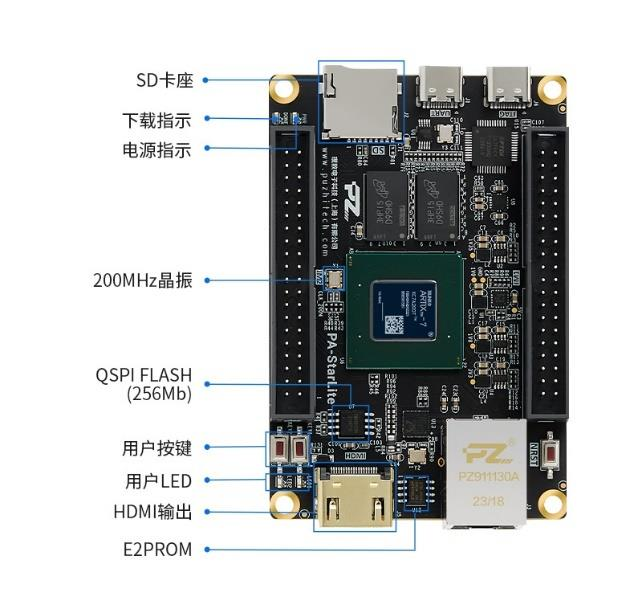

璞致电子科技 Artix-7 系列开发板提供了四个版本,使用XILINX 公司的

XC7A35T-2FGG484I/XC7A75T-2FGG484I/XC7A100T-2FGG484I/XC7A200T-2FBG484I 作为主控制器,我们根据主控芯片的不同分别命名开发板名字为 PA35T-Starlite

/PA75T-Starlite/PA100T-Starlite/PA200T-Starlite,其中 PA35T-Starlite 不带Mipi 接口,其他三款管脚完全兼容。

璞致电子科技 PA-Starlie 系列开发板每款板卡都提供带 40P 连接器和不带40P 连接器两个版本。方便了用户作为开发板或者当成项目核心板使用。

另外,开发板集成了丰富的外设资源,提供了详尽的开发例程,加速了用户学习进度。除此之外,开发板还集成了 JTAG 调试器,做到了一根 USB 线就可以实现供电和调试两用,使用更加便捷。

关于开发板的详细说明,可以查阅下文对应章节。

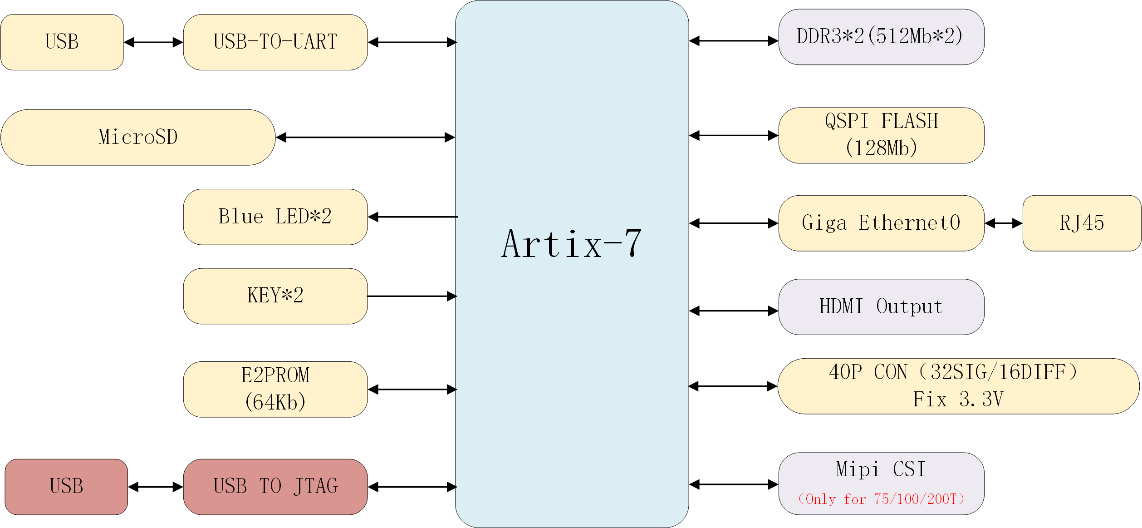

2.2.开发板资源和框图

如下分别为开发板的框图和板载资源表,用户可对比查看。

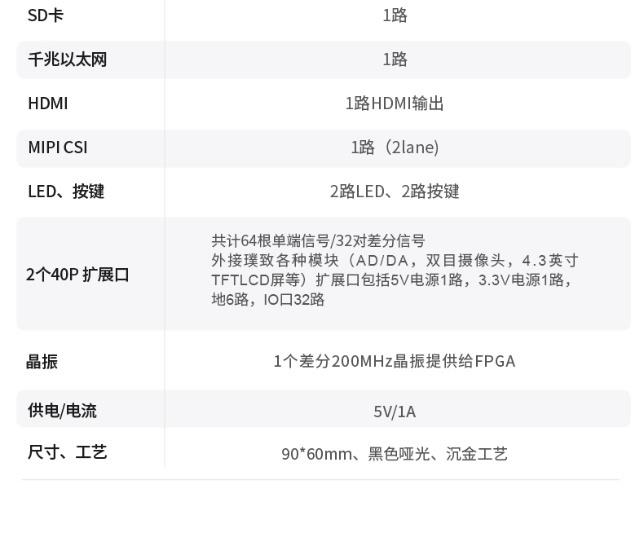

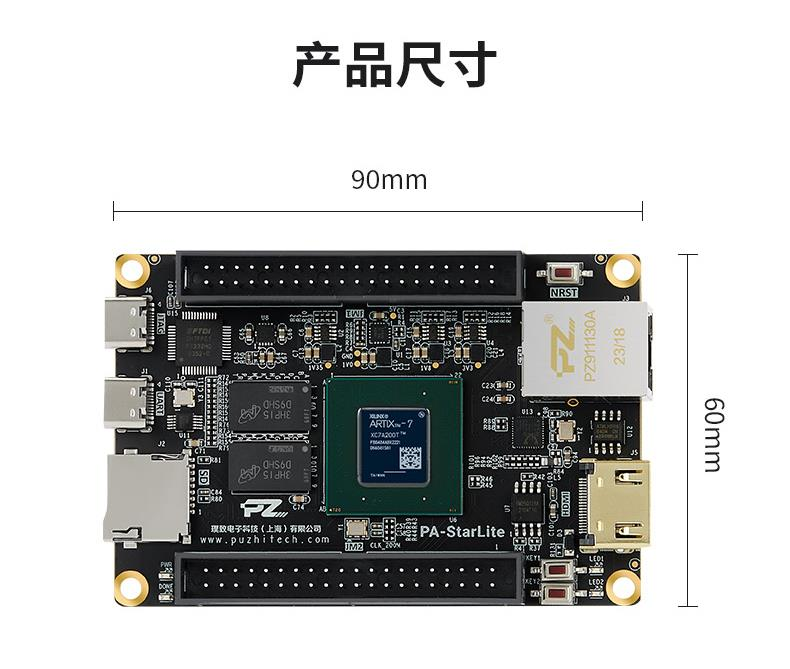

2.3.开发板尺寸

如下图标出开发板尺寸为 90x60mm,开发板的四个角各放置一个固定孔,用于安装支撑柱或固定单板,孔径为 3.5mm。如下图以 PA200T-Starlite 为例,其他三款尺寸跟 PA200T-Starlite 一样大。

第三章: 璞致 PA-Starlite 开发板接口说明

3.1.关于供电

璞致 PA-Starlite 系列开发板提供了两种供电方式:一种是用 TypeC 线连接电脑给板卡提供 5V 电源;另一种是通过 40P 连接器上的排针给板卡提供 5V电源。两种供电方式二选一,根据用户实际需求来选用哪种供电。

采用 USB 线给板卡供电,即是当成开发板使用。采用40P 连接器供电,用户可以把板卡当成核心板,用户设计扩展底板,扩展其他功能。

3.2.系统时钟

开发板提供了一路 200M 差分时钟给主控芯片,连接的管脚名称分别为

IO_L13P_MRCC_34/ IO_L13N_MRCC_34,对应的管脚位置为 R4/T4。更详细说明可参考璞致提供的开发板原理图。

3.3.开发板复位

开发板上设计了一路复位按键,按键所在位置如图示,对应的管脚名称为IO_L19N_14,管脚位置为 R14。更详细说明可参考璞致提供的开发板原理图。

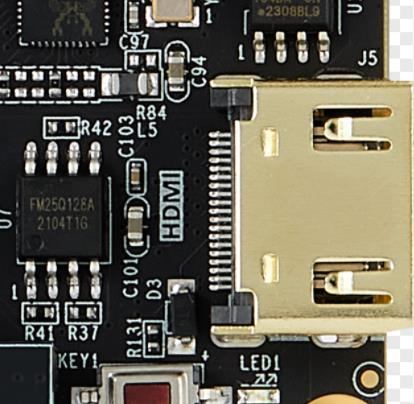

3.4.开发板启动方式

主芯片的启动模式分别是 JTAG、QSPI Flash,默认配置为 QSPI Flash 启动,但JTAG 模式优先级要高于 QSPI Flash,所以当用户连接了 JTAG 接口芯片优先从 JTAG启动,不用做启动模式切换。核心板上 QSPI Flash 容量为 128Mb,更详细说明可参考璞致提供的开发板原理图。

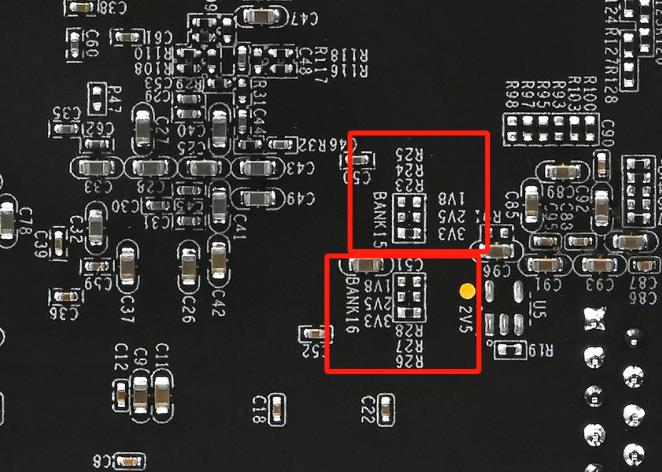

3.5.BANK 电平选择

开发板上连接到 40P 连接器上的 BANK15/16 为 HR BANK,为方便用户使用,我们设计了 IO 电平可以在 1.8/2.5/3.3V 三种电平下选择,默认电平为 3.3V,用户需要调节其他电平可以开发板上位置指示来调整 BANK 电平。 更详细说明可参考璞致提供的开发板原理图。

3.6.DDR3 资源

主芯片配置了两颗 DDR3,单颗容量 512Mb,共计 1GB,DDR3 管脚分配参见下表,更详细信息可参考璞致提供的原理图或者例程。

DDR3 引脚 | 管脚名称 | 管脚位置 |

DDR3_DQ0 | IO_L2P_35 | C2 |

DDR3_DQ1 | IO_L5P_35 | G1 |

DDR3_DQ2 | IO_L1N_35 | A1 |

DDR3_DQ3 | IO_L6P_35 | F3 |

DDR3_DQ4 | IO_L2N_35 | B2 |

DDR3_DQ5 | IO_L5N_35 | F1 |

DDR3_DQ6 | IO_L1P_35 | B1 |

DDR3_DQ7 | IO_L4P_35 | E2 |

DDR3_DM0 | IO_L4N_35 | D2 |

DDR3_DQS_P0 | IO_L3P_35 | E1 |

DDR3_DQS_N0 | IO_L3N_35 | D1 |

DDR3_DQ8 | IO_L11P_35 | H3 |

DDR3_DQ9 | IO_L11N_35 | G3 |

DDR3_DQ10 | IO_L8P_35 | H2 |

DDR3_DQ11 | IO_L10N_35 | H5 |

DDR3_DQ12 | IO_L7N_35 | J1 |

DDR3_DQ13 | IO_L10P_35 | J5 |

DDR3_DQ14 | IO_L7P_35 | K1 |

DDR3_DQ15 | IO_L12P_35 | H4 |

DDR3_DM1 | IO_L8N_35 | G2 |

DDR3_DQS_P1 | IO_L9P_35 | K2 |

DDR3_DQS_N1 | IO_L9N_35 | J2 |

DDR3_DQ16 | IO_L18N_35 | L4 |

DDR3_DQ17 | IO_L16P_35 | M3 |

DDR3_DQ18 | IO_L14P_35 | L3 |

DDR3_DQ19 | IO_L17N_35 | J6 |

DDR3_DQ20 | IO_L14N_35 | K3 |

DDR3_DQ21 | IO_L17P_35 | K6 |

DDR3_DQ22 | IO_L13N_35 | J4 |

DDR3_DQ23 | IO_L18P_35 | L5 |

DDR3_DM2 | IO_L16N_35 | M2 |

DDR3_DQS_P2 | IO_L15P_35 | M1 |

DDR3_DQS_N2 | IO_L15N_35 | L1 |

DDR3_DQ24 | IO_L20N_35 | P1 |

DDR3_DQ25 | IO_L19P_35 | N4 |

DDR3_DQ26 | IO_L20P_35 | R1 |

DDR3_DQ27 | IO_L22N_35 | N2 |

DDR3_DQ28 | IO_L23P_35 | M6 |

DDR3_DQ29 | IO_L24N_35 | N5 |

DDR3_DQ30 | IO_L24P_35 | P6 |

DDR3_DQ31 | IO_L22P_35 | P2 |

DDR3_DM3 | IO_L23N_35 | M5 |

DDR3_DQS_P3 | IO_L21P_35 | P5 |

DDR3_DQS_N3 | IO_L21N_35 | P4 |

DDR3_A0 | IO_L11N_34 | AA4 |

DDR3_A1 | IO_L8N_34 | AB2 |

DDR3_A2 | IO_L10P_34 | AA5 |

DDR3_A3 | IO_L10N_34 | AB5 |

DDR3_A4 | IO_L7N_34 | AB1 |

DDR3_A5 | IO_L6P_34 | U3 |

DDR3_A6 | IO_L5P_34 | W1 |

DDR3_A7 | IO_L1P_34 | T1 |

DDR3_A8 | IO_L2N_34 | V2 |

DDR3_A9 | IO_L2P_34 | U2 |

DDR3_A10 | IO_L5N_34 | Y1 |

DDR3_A11 | IO_L4P_34 | W2 |

DDR3_A12 | IO_L4N_34 | Y2 |

DDR3_A13 | IO_L1N_34 | U1 |

DDR3_A14 | IO_L15N_34 | W5 |

DDR3_BA0 | IO_L9N_34 | AA3 |

DDR3_BA1 | IO_L9P_34 | Y3 |

DDR3_BA2 | IO_L11P_34 | Y4 |

DDR3_nCS | IO_L8P_34 | AB3 |

DDR3_nWE | IO_L7P_34 | AA1 |

DDR3_nRESET | IO_L15P_34 | W6 |

DDR3_CLK_P | IO_L3P_34 | R3 |

DDR3_CLK_N | IO_L3N_34 | R2 |

DDR3_nWE | IO_L7P_34 | AA1 |

DDR3_nRAS | IO_L12P_34 | V4 |

DDR3_nCAS | IO_L12N_34 | W4 |

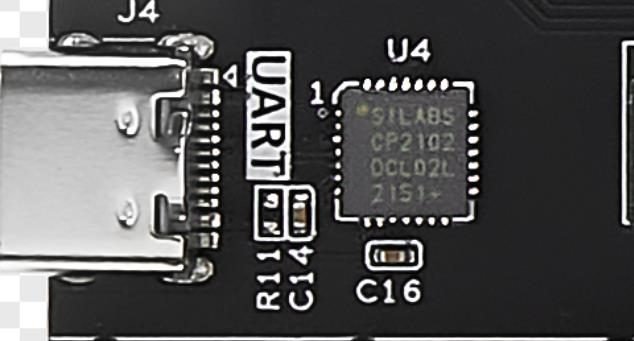

3.7.USB 转串口

开发板使用CH340E 芯片实现 USB 转 UART, USB 接口采用 TypeC 接口,用户只要用一根 USB 线连接到 PC 上即可进行串口通信。

UART 的 TX/RX 信号与 FPGA 的 BANK14 相连,接口电平为 3.3V。 如下是信号对应关系表和原理图。

UART 引脚 | 管脚名称 | 管脚位置 |

UART_TX | IO_L22P_14 | P15 |

UART_RX | IO_L19P_14 | P14 |

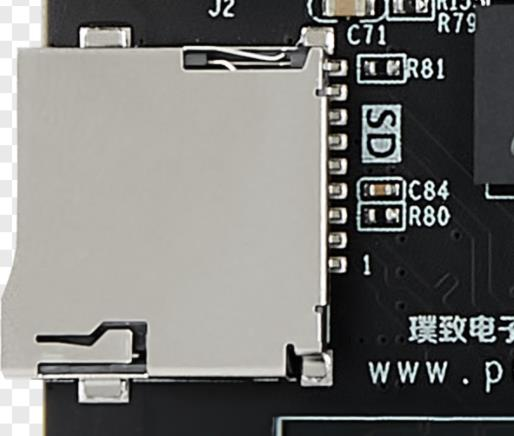

3.8.SD 卡

开发板上放置了一个 SD 卡座(开发板背面), SD 卡信号连接到 FPGA 的 BANK14上,接口电平为 3.3V。如下是信号对应关系,详细电路可以参考开发板原理图。

SD 卡引脚 | 管脚名称 | 管脚位置 |

SD-CLK | IO_L8P_14 | AA20 |

SD-CMD | IO_L10P_14 | AB21 |

SD-DATA0 | IO_L17N_14 | AB18 |

SD-DATA1 | IO_L17P_14 | AA18 |

SD-DATA2 | IO_L10N_14 | AB22 |

SD-DATA3 | IO_L8N_14 | AA21 |

3.9.E2PROM

开发板上放置了一颗 64Kbit 的 EEPROM 芯片,型号为 AT24C64D-SSHM-T,E2PROM通过 IIC 扩展芯片与 FPGA 的 BANK14 相连,接口电平为 3.3V。EEPROM 读地址是 0xA1,写地址是 0xA0。操作代码可参考璞致提供的例程,详细电路可以参考开发板原理图。

E2PROM | 管脚名称 | 管脚位置 |

E2PROM_I2C_SCL | IO_L23P_14 | N13 |

E2PROM_I2C_SDA | IO_L23N_14 | N14 |

3.10.千兆以太网

开发板上设计了一路千兆以太网,以太网芯片与 FPGA 之间通过 RGMII 接口互联,连接 BANK14,接口电平是 1.8V,连接对应管脚见下表,网口地址是PHY_AD[2:0]=001,详细电路可以参考开发板原理图。

RMGII 信号 | 管脚名称 | 管脚位置 |

GPHY_TX_CLK | IO_L21N_14 | P17 |

GPHY_TX_EN | IO_L22N_14 | R16 |

GPHY_TXD0 | IO_L5P_14 | P19 |

GPHY_TXD1 | IO_L24P_14 | P16 |

GPHY_TXD2 | IO_L21P_14 | N17 |

GPHY_TXD3 | IO_L24N_14 | R17 |

GPHY_RX_CLK | IO_L12P_14 | W19 |

GPHY_RX_DV | IO_L12N_14 | W20 |

GPHY_RXD0 | IO_L18N_14 | U18 |

GPHY_RXD1 | IO_L5N_14 | R19 |

GPHY_RXD2 | IO_L20P_14 | R18 |

GPHY_RXD3 | IO_L0_14 | P20 |

GPHY_MDC | IO_L20N_14 | T18 |

GPHY_MDIO | IO_L25_14 | N15 |

GPHY_nRST | IO_L6N_14 | T20 |

3.11.HDMI 接口

开发板设计了一路 HMDI 输出接口,管脚定义如下表,详细电路可以参考开发板原理图。

HDMI 信号 | 管脚名称 | 管脚位置 |

HDMI_DATA0_P | IO_L14P_14 | V18 |

HDMI_DATA0_N | IO_L14N_14 | V19 |

HDMI_DATA1_P | IO_L15P_14 | AA19 |

HDMI_DATA1_N | IO_L15N_14 | AB20 |

HDMI_DATA2_P | IO_L16P_14 | V17 |

HDMI_DATA2_N | IO_L16N_14 | W17 |

HDMI_CLK_P | IO_L13P_14 | Y18 |

HDMI_CLK_N | IO_L13N_14 | Y19 |

HDMI_CEC | IO_L18P_14 | W22 |

HDMI_I2C_SCL | IO_L4P_14 | T21 |

HDMI_I2C_SDA | IO_L11P_14 | U20 |

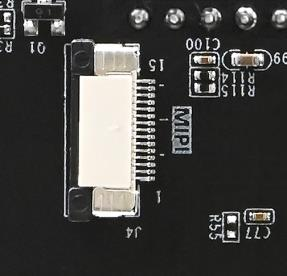

3.12.MIPI 接口

开发板设计了一路 MIPI 接口,管脚定义如下表,详细电路可以参考开发板原理图。

MIPI 信号 | 管脚名称 | 管脚位置 |

MIPI_LP_DATA_P0 | IO_L10P_13 | V10 |

MIPI_LP_DATA_N0 | IO_L10N_13 | W10 |

MIPI_LP_DATA_P1 | IO_L9P_13 | AA10 |

MIPI_LP_DATA_N1 | IO_L9N_13 | AA11 |

MIPI_DATA_P0 | IO_L12P_13 | W11 |

MIPI_DATA_N0 | IO_L12N_13 | W12 |

MIPI_DATA_P1 | IO_L11P_13 | Y11 |

MIPI_DATA_N1 | IO_L11N_13 | Y12 |

MIPI_LP_CLK_P | IO_L14P_13 | U15 |

MIPI_LP_CLK_N | IO_L14N_13 | V15 |

MIPI_CLK_P | IO_L13P_13 | V13 |

MIPI_CLK_N | IO_L13N_13 | V14 |

MIPI_CAM_nRST | IO_L15N_13 | T15 |

MIPI_CAM_CLK | IO_L15P_13 | T14 |

MIPI_IIC_SCL | IO_L16P_13 | W15 |

MIPI_IIC_SDA | IO_L16N_13 | W16 |

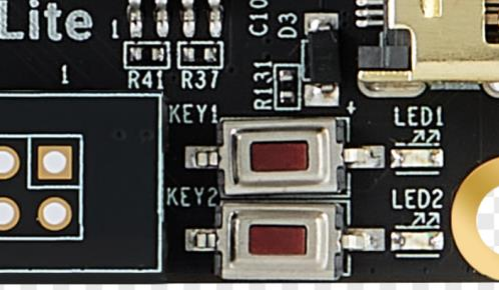

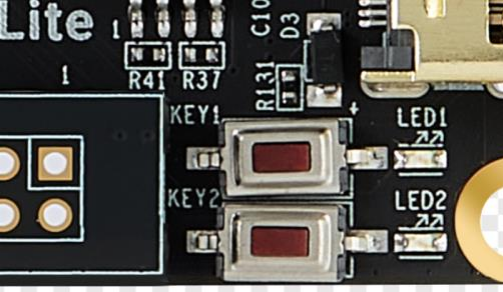

3.13.LED

开发板设计了两路 LED。LED 高电平亮,低电平灭。详细电路可参考开发板原理图。

LED 位号 | 管脚名称 | 管脚位置 |

LED1 | IO_L7N_14 | W22 |

LED2 | IO_L9N_14 | Y22 |

3.14.按键

开发板设计了两路用户按键,一路复位按键。按键默认高电平,按下为低电平,按键连到 PL 侧,管脚位置如下表。

按键位号 | 管脚名称 | 管脚位置 |

KEY1 | IO_L7P_14 | W21 |

KEY2 | IO_L9P_14 | Y21 |

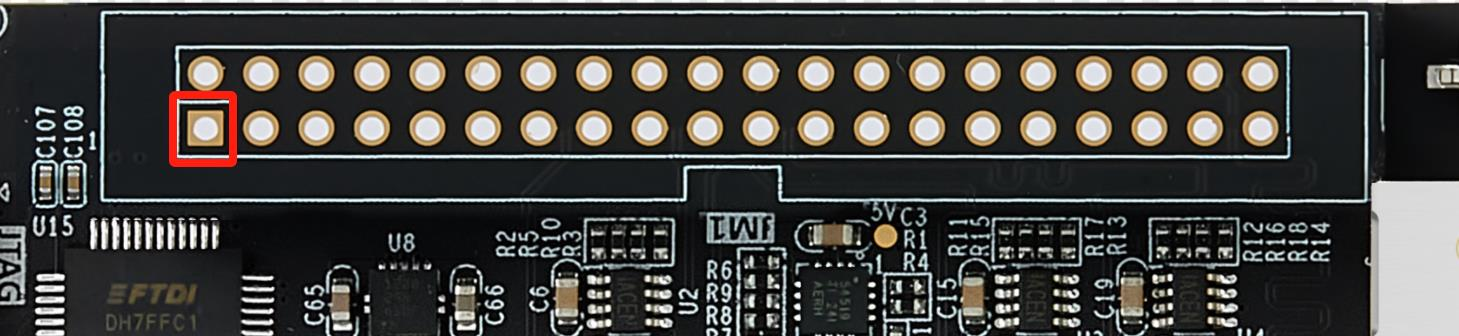

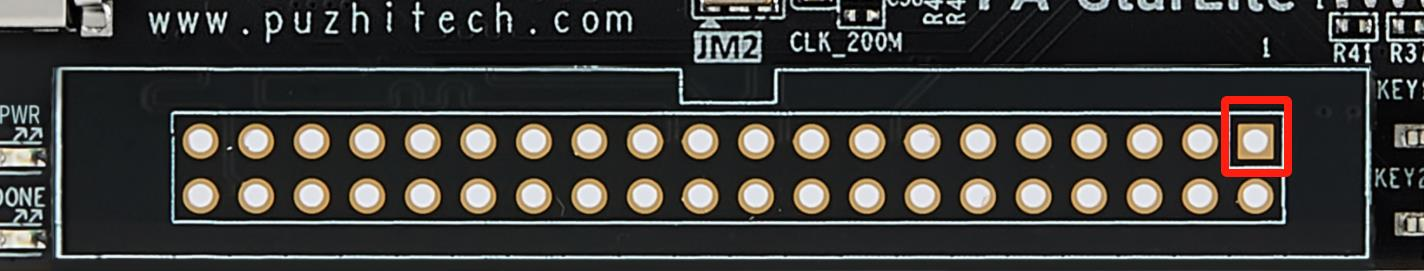

3.15.40P 扩展口

开发板设计了一个 40P 2.54mm 间距的简易牛角座,用于扩展信号的连接,信号与 FPGA 的 BANK15/16 连接,电平为 3.3V。如下表标出了信号所在的芯片位置,详细连接关系参考原理图部分,1脚位置已标注。

JM1 信号顺序 | 管脚名称 | 管脚位置 | JM1 信号顺序 | 管脚名称 | 管脚位置 |

5 | IO_L5P_16 | E16 | 6 | IO_L1P_16 | F13 |

7 | IO_L5N_16 | D16 | 8 | IO_L1N_16 | F14 |

9 | IO_L8P_16 | C13 | 10 | IO_L6P_16 | D14 |

11 | IO_L8N_16 | B13 | 12 | IO_L6N_16 | D15 |

13 | IO_L10P_16 | A13 | 14 | IO_L3P_16 | C14 |

15 | IO_L10N_16 | A14 | 16 | IO_L3N_16 | C15 |

17 | IO_L9P_16 | A15 | 18 | IO_L4P_16 | E13 |

19 | IO_L9N_16 | A16 | 20 | IO_L4N_16 | E14 |

21 | IO_L11P_SRCC_16 | B17 | 22 | IO_L7P_16 | B15 |

23 | IO_L11N_SRCC_16 | B18 | 24 | IO_L7N_16 | B16 |

25 | IO_L12P_MRCC_16 | D17 | 26 | IO_L2P_16 | F16 |

27 | IO_L12N_MRCC_16 | C17 | 28 | IO_L2N_16 | E17 |

29 | IO_L13P_MRCC_16 | C18 | 30 | IO_L15P_16 | F18 |

31 | IO_L13N_MRCC_16 | C19 | 32 | IO_L15N_16 | E18 |

37 | IO_L14P_SRCC_16 | E19 | 38 | IO_L16P_16 | B20 |

39 | IO_L14_SRCC_N_16 | D19 | 40 | IO_L16N_16 | A20 |

JM2 信号顺序 | 管脚名称 | 管脚位置 | JM2 信号顺序 | 管脚名称 | 管脚位置 |

5 | IO_L4P_15 | G17 | 6 | IO_L15P_15 | N22 |

7 | IO_L4N_15 | G18 | 8 | IO_L15N_15 | M22 |

9 | IO_L2P_15 | G15 | 10 | IO_L6P_15 | H17 |

11 | IO_L2N_15 | G16 | 12 | IO_L6N_15 | H18 |

13 | IO_L3P_15 | J14 | 14 | IO_L5P_15 | J15 |

15 | IO_L3N_15 | H14 | 16 | IO_L5N_15 | H15 |

17 | IO_L1P_15 | H13 | 18 | IO_L10P_15 | M21 |

19 | IO_L1N_15 | G13 | 20 | IO_L10N_15 | L21 |

21 | IO_L11P_SRCC_15 | J20 | 22 | IO_L8P_15 | H20 |

23 | IO_L11N_SRCC_15 | J21 | 24 | IO_L8N_15 | G20 |

25 | IO_L12P_MRCC_15 | J19 | 26 | IO_L9P_15 | K21 |

27 | IO_L12N_MRCC_15 | H19 | 28 | IO_L9N_15 | K22 |

29 | IO_L13P_MRCC_15 | K18 | 30 | IO_L7P_15 | J22 |

31 | IO_L13N_MRCC_15 | K19 | 32 | IO_L7N_15 | H22 |

37 | IO_L14P_SRCC_15 | L19 | 38 | IO_L16P_15 | M18 |

39 | IO_L14N_SRCC_15 | L20 | 40 | IO_L16N_15 | L18 |

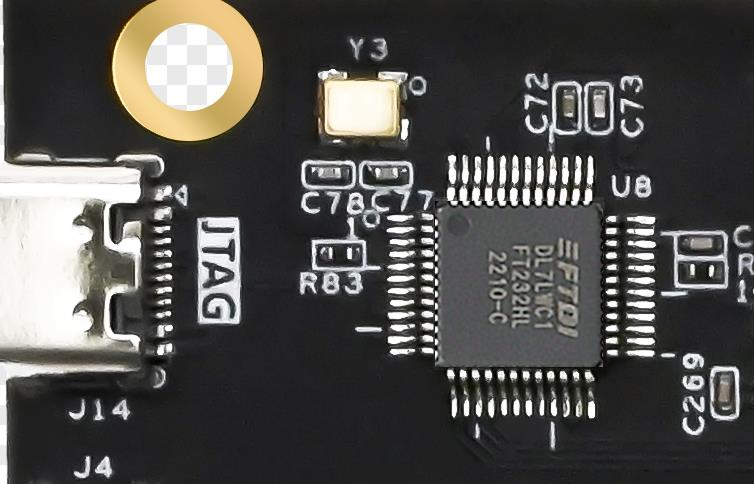

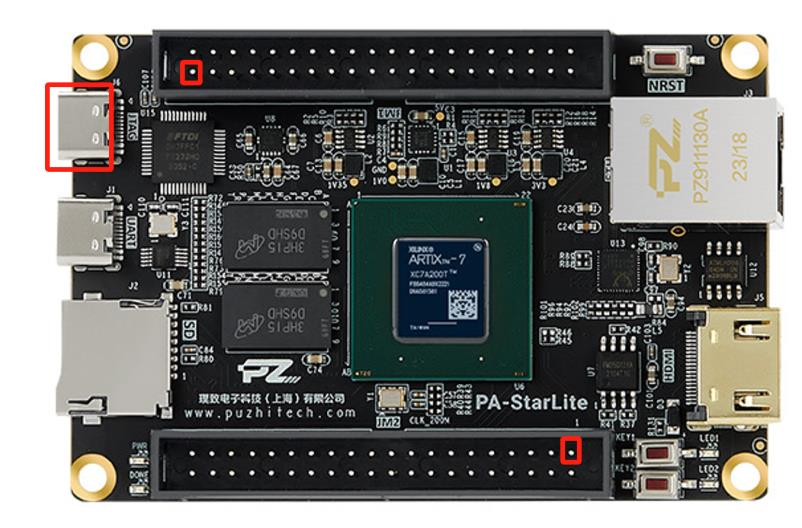

3.16.USB 转 JTAG 下载器

开发板板载了一个 USB 转 JTAG 下载器,安装好 Vivado 软件后使用USB 线连接好JTAG 对应的 USB 口,即可实现调试下载,非常方便。如下是接口在开发板上的位置图。