基于FPGA实现ARINC818

1.使用transceiver进行正确配置,如何配置不正确,设计会出现很多问题

2.关于transceiver的IP可以配置任意的line rate先速率,如果需要修改速率,直接使用IP进行配置,然后生成ex,然后将共享文件进行替换和覆盖

3.设计需要注意大小端

4.设计的接口可以设计为axi-s数据流接口,也可以设计为VGA的行场同步接口

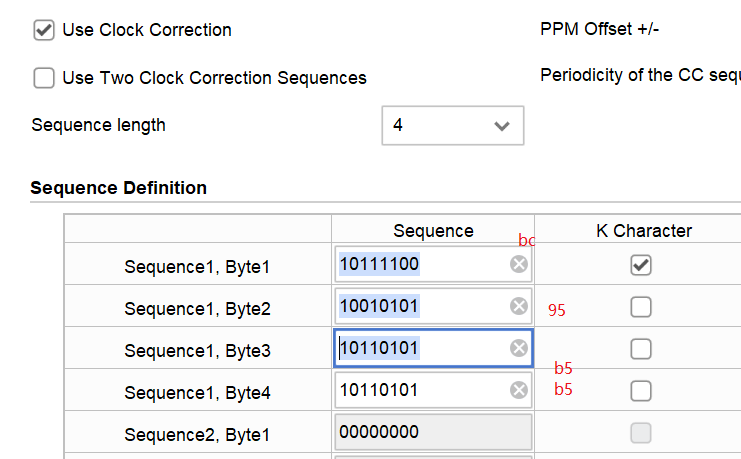

5.编码部分设计

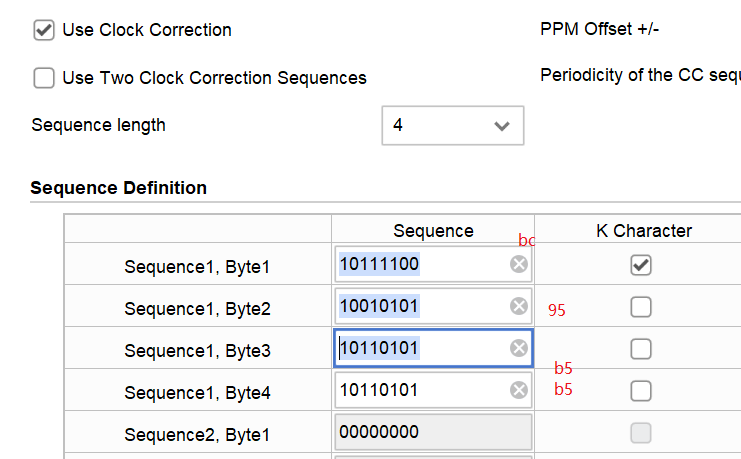

6.解码部分设

1.使用transceiver进行正确配置,如何配置不正确,设计会出现很多问题

2.关于transceiver的IP可以配置任意的line rate先速率,如果需要修改速率,直接使用IP进行配置,然后生成ex,然后将共享文件进行替换和覆盖

3.设计需要注意大小端

4.设计的接口可以设计为axi-s数据流接口,也可以设计为VGA的行场同步接口

5.编码部分设计

6.解码部分设