(T24) 跨时钟域SI->Q path的latch选型

在前端设计中, latch并不是主流的跨时钟域的同步方案(主流仍然是触发器+协议 或者 异步FIFO) ; 对于DFTmode下SI-Q的跨时钟路径, latch仍是解决hold问题的有效方式;

latch电平类型的选择核心是:它在“透明窗口”开放的时段,不能与目的域采样边沿形成数据直通或竞争;同时要让数据在需要时被稳定“关住”。

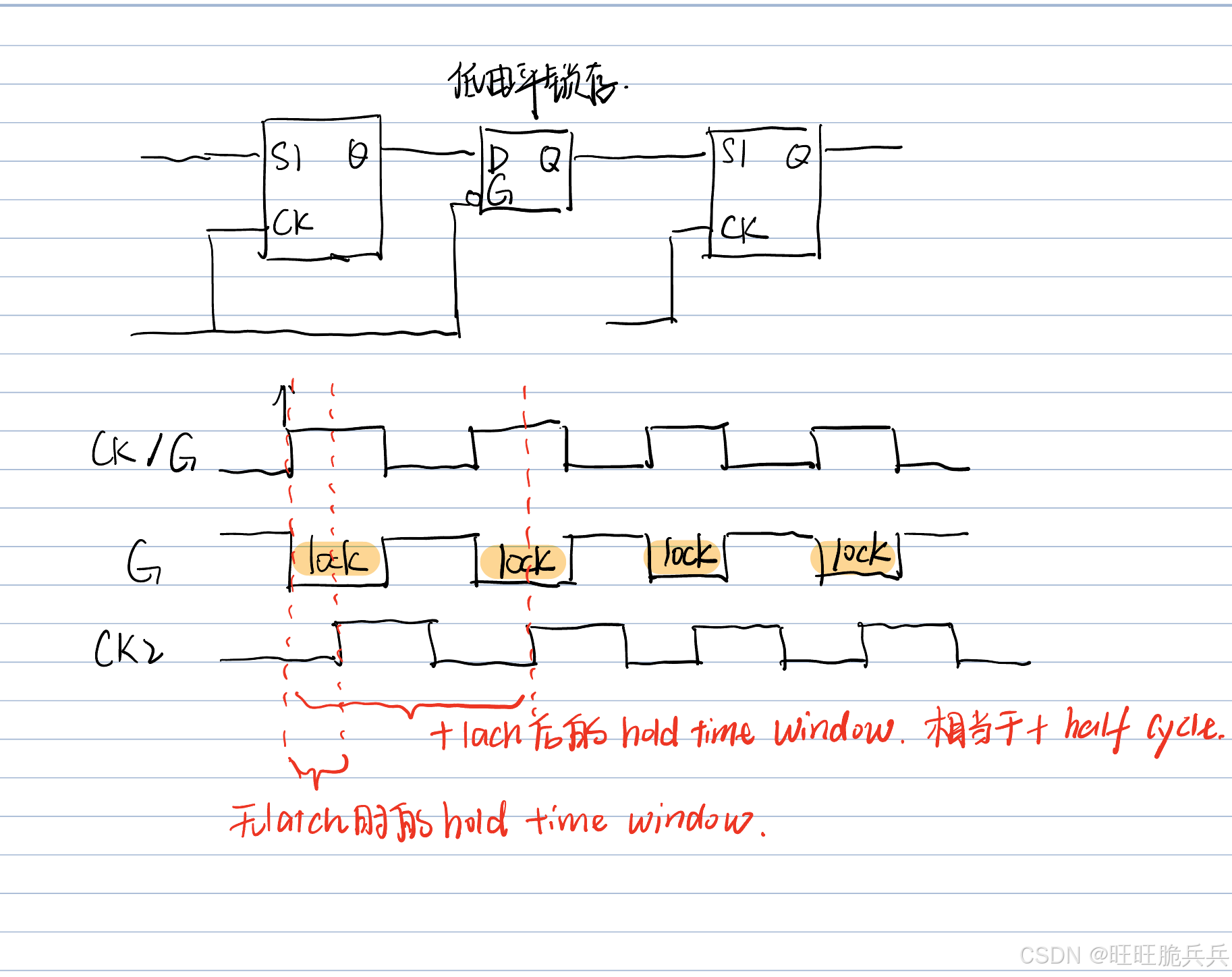

Case 1:

两个寄存器都是同沿触发, 但来自不同时钟域; latch 选择与沿相反的电平触发类型; 且latch要与做launch 寄存器做clock tree balance;

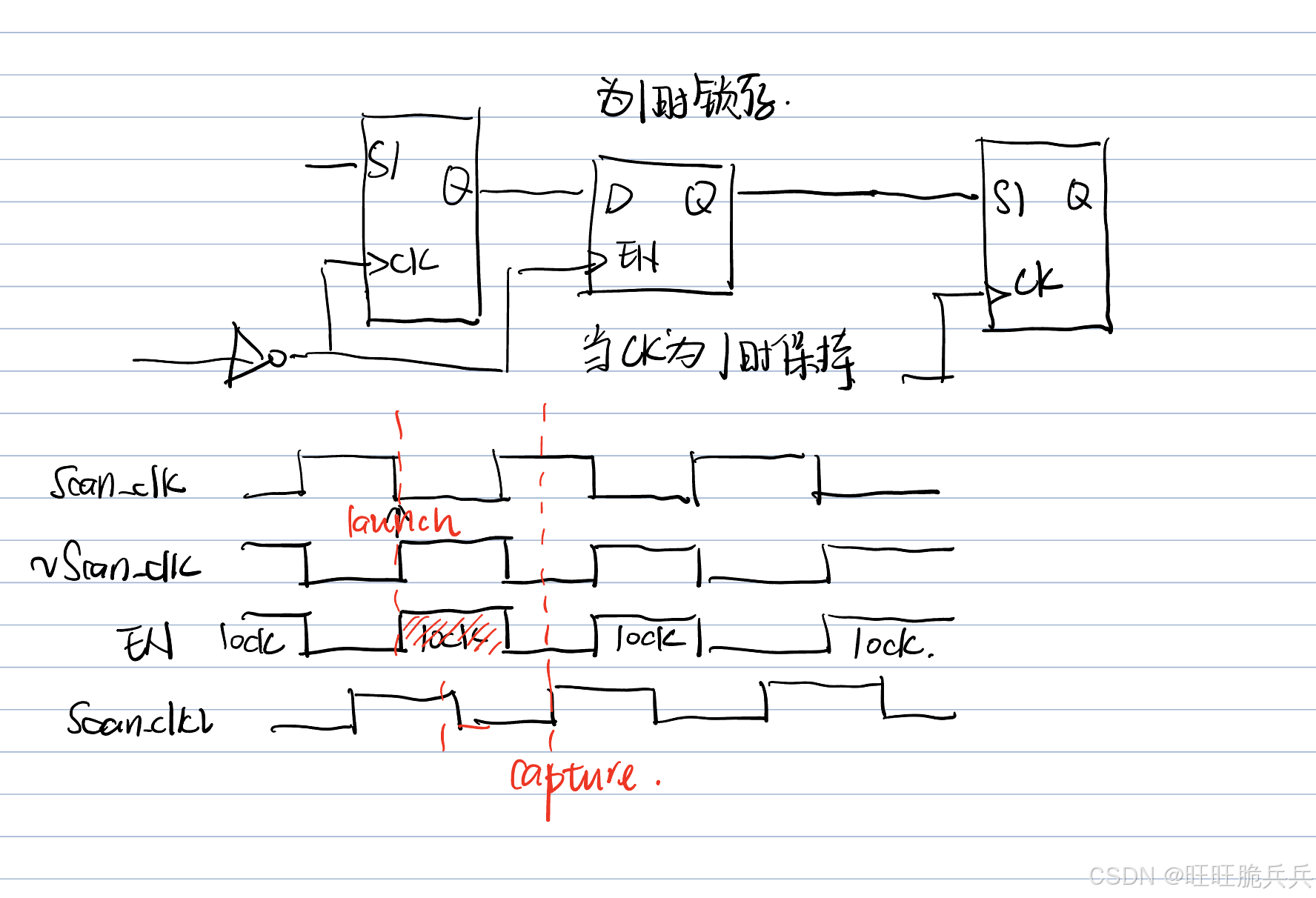

Case 2:

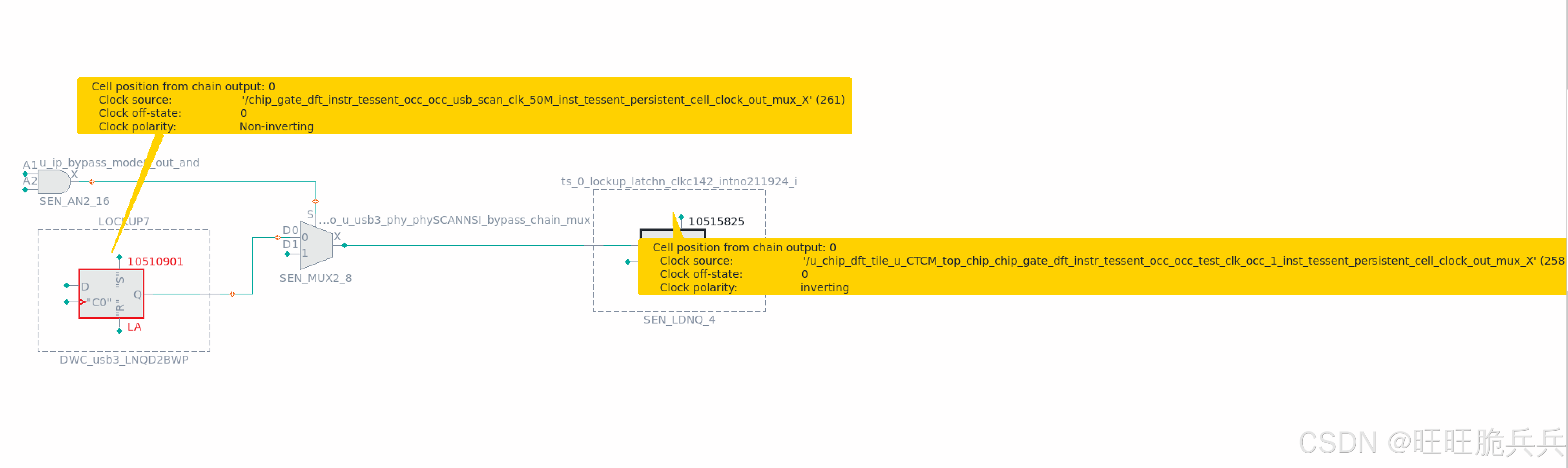

T24的违例报告在两个latch上; 提示两个latch的时钟来自不同的时钟域, 且极性相反;latch再往前一级寄存器为正沿触发: 但值得注意的是, 此级latch和上一级寄存器的时钟都来自于clock的反;

latch EN为高电平时保持; 与case1 正沿寄存器接低电平latch一致; 分析原因与tcd中描述的最后一级为latch的极性; 不是scan cell的极性; 导致在工具在串链时(只吃tcd) 插latch时极性判断错误;