嵌入式系统与RISC-V:开源架构驱动的下一代创新

目录

- 前言

- 1 嵌入式系统概述

- 1.1 定义与核心特征

- 1.2 典型应用场景

- 2 RISC-V架构概述

- 3 RISC-V ISA基础:简洁与模块化设计

- 3.1 精简指令集与寄存器模型

- 3.2 特权模式与内存管理

- 3.3 压缩指令集(C扩展)

- 4 ISA扩展机制:灵活可裁剪的创新设计

- 5 RISC-V在嵌入式系统中的技术优势

- 5.1 功耗与面积优化

- 5.2 实时性与多核支持

- 5.3 安全与隔离机制

- 5.4 开放生态与自主可控

- 6 工具链与开发生态

- 7 典型嵌入式应用实例

- 8 结语

- 参考资料

前言

随着人工智能、物联网(IoT)和边缘计算的高速发展,嵌入式系统的角色正在从“执行简单逻辑控制”向“智能化决策与实时数据处理”转变。在这一背景下,处理器架构的开放性与可定制性成为推动产业演进的关键。

RISC-V 作为一种开源、模块化的指令集架构(ISA),正在重新定义嵌入式领域的生态格局。它以简洁、灵活、高能效的设计理念,为开发者提供了更自由的创新空间,逐步成为嵌入式、边缘AI和高性能计算的核心技术基础。

本文将系统介绍嵌入式系统的技术特征,并深入剖析RISC-V的架构设计、扩展机制、嵌入式应用优势及其生态工具链,全面展现RISC-V如何助力构建下一代智能设备。

1 嵌入式系统概述

1.1 定义与核心特征

嵌入式系统(Embedded System)是指专门为特定功能而设计的计算机系统,其硬件与软件紧密结合,常被嵌入在设备或产品中,用于控制、监测或数据处理。

与通用计算机不同,嵌入式系统强调实时性、低功耗、高可靠性与长期稳定运行。其典型特征包括:

- 资源受限:CPU频率低、内存容量小,注重能效与占用面积。

- 实时性要求高:需在确定时间内响应外部事件。

- 高可靠性:系统需长期运行且容错能力强。

- 软硬件协同设计:硬件架构与软件逻辑高度匹配。

1.2 典型应用场景

嵌入式系统广泛应用于工业控制、汽车电子、消费电子、医疗设备与通信基础设施等领域。例如:

| 应用领域 | 典型设备 | 技术特征 |

|---|---|---|

| 工业自动化 | PLC控制器、智能传感器 | 高可靠性、实时响应 |

| 汽车电子 | ADAS、车身控制单元 | 安全隔离、并行计算 |

| 消费电子 | 智能手表、语音助手 | 超低功耗、集成AI |

| 医疗设备 | 可穿戴监测仪、植入式控制芯片 | 高安全性、长续航 |

| 通信设备 | 无线网关、边缘节点 | 多核并发、协议处理 |

在这些场景中,嵌入式系统需要具备可扩展架构与灵活的软硬件适配能力,这正是RISC-V在设计之初所关注的核心方向。

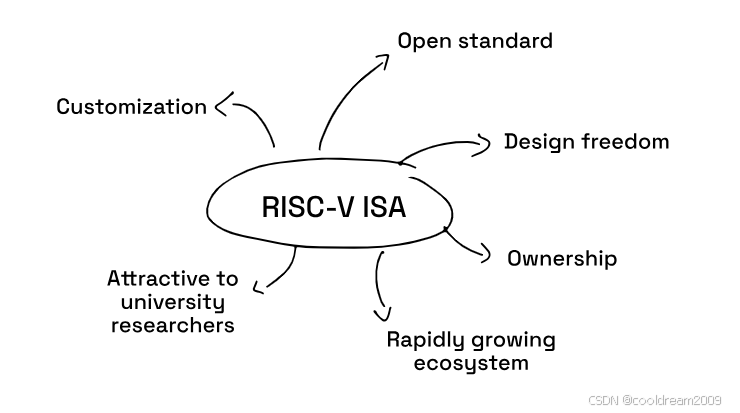

2 RISC-V架构概述

RISC-V(读作“risk-five”)诞生于2010年,由加州大学伯克利分校发起,旨在打造一个开放、精简、模块化的指令集架构,以突破ARM、x86等专有架构的限制。

2015年,非营利组织 RISC-V International 成立,统一维护架构标准。目前已有超过400家成员公司参与,包括 SiFive、Andes、Intel、NVIDIA、Alibaba、Google 等。

RISC-V的核心理念是:

- 开源与自由实现:无需授权费用,允许任何组织自行设计处理器。

- 模块化与可裁剪性:开发者可根据场景选择或定制扩展集。

- 可验证与高兼容性:所有标准扩展均保持向后兼容,降低生态碎片化风险。

到2025年,RISC-V已成为MCU、AI加速器、汽车控制器和高性能嵌入式SoC的重要架构选择。

3 RISC-V ISA基础:简洁与模块化设计

3.1 精简指令集与寄存器模型

RISC-V基于精简指令集计算(RISC) 原则,采用“负载-存储(Load-Store)架构”,所有计算均通过寄存器完成,简化硬件控制路径。

基本指令集 RV32I 包含约47条指令,涵盖整数运算、分支跳转与存储访问操作。

寄存器模型包括:

- 32个通用寄存器(x0–x31):x0固定为常数0,用于快速清零。

- PC程序计数器:控制指令执行顺序。

- CSR寄存器组:用于管理状态、中断与特权控制。

在嵌入式系统中,这种简化设计可减少硅片面积与功耗,提高实时响应性能。

3.2 特权模式与内存管理

RISC-V支持三级特权模式:

- M-mode(机器模式):最高权限,执行启动与安全控制。

- S-mode(监督模式):运行RTOS或轻量操作系统。

- U-mode(用户模式):普通应用运行空间。

通过 控制与状态寄存器(CSR) 管理模式切换与中断处理,确保系统安全与隔离性。

同时,RISC-V支持:

- 物理内存保护(PMP):硬件级访问控制;

- 弱一致性内存模型:提升性能;

- 虚拟内存扩展(Sv32/Sv39):支持4GB及以上地址空间。

3.3 压缩指令集(C扩展)

嵌入式设备常面临Flash容量限制。

RISC-V的C扩展允许将部分32位指令压缩为16位形式,从而提升代码密度20~30%,在MCU与低功耗SoC上显著降低存储与功耗成本。

4 ISA扩展机制:灵活可裁剪的创新设计

RISC-V的扩展系统是其最大的技术亮点。开发者可通过标准化扩展或自定义指令集实现针对性优化,而不破坏兼容性。

下表展示了部分常见扩展及其在嵌入式系统中的典型应用:

| 扩展代号 | 功能说明 | 典型嵌入式应用 |

|---|---|---|

| M | 乘除法扩展(MUL/DIV) | 数字滤波、信号处理算法 |

| A | 原子操作(AMO, LR/SC) | 多核同步与任务调度 |

| F/D | 浮点扩展 | 传感器融合、航姿计算 |

| V | 向量扩展(SIMD) | TinyML模型加速、图像识别 |

| C | 压缩指令集 | IoT固件、低功耗设备 |

| B/P | 位操作与打包SIMD扩展 | 通信协议解析与DSP计算 |

| 自定义扩展 | 用户自定义指令 | 加密算法、AI算子加速 |

例如,Andes Custom Extension™ (ACE) 允许开发者为5G基站或AI芯片添加加密与信号处理指令,从而在特定任务上实现2~5倍性能提升。

此外,向量扩展(V) 已成为边缘AI的关键基础,可根据寄存器长度(VLEN=128~1024位)动态调整并行度。

5 RISC-V在嵌入式系统中的技术优势

5.1 功耗与面积优化

RISC-V允许开发者根据需求裁剪指令集。

例如,RV32E变体仅保留16个寄存器,面积比ARM Cortex-M0小约30%,功耗可降至微瓦级,非常适合可穿戴设备和传感器网络。

这种模块化策略使得RISC-V可在性能与功耗之间灵活平衡。

5.2 实时性与多核支持

RISC-V支持多核与异构集群架构。

借助 原子操作扩展(A) 与 内存一致性协议(AMO),多个核心可高效协作,共享内存资源。

在RTOS(如Zephyr、FreeRTOS)支持下,RISC-V可实现确定性中断响应,满足汽车电子与工业控制对实时性的严格要求。

5.3 安全与隔离机制

RISC-V通过 物理内存保护(PMP) 与特权模式隔离实现硬件级安全防护,防止非法访问与代码注入。

此外,RISC-V生态正推动 安全扩展标准化(Security SoC Profile),确保医疗、汽车与工业应用的可信执行。

5.4 开放生态与自主可控

与ARM不同,RISC-V无授权限制,开发者可自由复用开源IP(如Rocket、PicoRV32、BOOM),大幅降低设计成本与周期。

据统计,基于RISC-V的SoC开发周期较传统架构缩短20%~50%,有助于快速原型验证与量产落地。

6 工具链与开发生态

RISC-V的生态体系正在快速成熟,覆盖编译、调试、仿真与系统构建等多个层面:

| 工具类别 | 主流组件 | 功能特性 |

|---|---|---|

| 编译器 | GCC、LLVM、riscv-gnu-toolchain | 支持RV32/64,优化级别-O3,兼容EABI |

| 调试与仿真 | QEMU、OpenOCD、GDB、JTAG | 支持裸机与RTOS调试 |

| IDE与框架 | PlatformIO、Eclipse CDT、VS Code | 集成构建、烧录与跟踪 |

| 高级语言支持 | Rust(embedded-hal)、Swift Embedded | 安全类型系统、硬件抽象层 |

| 构建与自动化 | CMake + Rocket Chip生成器 | 自动化RTL生成与固件打包 |

| 商用开发板 | SiFive HiFive1、Andes AE350 | 支持RV32IMAC及Zephyr RTOS |

此外,部分厂商(如RISCstar)在2025年推出了预编译全ISA支持工具链,简化嵌入式交叉编译和调试部署过程。

7 典型嵌入式应用实例

| 应用场景 | RISC-V核心 | 技术特性与成果 |

|---|---|---|

| 工业控制器 | RV32IMC | 微秒级中断延迟,支持实时PID算法 |

| 智能穿戴设备 | RV32E + C扩展 | 超低功耗运行,支持TinyML语音识别 |

| 车载视觉系统 | RV64G + V扩展 | 图像预处理加速,性能较ARM A55提升约2倍 |

| 边缘AI节点 | 自定义矩阵乘法指令集 | 提升ML推理效率3~5倍 |

| 医疗监测设备 | RV32EC | 具备安全隔离与加密功能,支持长期运行 |

这些案例表明,RISC-V不仅适用于低功耗MCU,也能覆盖高性能、实时与安全敏感的嵌入式场景。

8 结语

RISC-V正在以开源精神和模块化理念重塑嵌入式系统的生态格局。

从微控制器到系统级芯片,从IoT节点到AI边缘加速器,RISC-V凭借灵活性、低功耗与可扩展性,为开发者提供了全栈创新平台。

未来十年,随着AI、车联网与智能制造的持续融合,RISC-V将不仅是一种ISA标准,更是一种推动产业开放、加速技术自主创新的生态理念。

它让嵌入式开发不再受限于专有授权,而成为一场真正属于全球开发者的技术革命。

参考资料

- RISC-V International 官方规范文档:https://riscv.org/technical/specifications