基于 JETSON+FPGA+GMSL+AI 车载视频采集与存储系统设计(二)系统测试

5.1 系统测试实验平台搭建 根据课题项目的要求,本系统要求能获取高分辨率的高清图像,并采用 GMSL 接 口输出。因此本系统选用索尼公司生产的 IMX490-GMSL 摄像头作为原始视频采集的 图像传感器,图像传感器模型如图 5.1 所示。IMX490 是 CMOS 图像传感器,支持输 出最大分辨率可以达到 2896×1876,约 540 万有效像素。使用千兆多媒体串行链路串 行器和解串器技术,支持使用 GMSL 接口时序输出图像数据。而且该 GMSL 相机还 能够对采集的视频图像进行补偿,支持伽玛曲线、白平衡、饱和度、色度等基础处理。 可以根据不同的分辨率配置寄存器参数,GMSL 相机输出的视频图像的帧率可以在 30-60 帧范围内可调。相机工作在正常状态时的实际功率在 150mW-200mW 范围内波 动是正常的。

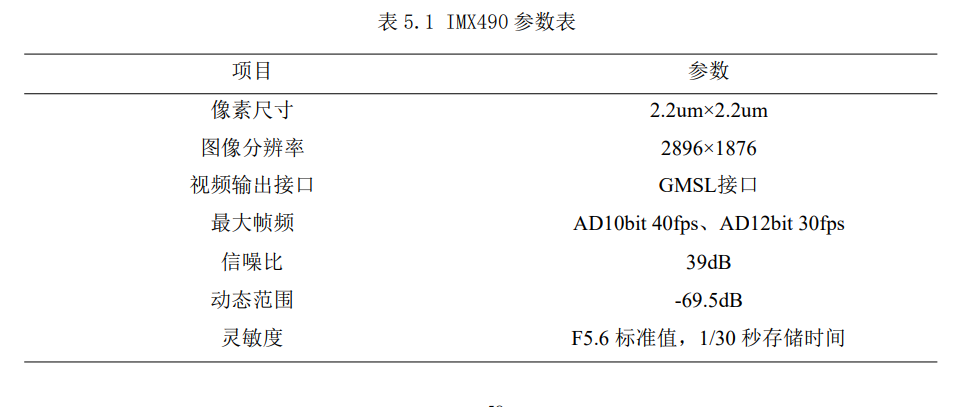

IMX490 图像传感器通过改变图像采集窗口的比例输出不同的分辨率图像。在视 频采集时通过 IIC 总线向 IMX490 发送内部寄存器配置信息完成相机初始化,图像输 出从而实现对分视频辨率、视频输出格式、视频图像色度和图像画面对比度等工作状 态的参数设置。IMX490 相机的具体参数如下表 5.1 所示。

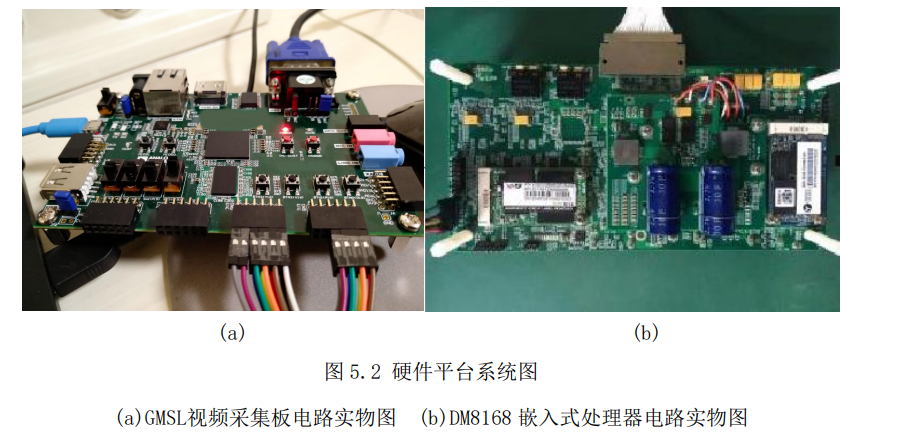

选好相机的型号后,根据第三章设计的系统设计方案搭建实验平台,搭建好的实 验电路如图 5.2 所示,左边电路图(a)是 GMSL 视频采集与接口转换电路单元,该 单元负责对 GMSL 接口输出的视频图像进行时标叠加和接口时序变换;右边电路图(b) 是对视频进行采集与存储的 DM8168 嵌入式处理单元,该单元主要负责对 GMSL 视 频数据进行原视频存储与压缩编码,并将压缩编码的视频数据通过网络传输。然后通 过实验平台模拟对车载视频的采集与存储验证并记录实验的效果和实验的相关数据。

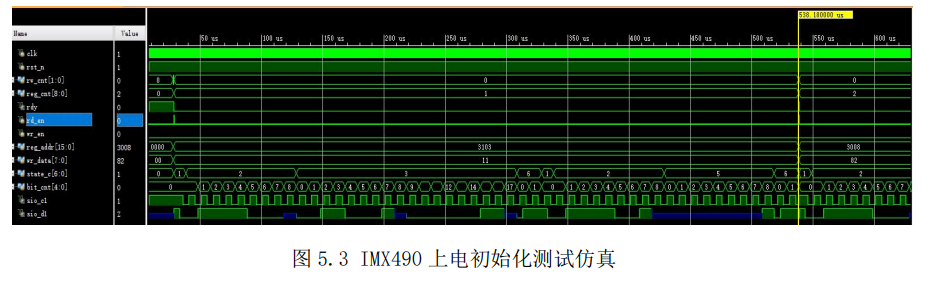

5.2 GMSL 视频采集与转换单元测试分析 连接好 GMSL 相机与视频采集板后对系统上电,在 FPGA 端通过 ISE14.7 自带的 仿真器对 IMX490 摄像头上电初始化的 IIC 总线数据传输进行波形仿真得出图 5.3 上 电时序仿真波形,通过仿真出来的时序图可以看出传输一个字节需要 9 个时钟周期, 写时序和读时序和软件程序设计一致。在 ISE14.7 中对 IMX490 摄像头采集模块顶层 模块程序进行编译,还可以得到 RTL 电路图。

5.4 本章小结 本章完成了对系统视频数据采集、视频数据存储和视频数据压缩编码速率进行了 测试分析。首先对视频数据的采集进行了测试分析,通过液晶屏显示和 Modesim 仿真 测试可以观察到视频数据采集和传输正常。通过视频画面可以观察到视频时标叠加正 常。最后通过对视频数据的回放测试,视频 SATA 盘存储正常。然后对视频的压缩编 码进行测试,视频的压缩编码率在误差范围内,满足系统的要求。根据上述的测试结 果,表明本系统的功能和性能指标均达到课题项目要求,设计的基于 GMSL 的车在视 频采集与存储系统稳定可靠。