AXI总线的基础知识

目录

一、核心设计哲学与特点

二、AXI的通道架构(Channel Architecture)

三、关键概念详解

1. Burst 传输

2. 事务ID

四、AXI协议家族

五、一个简单的写传输时序例子

总结

AXI(Advanced eXtensible Interface)是一种高性能、高频率的片上总线协议,是ARM公司推出的AMBA(Advanced Microcontroller Bus Architecture)标准的一部分。它被广泛用于连接处理器、内存控制器和高性能外设等片上系统(SoC)中的IP核。

一、核心设计哲学与特点

AXI的设计围绕几个核心思想展开,这些也是它区别于前代总线(如AHB)的关键:

-

分离的地址/数据通道:读命令、写命令、读数据、写数据、写响应都有独立的通道。这允许这些操作并行发生,极大地提高了总线利用效率。

-

例如:处理器可以在前一个写操作的数据还在传输时,就发出下一个读操作的地址。

-

-

基于VALID/READY的握手机制:这是AXI的流控制机制。每个通道都使用

VALID和READY信号来握手。-

源端 驱动

VALID表示地址、数据或控制信息已经准备好。 -

目的端 驱动

READY表示它已经准备好接收信息。 -

传输发生在

VALID和READY同时为高的时钟上升沿。这种机制使得连接双方可以以各自最快的速度运行,无需等待对方,实现了简单的反压控制。

-

-

支持乱序传输:每个传输都有一个ID标签。不同ID的交易可以以任何顺序完成。这对于提升系统性能至关重要,比如一个慢速外设的访问不会阻塞后续对高速内存的访问。

-

支持非对齐传输:简化了处理器(尤其是支持非对齐内存访问的架构,如ARM)与总线的接口设计。

-

** burst 传输**:只需提供首地址,即可传输一大块连续数据,高效利用带宽。

二、AXI的通道架构(Channel Architecture)

这是理解AXI工作原理的核心。AXI协议定义了5个独立的通道:

1. 写地址通道 (AW)

-

主设备 → 从设备

-

传输信息:本次写传输的首地址、burst类型、burst长度等。

2. 写数据通道 (W)

-

主设备 → 从设备

-

传输信息:实际的数据 和字节使能信号。

-

注意:数据通道的宽度可以配置(如32位,64位,128位等)。

3. 写响应通道 (B)

-

从设备 → 主设备

-

在一次burst写传输全部完成后,从设备通过此通道返回一个响应信号(如

OKAY,EXOKAY,SLVERR,DECERR),告诉主设备这次写入是成功还是失败。

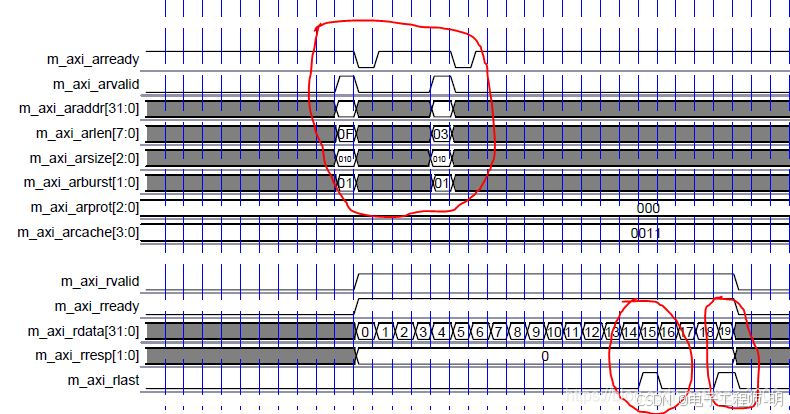

4. 读地址通道 (AR)

-

主设备 → 从设备

-

传输信息:本次读传输的首地址、burst类型、burst长度等。

5. 读数据通道 (R)

-

从设备 → 主设备

-

传输信息:从设备返回的数据,并在最后一次传输时携带响应信号。

三、关键概念详解

1. Burst 传输

AXI的所有数据传输都是基于burst的。一次burst传输由1到256个数据节拍(beat)组成。主设备只需在地址通道发出首地址和burst信息,后续数据的地址由从设备根据协议自动计算。

-

Burst Length: 传输的数据量(

ARLEN/AWLEN)。 -

Burst Size: 每次传输的数据宽度(

ARSIZE/AWSIZE),如 1字节,4字节等。 -

Burst Type: 主要定义了地址计算方式(

ARBURST/AWBURST)。-

FIXED: 地址不变,用于访问FIFO或外设寄存器。

-

INCR: 递增burst,地址按size大小递增,用于访问常规内存。

-

WRAP: 回环burst,地址递增,但到达边界后回绕到起始地址,用于缓存行填充。

-

2. 事务ID

每个通道的信号中都包含一个ID标签(ARID, AWID, RID, BID)。这允许主设备发出多个未完成的事务(Outstanding Transactions),并且从设备可以以任何顺序(Out-of-order)返回这些事务的数据或响应。系统通过ID来匹配返回的数据与最初发出的请求。

四、AXI协议家族

在AMBA 4(2010年)中,AXI演进为一个协议家族,包含三个主要变体:

| 协议 | 全称 | 主要特点与适用场景 |

|---|---|---|

| AXI4 | AXI4 (Full) | 高性能内存映射接口。支持最多256 beat的burst,功能最全,用于连接处理器、DDR控制器、DMA等高带宽需求的主从设备。 |

| AXI4-Lite | AXI4-Lite | 简化版,轻量级。不支持burst(每次传输1个数据),所有其他高级功能(乱序、非对齐等)均不支持。用于配置寄存器等简单的低速外设,实现简单。 |

| AXI4-Stream | AXI4-Stream | 用于高速数据流。没有地址概念,只有一个主设备和一个从设备,数据一直流。用于连接ADC/DAC、视频处理管线、网络接口等。 |

五、一个简单的写传输时序例子

-

主设备在写地址通道上驱动地址和控制信息,并拉高

AWVALID。 -

从设备准备好接收地址后,拉高

AWREADY。 -

在CLK上升沿,

AWVALID和AWREADY同时为高,地址被捕获。 -

主设备在写数据通道上驱动数据,并拉高

WVALID。如果是最后一次数据传输,同时拉高WLAST。 -

从设备准备好接收数据后,拉高

WREADY。 -

在CLK上升沿,

WVALID和WREADY同时为高,数据被捕获。重复步骤4-6直到所有数据传输完毕。 -

从设备在写响应通道上驱动响应信号(如

BRESP),并拉高BVALID。 -

主设备准备好接收响应后,拉高

BREADY。 -

在CLK上升沿,

BVALID和BREADY同时为高,写响应被主设备捕获,整个写事务结束。

总结

AXI总线通过其通道分离和握手机制,实现了高性能、高灵活性的片上通信。它的架构完美契合了现代多核、高并行度SoC的设计需求,成为了该领域无可争议的事实标准。理解其五通道模型和VALID/READY握手是掌握AXI的关键。