存储栈学习笔记

1. 缩略词

- NvM:Non-Volatile RAM Manager(非易失存储管理器),AutoSar SW层提供存储管理服务的核心模块。

- MemIf:Memory Abstraction Interface(内存抽象模块接口),提供外部非易失存储的管理、读取、存储接口,是将存储设备硬件抽象后的标准模块。

- EEP:Electrically Erasable Programmable Read-Only Memory(电可擦可编程只读存储器),MCAL层EEPROM驱动的简称。

- FEE:Flash Emulation EEPROM(Flash模拟EEPROM),AutoSar基于Flash实现类EEPROM功能的模块。

- Fls:Flash Driver(Flash驱动),MCAL层的Flash软件驱动模块。

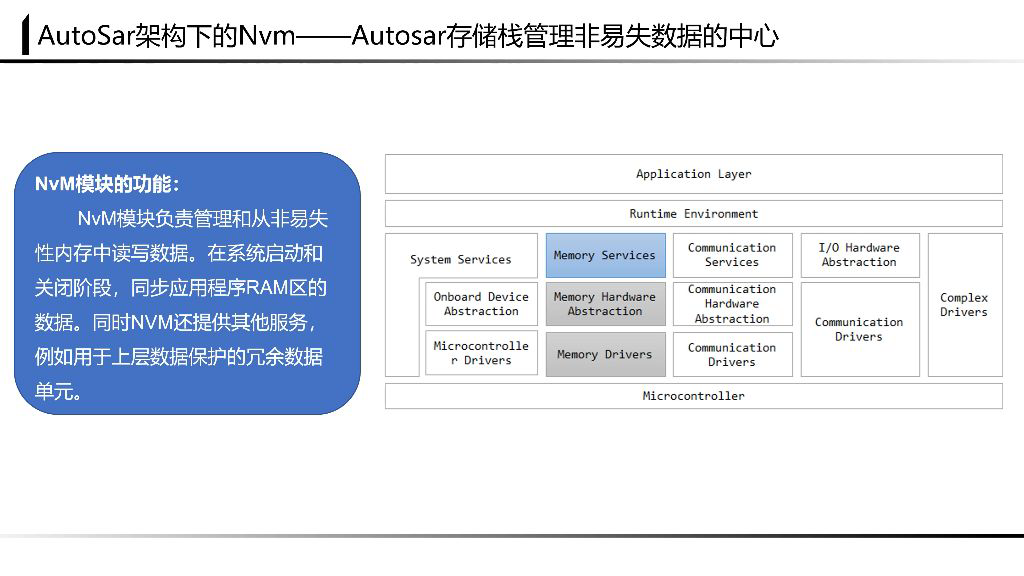

2. AutoSar架构下的Nvm

(1)Autosar存储栈管理非易失数据的中心

- 核心地位:NvM模块是AutoSar非易失数据管理的核心,配合硬件抽象层FEE模块和驱动层(EEP/Flash等)共同构成存储栈。

- 分层结构:存储栈分为三层——存储服务层(BSW层,NvM模块)、存储硬件抽象层(MemIf、FEE/EA模块)、存储驱动层(MCAL层,EEP/Fls模块)。

(2)NvM模块的功能

- 核心功能:管理非易失性内存的数据读写,在系统启动/关闭阶段同步应用程序RAM区与非易失存储的数据。

- 增值服务:提供数据冗余保护单元等附加功能,保障数据安全性与可靠性。

(3)AutoSar存储栈的层次结构

- 服务层:NvM模块,提供存储管理服务接口(如数据读写、同步),面向应用层提供统一调用方式。

- 抽象层:MemIf、FEE/EA模块,实现存储硬件抽象,屏蔽不同存储介质(Flash/EEPROM)的硬件差异。

- 驱动层:EEP、Fls模块,直接操作存储硬件设备,执行底层读写、擦除等硬件指令。

(4)存储栈设计的问题

- 介质特性矛盾:

- RAM:空间小、随机读写速度快(纳秒级)、掉电丢失,适合运行时临时数据存储。

- ROM(Flash/EEPROM):容量大、读写速度慢(毫秒级)、擦除次数有限(几万-几十万次),适合持久化数据存储。

- 设计需求:需结合两者优势,实现“既能持久保存数据,又能支持运行时修改”的存储机制。

(5)自动存储管理

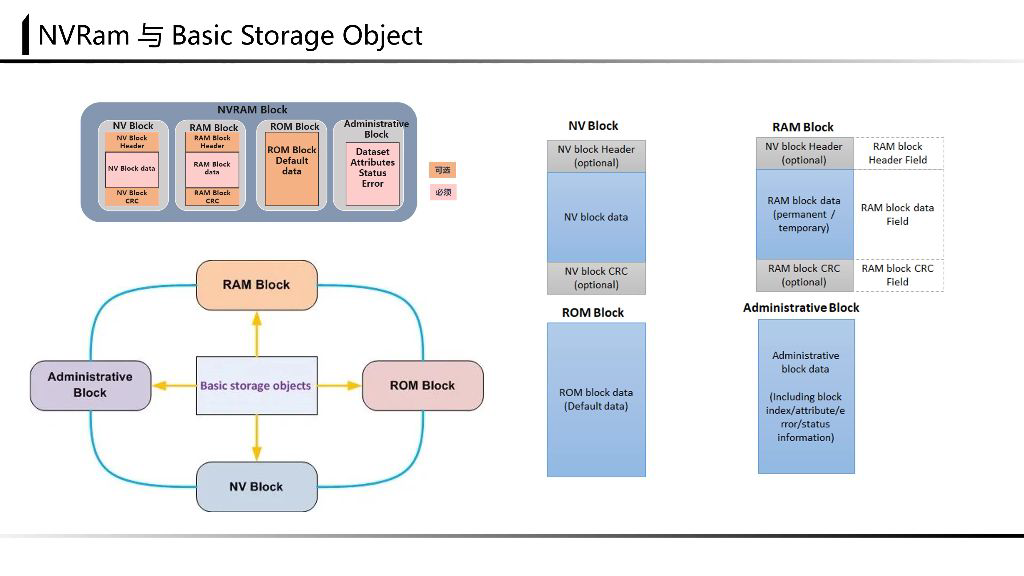

① NvRam与基本存储对象

| 存储对象 | 存储位置 | 功能作用 | 可见性 |

|---|---|---|---|

| NV Block | Flash | 存储持久化数据,读写速度较慢 | 用户可见 |

| RAM Block | RAM | 作为应用层数据交互的缓存,访问速度快,用于临时存储待同步/读取的数据 | 用户可见 |

| ROM Block | Flash | 存储默认数据(可选配置),用于NV Block失效时恢复默认值 | 用户可选见 |

| Administrative Block | RAM | 存储管理数据(如Block序号、属性、错误状态),负责存储栈内部管理 | 用户不可见 |

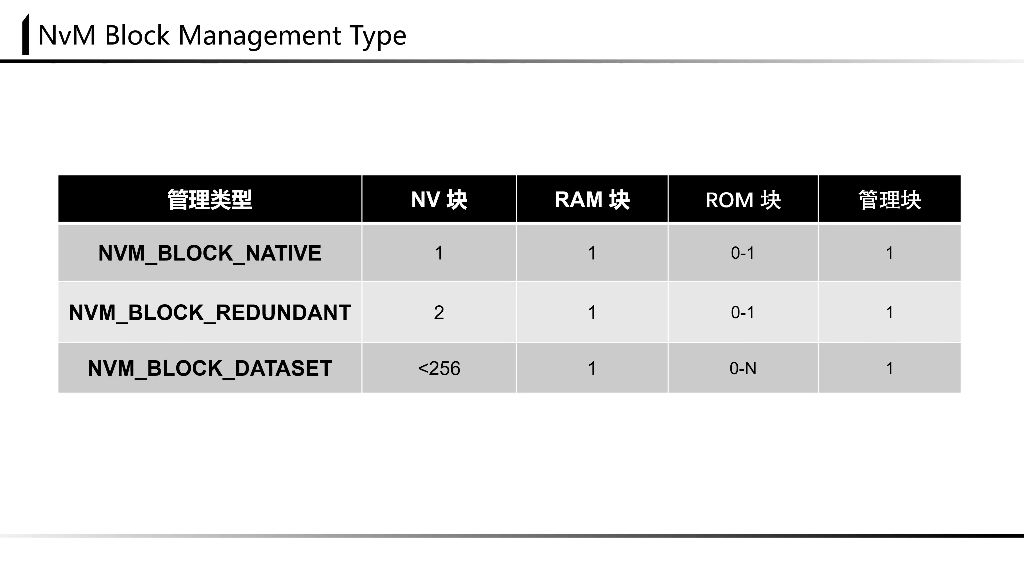

② NvM Block管理类型

- NATIVE类型:1个NV Block + 1个RAM Block + 1个管理块(必选),可配置0-1个ROM Block,适用于普通单备份数据存储。

- REDUNDANT类型:2个NV Block(双备份) + 1个RAM Block + 1个管理块,提供更高安全性,适用于关键数据(如诊断DTC、安全配置)。

- DATASET类型:1-255个NV Block + 1个RAM Block + 1个管理块,可配置N个ROM Block,用于管理一组关联数据(如同一功能的多个参数)。

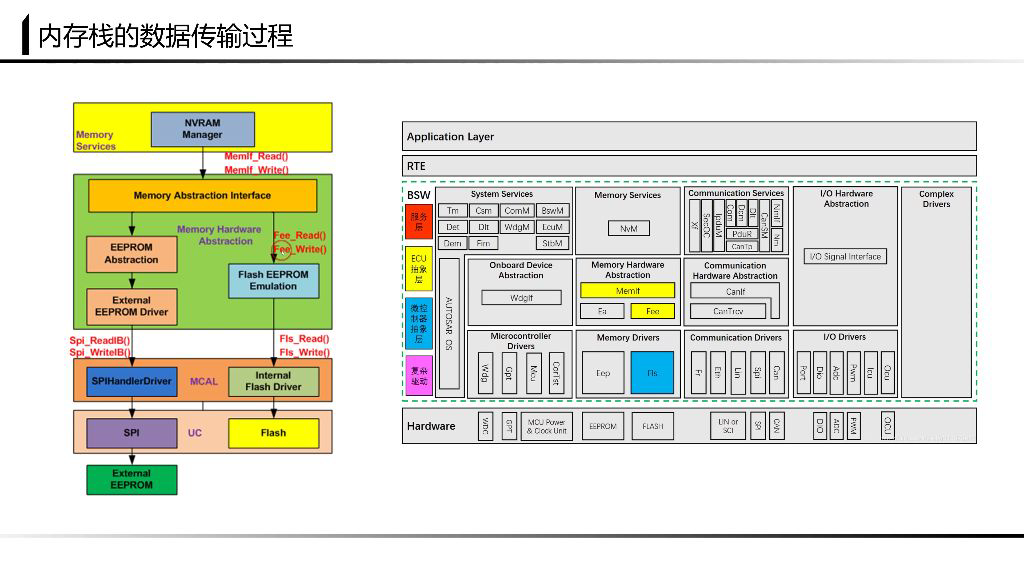

(6)内存栈的数据传输过程

- 交互基础:所有数据存取均基于“NVRAM Block”为单位执行。

- 执行流程:应用层发起数据操作请求 → 调用NvM模块接口 → NvM调用MemIf抽象层接口 → MemIf转发请求至FEE/EA模块 → FEE/EA模块调用EEP/Fls驱动 → 驱动操作硬件完成数据读写。

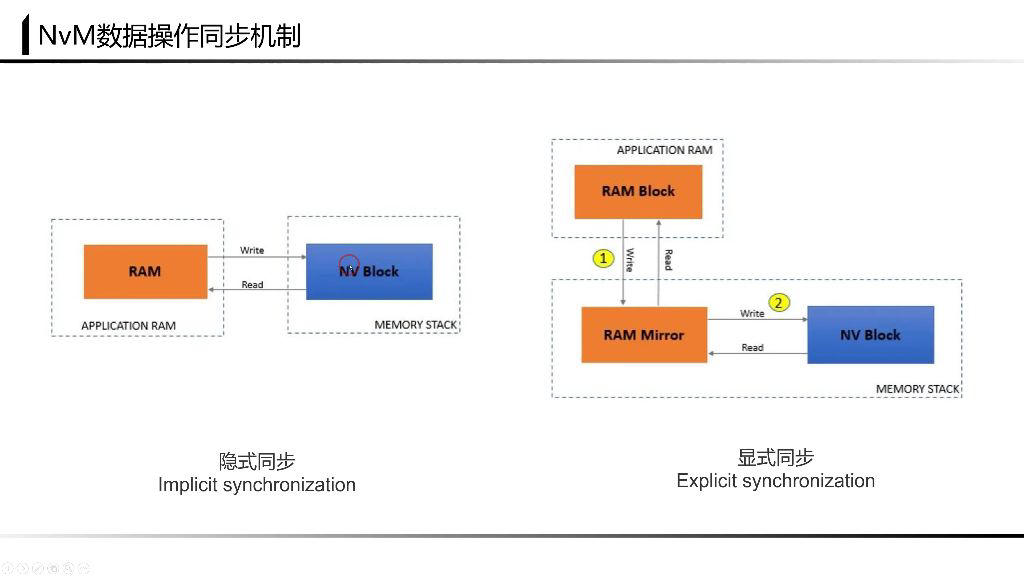

(7)NvM数据操作同步机制

- 隐式同步:NV Block直接与应用层RAM数据交互(无中间缓存),操作延迟低,适合实时性要求高的场景。

- 显式同步:通过“RAM Mirror”(RAM镜像区)作为中间缓冲,数据先同步到镜像区再写入非易失存储,提供更安全的数据保护(如避免断电导致的数据损坏)。

3. FEE模块与FEE的机制

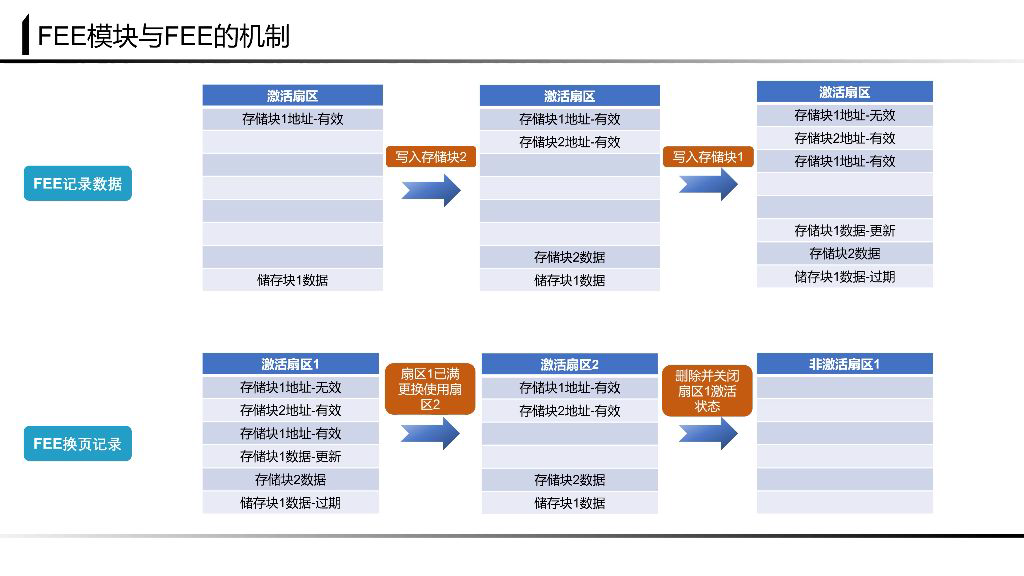

(1)FEE记录数据

- 实现原理:采用“地址+数据”组合记录方式,新数据写入Flash的新物理地址,并标记旧地址数据为“无效”,避免重复擦除同一区域。

- 硬件限制适配:Flash仅支持“存储位为FF(未写入)时覆盖写入”,需先擦除(将存储位置为FF)才能重新写入,FEE通过地址轮换规避此限制。

(2)FEE换页记录

- 扇区管理机制:采用“双扇区轮换”策略,Flash划分为“激活扇区”(当前写入扇区)和“备用扇区”(待切换扇区)。

- 优势:实现近似无限次的数据修改,规避Flash擦写次数有限的硬件限制。

- 操作流程:

- 激活扇区(如扇区1)数据写满;

- 将扇区1中的有效数据拷贝到备用扇区(如扇区2);

- 擦除扇区1(恢复为FF状态);

- 切换备用扇区为新的激活扇区,原激活扇区变为备用扇区。

4. 实际操作配置

(1)配置流程

① 打开ISO lab工具与工作重点

- 工作范围:本章仅配置BSW模块,不涉及system info文件夹。

- 核心任务:BSW模块(NvM、MemIf、FEE)配置;ASW/BSW模块与NvM的连接配置。

- 操作起点:单击vcu starter工程,打开RTA代码生成对话框。

② 选择rtabsw与存储介质模块选择

- 模块选择依据:根据实际使用的非易失存储介质类型决定:

- 若使用Flash介质:需选择NvM、MemIf、Fee、rbaFefSYS模块;

- 若使用EEPROM介质:需选择EaMemIf、NvM、rbaFefSYS模块。

- 代码生成基础:基于已创建的模块ARXML文件生成底层代码。

③ 创建memory stack模块

- 操作步骤:

- 返回主界面,通过ECU navigator进入BSW模块配置界面;

- 在BSW模块下创建NvM、Fee、MemIf模块;

- 将所有存储相关模块放在同一个ARXML文件中(命名为“Memory Stack”)。

- 注意事项:创建时需遵循命名规范(如去除模块名称中多余的“0”,确保标识清晰)。

④ 配置流程回顾与NV m模块作用

- 核心机制:NvM模块接收应用层数据存取需求,通过MemIf抽象层接口调用具体存储介质(Flash/EEPROM)的操作模块,最终由驱动层完成硬件交互。

- 数据流向:应用层 → NvM模块 → MemIf模块 → FEE/EA模块 → EEP/Fls驱动 → 存储硬件。

(2)NVRAM模块配置

① common配置选项

- 关键参数:

- NvMApiConfigClass:仅支持“Class Three”(AutoSar标准规定);

- NvMCompiledConfigId:初始设为0(关联动态配置,后续可根据需求调整);

- CrcNumberOfBytes:设为1字节(在满足校验需求的前提下节省存储资源);

- DevErrorDetect:建议开启(便于开发阶段检测配置错误或运行时异常);

- PollingMode:设为True(采用同步处理方式,操作完成后立即返回结果,本例适用)。

- 优化建议:

- NvMJobPrioritization:设为True(启用作业优先级,高优先级操作可打断低优先级操作);

- MainFunction周期:设为0.001秒(1毫秒,确保存储作业及时调度);

- StandardJobQueue:初始设为5(作业队列长度,可根据调试过程中的实际作业数量调整)。

② block descriptor配置

- 核心配置项:

- BlockManagementType:选择管理类型(native/redundant/dataset,根据数据重要性决定);

- BlockLength:定义NvM Block的数据长度(示例设为8字节,需与应用层数据长度匹配);

- NumberOfBlocks:native类型设为1(1个NV Block对应1个RAM Block)。

- 重要机制:

- SelectBlockForReadAll:设为True(系统上电时自动将NV Block数据加载到RAM Block);

- SelectBlockForWriteAll:设为True(系统下电时自动将RAM Block数据写入NV Block)。

- 调试建议:

- 初始阶段可按需求大胆配置,通过代码生成工具校验配置合法性,发现错误后针对性修改;

- 利用trace工具和生成的底层代码,分析配置参数对实际存储操作的影响;

- 错误调试是理解AUTOSAR存储栈功能逻辑的重要环节,需重点关注DevErrorDetect上报的异常。

- 特殊参数:

- RamBlockCrc:建议开启(对RAM Block数据进行CRC校验,防止数据在RAM中被篡改);

- ResistantToChangedSW:建议关闭(非必要场景下,减少配置复杂度);

- MaxNumOfRead/WriteRetries:设为3-5次(读取/写入失败时的重试次数,需注意不同存储介质的重试次数限制)。

- 回调函数:

- 初始化回调(NvM_InitCallback):可设为NULL(本例无特殊初始化需求);

- 验证回调(NvM_VerifyCallback):根据需求配置(如自定义数据验证逻辑)。

(3)MEMIF模块配置

- 配置选项:仅包含“General”一个配置文件夹,无其他子项。

- 关键参数:

- Main function cycle time:声明主函数周期(与NvM模块主函数周期保持一致,设为1毫秒);

- Number of device:设为1(管理1个存储设备,本例仅用Flash);

- RB Fee使用声明:设为True(使用FEE模块管理Flash,若用EEPROM则选择EA模块);

- Verapi设置:设为False(关闭版本接口,简化配置);

- Developed error:设为True(开启开发阶段错误检测)。

(4)FEE模块配置

① FEE General配置

- 关键配置项:

- Error detect:开启“develop an error detect”(开发阶段错误检测);

- FEE index:初始设为0(标识FEE模块实例,多存储设备时需区分);

- 通知回调:配置“NV M job的end notification”(存储作业完成时的回调函数,可选)、“Error notification”(存储错误时的回调函数,便于异常处理);

- 工作模式:设为“polling mode”(同步工作模式,与NvM模块匹配);

- 功能开关:根据需求开启“Erase suspension”(擦除暂停)、“Safety check”(安全检查)、“Survival evaluation”(存续性评估);

- Machine type:若找不到匹配的MCU型号,可选择“menu config”(手动配置Flash参数);

- 冗余块维护:开启“maintain redundant block”(双备份块维护,提升数据安全性);

- Buffer size:设为1024字节(FEE内部数据缓冲大小,需根据Flash页大小调整);

- 虚页大小:必须与实际Flash页大小一致(示例设为16字节,需参考MCU数据手册)。

- 地址管理机制:

- FEE模块将Flash物理地址“虚拟化”,应用层通过NvM操作的是“虚拟地址”;

- FEE内部自动完成“虚拟地址→物理地址”的映射,屏蔽Flash硬件地址细节。

② FEE SectorTable配置

- 核心配置:右键添加“child sector table”(扇区表子项),配置Flash扇区参数。

- 物理页大小:必须与Flash控制器支持的页大小、Flash芯片实际页大小一致(示例设为16字节,需参考Flash数据手册)。

③ FEE Sectors配置

- Sector数量要求:必须配置≥2个sector(满足FEE双扇区轮换机制的需求);

- 物理大小声明:需准确填写每个sector的实际物理大小(单位:字节,参考MCU/Flash数据手册);

- 配置方式:可一次性添加多个sector,并分别配置大小(如2个sector,每个大小为4096字节);

- 自动生成机制:FEE block无需手动配置,工具会根据NvM模块的Block配置自动生成对应的FEE block;

- Flash模块关联:FEE与Flash的交互配置在MCAL阶段完成,通过AutoSar标准接口(如Fls_Erase、Fls_Write)实现数据交互。

二、内容总结

1. AutoSar架构下的非易失数据管理机制

- 核心问题:解决“非易失存储介质(Flash/EEPROM)读写速度慢”与“应用层RAM数据访问速度快”之间的性能冲突,实现“持久存储+快速交互”的平衡。

- 实现模块:以NvM模块为核心,配合MemIf抽象层、FEE/EA硬件适配层、EEP/Fls驱动层,构成完整存储栈。

- 管理方式:基于“NV Block、RAM Block、ROM Block、Administrative Block”四类存储对象的不同组合,形成native(单备份)、redundant(双备份)、dataset(数据组)三种管理方式,适配不同场景需求。

(1)机制特点

- 多样性:三种管理方式各具优势,native适合普通数据、redundant适合关键数据、dataset适合关联数据组,覆盖多场景需求。

- 复杂性:为平衡“速度、安全性、硬件限制”,设计了分层抽象、地址轮换、同步机制等复杂逻辑,需结合AutoSar标准深入理解。

- 针对性:专门针对“存储介质与应用层速度不匹配”“Flash擦写次数有限”等硬件特性问题设计,确保非易失数据管理的实用性与可靠性。

三、知识小结

| 知识点 | 核心内容 | 考试重点/易混淆点 | 难度系数 |

|---|---|---|---|

| AUTOSAR存储架构 | 三层架构:存储服务层(NvM)、硬件抽象层(FEE/EA)、驱动层(Flash/EEP) | NvM(服务层)与FEE(硬件适配层)的功能边界区分 | ⭐⭐⭐⭐ |

| NvM模块 | 非易失数据管理中心,管理四类存储对象(NV/RAM/ROM/Admin Block),支持三种管理类型(native/redundant/dataset) | 三种管理类型的组成差异(NV Block数量、ROM Block可选性) | ⭐⭐⭐⭐ |

| 存储对象类型 | NV Block(Flash持久存储)、RAM Block(RAM缓存)、ROM Block(默认值存储)、Admin Block(管理数据) | ROM Block的“可选性”(仅在NV Block失效时启用) | ⭐⭐⭐ |

| 同步机制 | 隐式同步(直接RAM交互,实时性高) vs 显式同步(RAM镜像缓冲,安全性高) | 不同同步机制的“性能-安全性”权衡选择 | ⭐⭐⭐⭐ |

| FEE模块原理 | Flash模拟EEPROM的换页机制:双扇区轮换+无效标记,虚拟地址映射物理地址 | 虚拟地址与物理地址的映射逻辑,双扇区轮换流程 | ⭐⭐⭐⭐⭐ |

| 配置关键参数 | NvM Block长度、CRC校验方式、作业优先级、读写重试次数 | 动态配置ID(NvMCompiledConfigId)与版本兼容性 | ⭐⭐⭐⭐ |

| 存储介质特性对比 | Flash:块擦除、寿命短(万次级) vs EEPROM:字节擦除、成本高、寿命长(十万次级) | 擦除次数限制与硬件成本的权衡选择 | ⭐⭐⭐ |

| 错误处理机制 | 开发错误检测(DevErrorDetect)、CRC校验、写入验证、最大重试次数 | 不同错误场景的恢复策略(如重试、默认值恢复) | ⭐⭐⭐⭐ |

| 工具链配置流程 | NvM→MemIf→FEE三层模块创建,ARXML文件关联,设备ID与虚拟页大小配置 | 虚拟页大小与Flash实际页大小的一致性校验 | ⭐⭐⭐⭐ |