基于FPGA的HDB3编解码(verilog语言)

文章目录

- 前言

- 一、HDB3码介绍

-

- AMI码介绍

- 二、HDB3编码过程

-

- 1.V破坏码插入

- 2.B码插入

- 3.确认B极性

- 4.确认V极性

- 5.小总结

- 三、verilog编码设计

-

- 1.原始数据产生模块

- 2.V码插入

- 3.B码插入

- 4.极性确认

- 5.编码总

- 6.解码总

- 7.top顶层

- 总结

前言

项目背景就是将数据通信需要进行HDB3编码,进而一起学习一下。

一、HDB3码介绍

HDB3码(三阶高密度双极性码 High Density Bipolar of Order 3 code)是一种适用于基带传输的编码方式,它是为了克服AMI码(交替反转码 Alternative Mark Inversion)的缺点而出现的,具有能量分散,抗破坏性强等特点。在数字通信中,有些场合可不经过载波调制和解调过程,而对基带信号进行直接传输。采用AMI码的信号交替反转,有可能出现四连零现象,会使得编码的自时钟(self-clocking)信息丢失,这不利于接收端的定时信号提取。而HDB3码因其无直流成份、低频成份少和连0个数最多不超过三个等特点,而对定时信号的恢复十分有利。但HDB3码也有缺点:1、如果单bit编解码出错,会影响后续所有信息;2、对于编解码电路而言,工作前若未正确的清零,同样将出现错误的编解码信息。

AMI码介绍

HDB3是在AMI的基础上进行改良的,进而使得传输长串的0更加可靠。介绍HDB3码前,我们必须介绍一下AMI编码的方法:对于输入代码中所有的0保持不变,对所有的1加上极性符号+/-,注意这里不是随机加上+/-,一个序列中要保持正负交替,至于代码中第一个1是加上正极还是负极则没有明确规定,这里我们默认第一个1为+1,下面给出一个AMI编码的实例:

原始数据:10000110000101100001

AMI数据: 10000-110000-101-100001

二、HDB3编码过程

1.V破坏码插入

HDB3码基于AMI码,若输入代码中连续0的个数小于4则编码规则同AMI码一致,若出现连续的四个0,则通过一下规则编码:

1、0000变为000V:注意这里是每四个0进行转变(V码意为violation,表明编码时出现了连续四个0)

原始数据:1 1 0 0 0 0 1 0 0 0 0 0 0 0 0

加V数据: 1 1 0 0 0 V 1 0 0 0 V 0 0 0 V

2.B码插入

加入B码:检查相邻两个V码之间1的个数,若有偶数个1则后一个000V变为B00V,奇数个1则不变(B码意为bipolar)

加V数据: 1 1 0 0 0 V 1 0 0 0 V 0 0 0 V

加B数据: 1 1 B 0 0 V 1 0 0 0 V B 0 0 V

3.确认B极性

确定B的极性,B和1正负交替加上极性,默认第一个B或者1为+;AMI码本身1的极性切换还是不变的,B的极性要跟AMI的正负1极性在一起切换

加B数据: 1 1 B 0 0 V 1 0 0 0 V B 0 0 V

一次极性:1 -1 B 0 0 V -1 0 0 0 V B 0 0 V

4.确认V极性

确认V码的极性,V码也是正负交替加上极性,这里大家可以发现,V是一个破坏沿,其前一个非0码跟其有相同的极性(V码直接跟随其前面一个1或者B的极性),V码后一个非0码则是有相反极性。

一次极性:1 -1 B 0 0 V -1 0 0 0 V B 0 0 V

二次极性:1 -1 B 0 0 V -1 0 0 0 -V B 0 0 V

5.小总结

所以说连续的4个0会因为两个V之前1个个数还有前一个数据的极性来进行确定:

分别有4种情况:

两个连续V之间的1个数————无极性数据————前一个bit的极性————带极性数据————

————偶数—————————(B00V)——————正————————( -B 0 0 -V)

————偶数—————————(B00V)——————负————————(+B 0 0 +V)

————奇数—————————(000V)——————正————————( 0 0 0 +V)

————奇数—————————(000V)——————负————————( 0 0 0 -V)

三、verilog编码设计

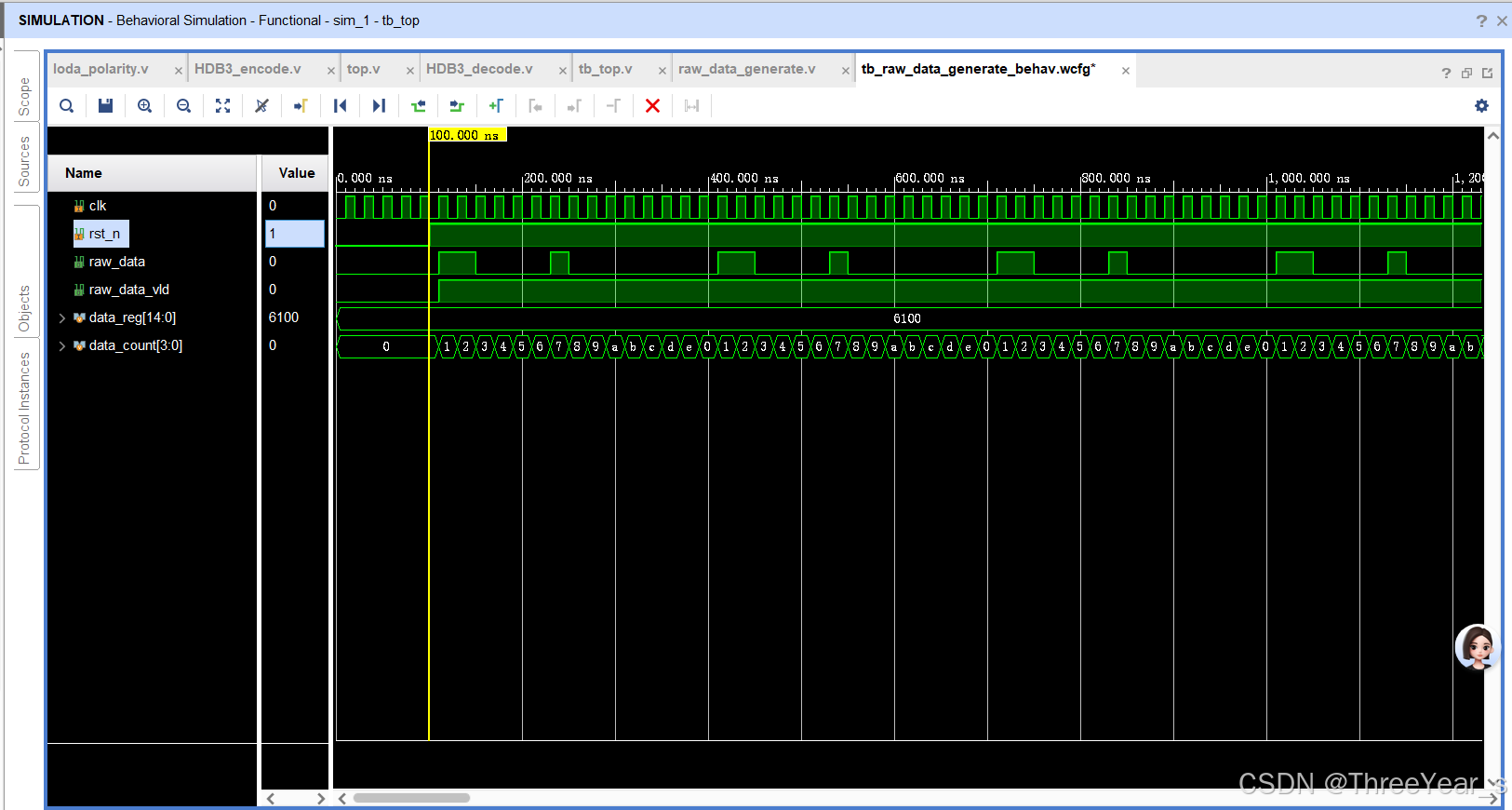

1.原始数据产生模块

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2025/09/24 21:07:39

// Design Name:

// Module Name: raw_data_generate

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////module raw_data_generate(input clk,input rst_n,output reg raw_data,output reg raw_data_vld);//data[14:0]:11 0000 1 0000 0000reg [14:0] data_reg;

reg [3:0] data_count;always @(posedge clk or negedge rst_n)beginif(!rst_n)begindata_reg <= 15'h61_00;data_count <= 4'd0;raw_data <= 1'b0;raw_data_vld <= 1'b0;endelse if(data_count<4'd14)beginraw_data <= data_reg[14-data_count];data_count <= data_count + 4'd1;data_reg <= data_reg;raw_data_vld <= 1'b1;endelse beginraw_data <= data_reg[14-data_count];data_count <= 4'd0;data_reg <= data_reg;raw_data_vld <= 1'b1;end

endendmodule

2.V码插入

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2025/09/24 21:34:22

// Design Name:

// Module Name: load_V

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////module load_V(input clk,input rst_n,input raw_data,input raw_data_vld,output reg [1:0] raw_data_V,output reg raw_data_V_vld,output reg [3:0] zero_count,output reg [3:0] one_count);//reg [3:0] zero_count; //统计0的个数

//reg [3:0] one_count; //统计1的个数

always @(posedge clk or negedge rst_n)beginif(!rst_n)beginzero_count <= 4'd0;one_count <= 4'd0;endelse if(raw_data_vld)beginif(!raw_data && zero_count<4'd3)begin zero_count <= zero_count + 4'd1;one_count <= 4'd0;endelse if(!raw_data && zero_count==4'd3)begin