ARM架构——学习时钟7.2

补充:消抖:

- 针对按键操作中的信号抖动问题,有硬件与软件两种消抖方法。

- 硬件消抖可通过添加电容或使用施密特触发器实现,后者利用正反馈形成迟滞比较器,设定上下门限电压以过滤毛刺。

- 施密特触发器通过电阻网络构建双阈值电压(如3.3V与1.6V),确保输入信号在跨越门限时产生稳定跳变,有效抑制高频噪声干扰。

- 软件消抖通常结合定时器,在检测到中断后延迟一段时间再读取状态,避开机械抖动期,常用延时时间为20ms左右。

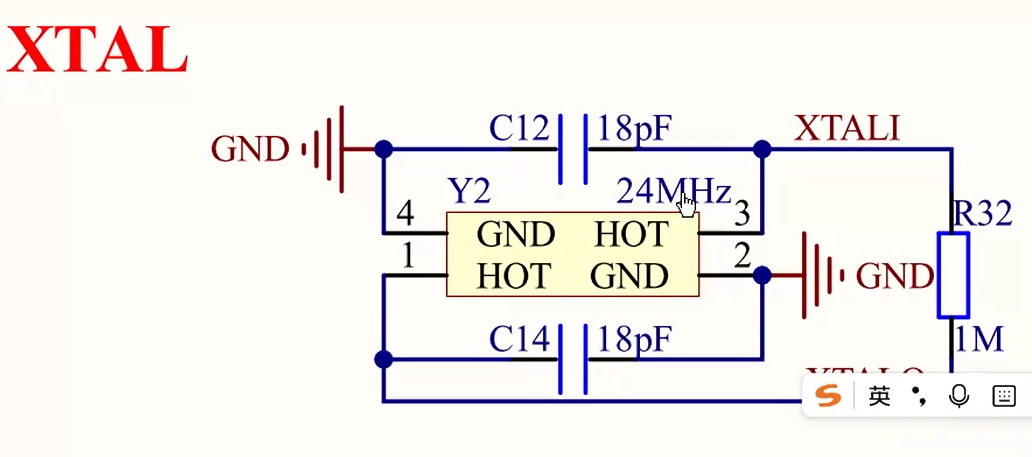

一、12M晶振

执行一条指令所花费时间:t = 1 /f (时间周期)

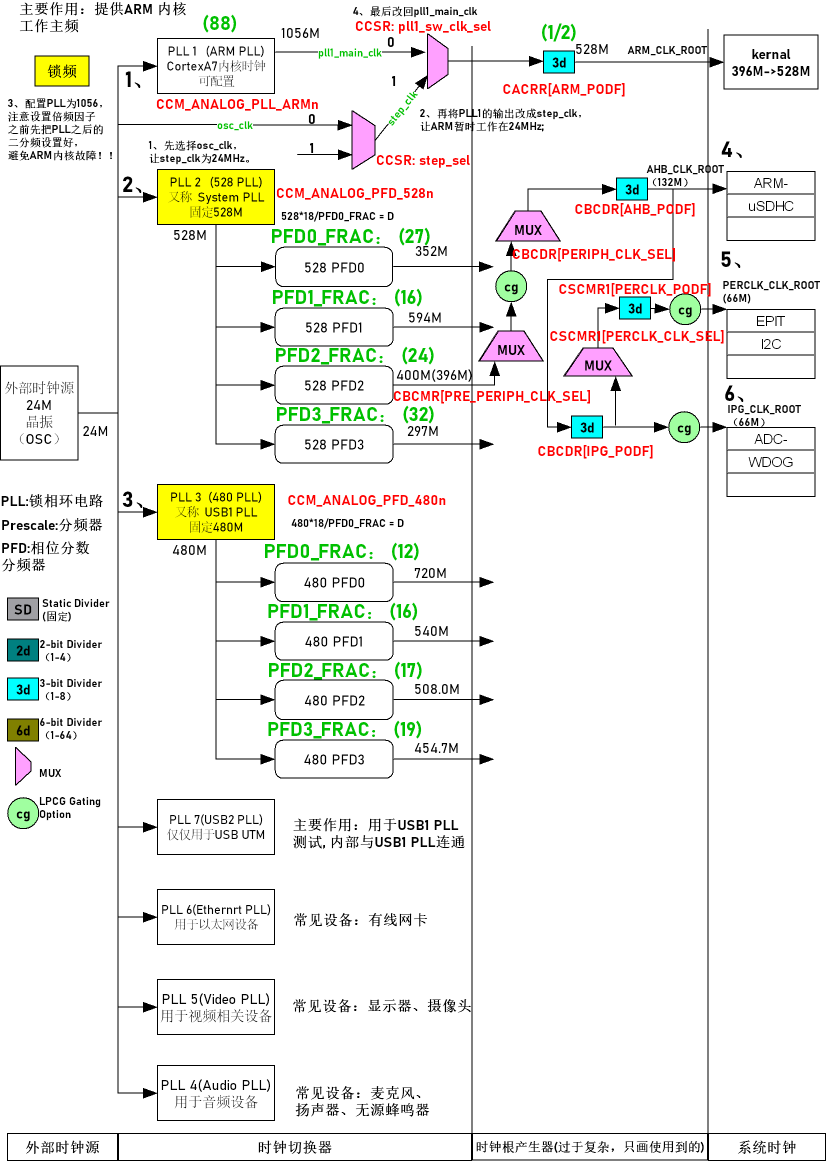

iMXULL 一上电,外部一个24M的晶振(石英差 稳定的时钟源), 产生396MHZ的时钟,通过时钟树的操作,产生不同频率的时钟供给不同的外设使用。

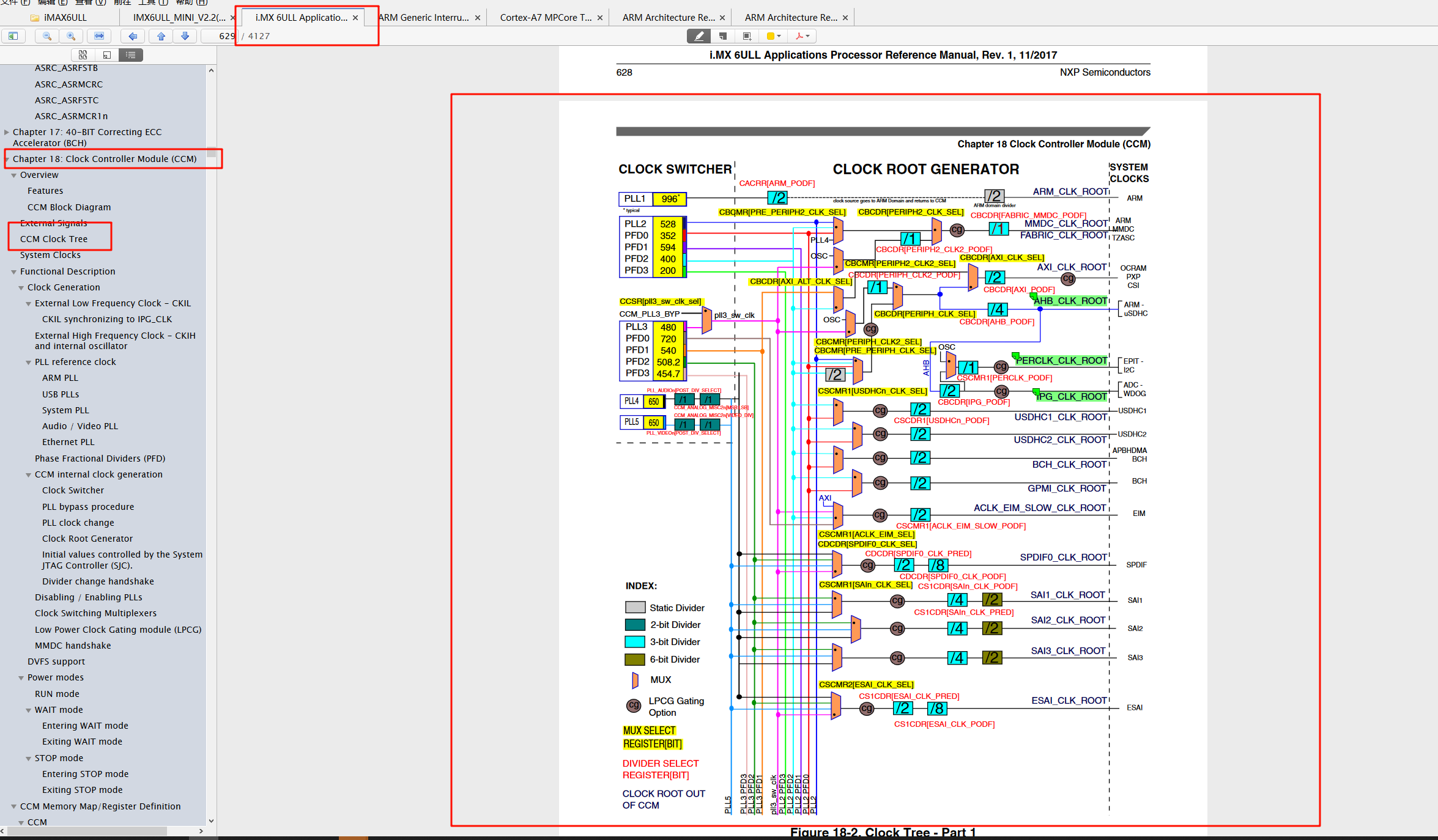

二、时钟树里的组成:

三、时钟树

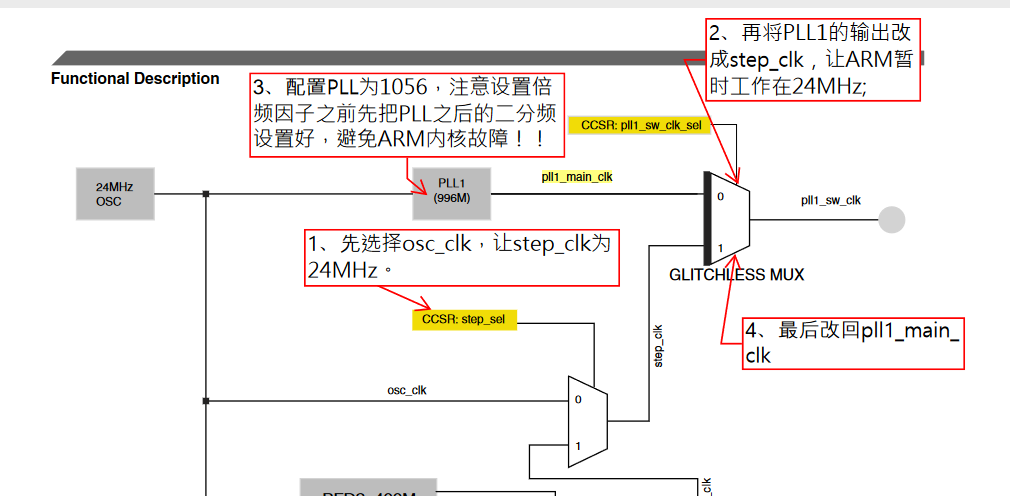

- 时钟配置需遵循安全流程:先降低目标路径时钟频率,再修改PLL参数,最后切回主路径,避免因频率突变导致CPU死机。

- 具体操作包括将ARM主频从默认396MHz提升至528MHz,通过设置PLL1倍频系数为88,并正确配置CCM相关寄存器完成。

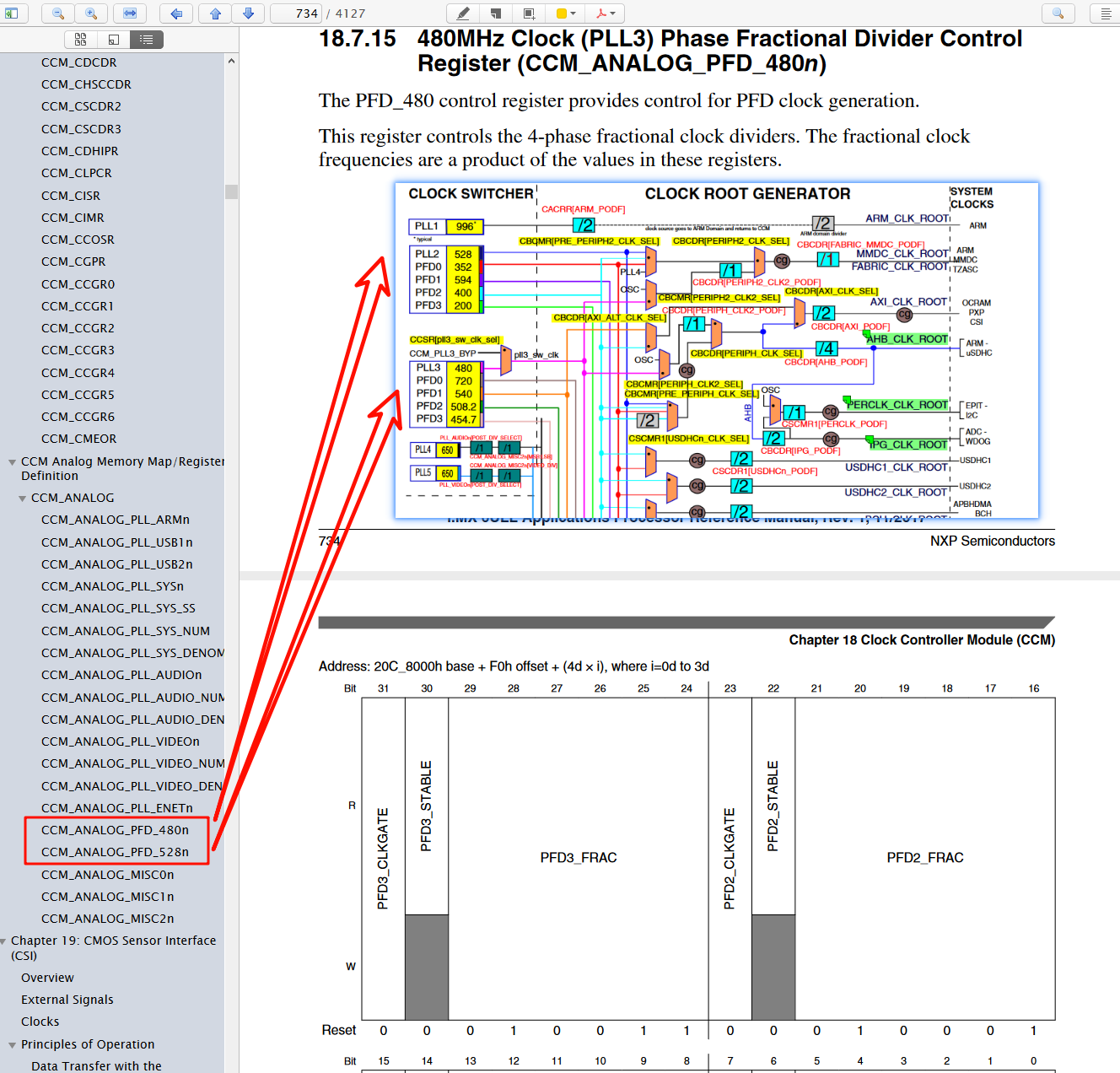

- 同步配置PLL2下的四个PFD分频器,分别输出352MHz、594MHz、396MHz和297MHz,以满足不同外设的时钟需求。

- 对PLL3下的PFD也进行相应设置,支持USB高速通信所需的720MHz等频率。

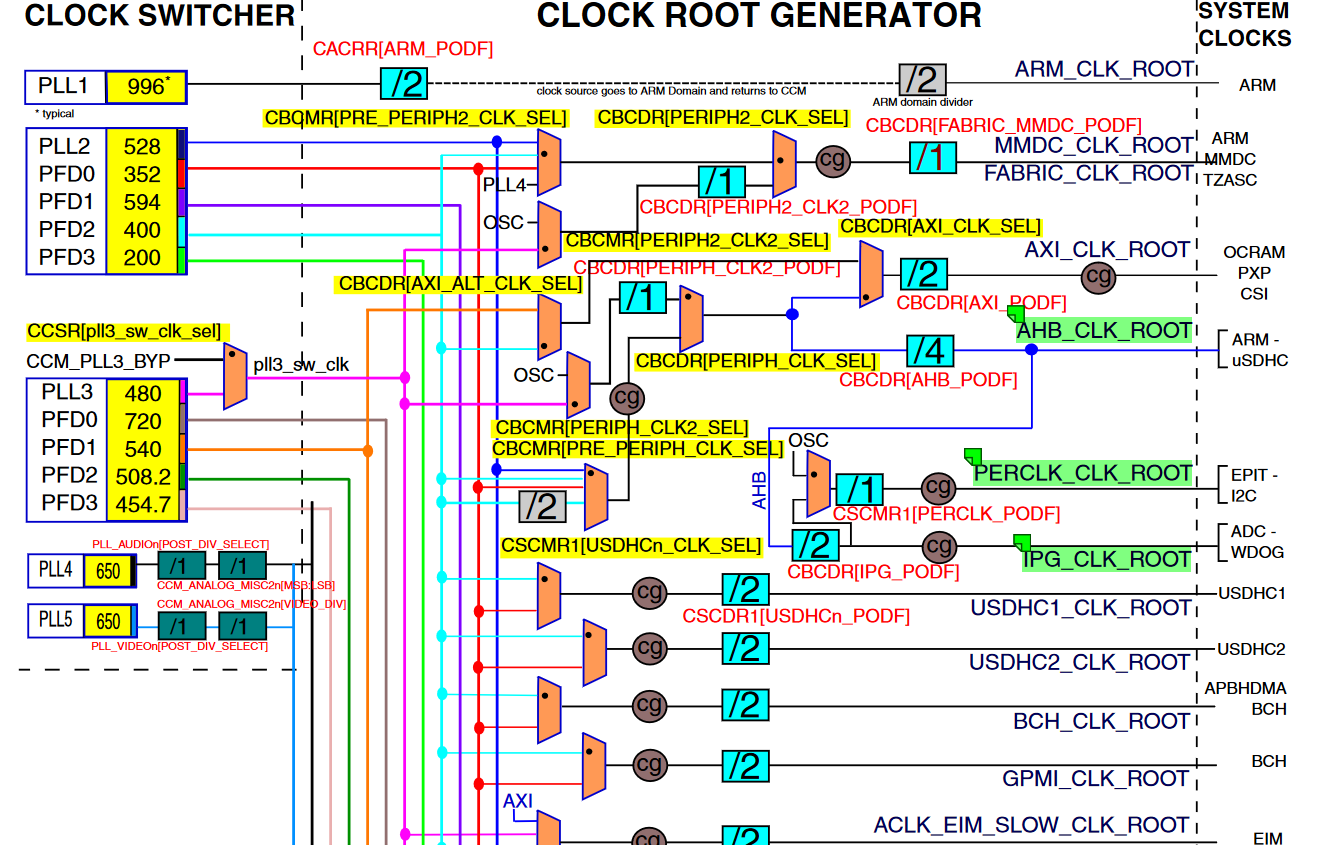

左下角四种分频器:

- 灰色的:静态分频器(锁频的无法改)

- 预分频器:2bit(00)3分频(000)6分频(000000)

- 梯形:多路选择器

- cg:时钟门

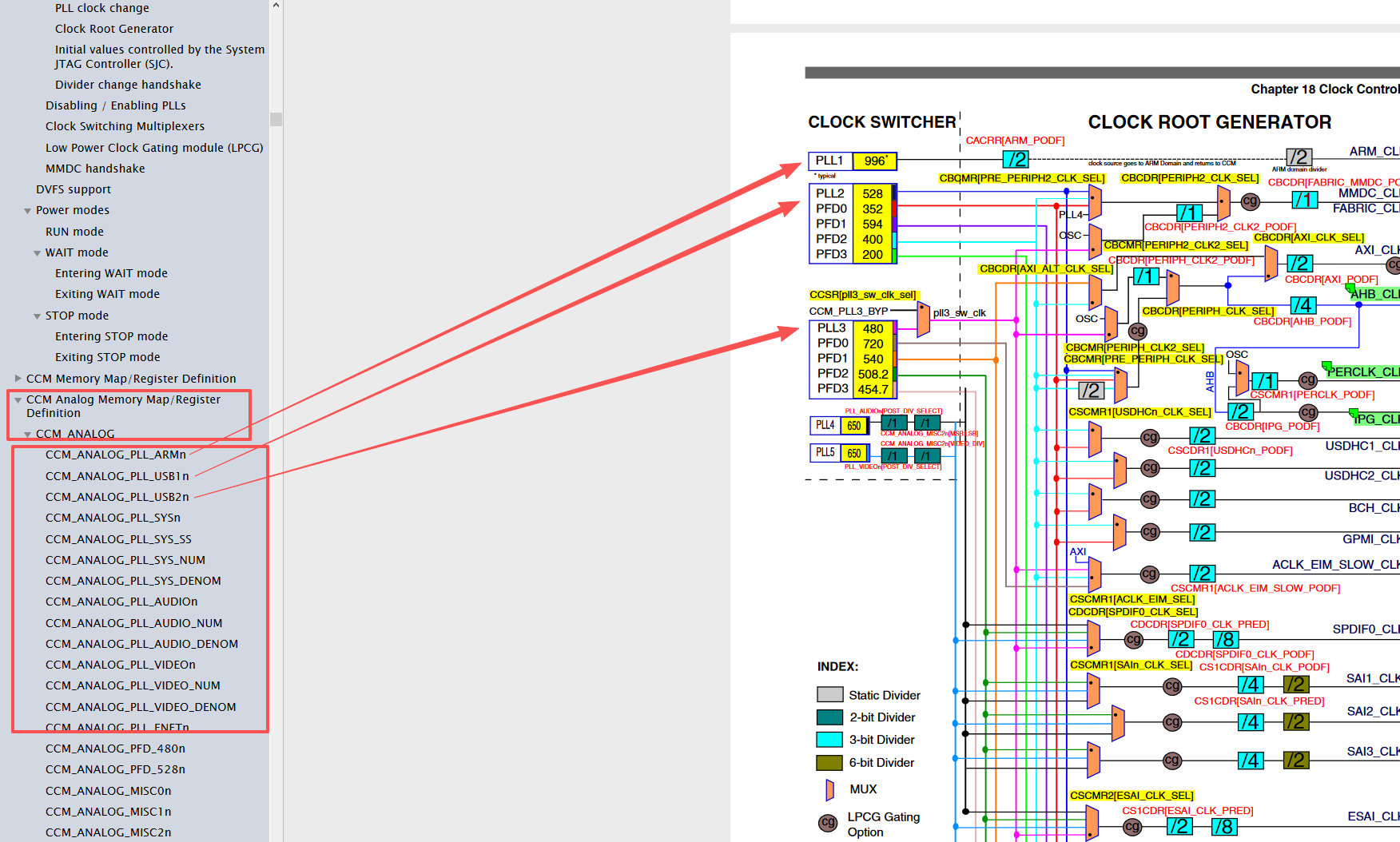

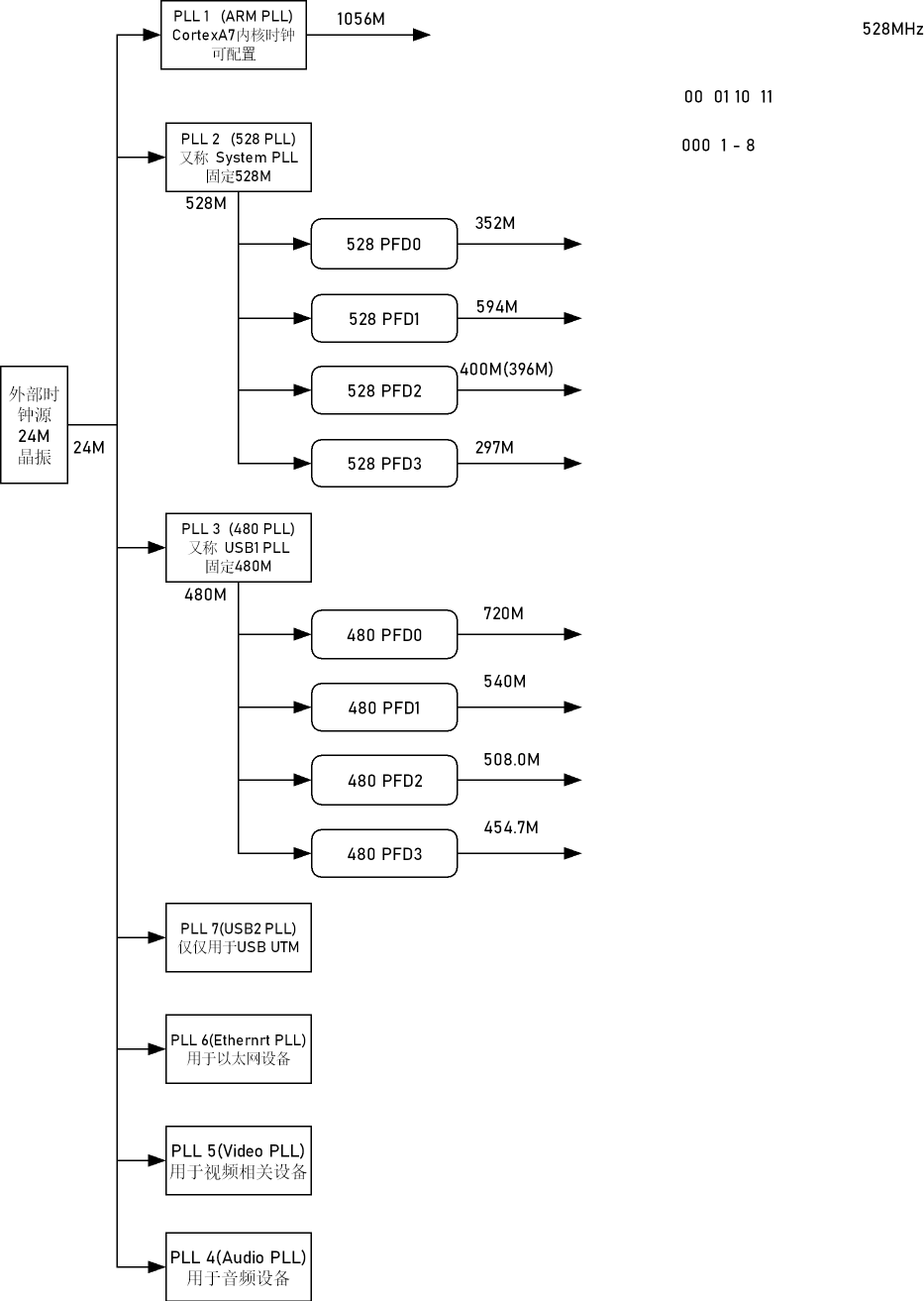

外部时钟24M接入,7个PLL:

- 系统时钟源自外部24MHz晶振,经内部锁相环(PLL)倍频后生成高频时钟供给CPU及外设使用。

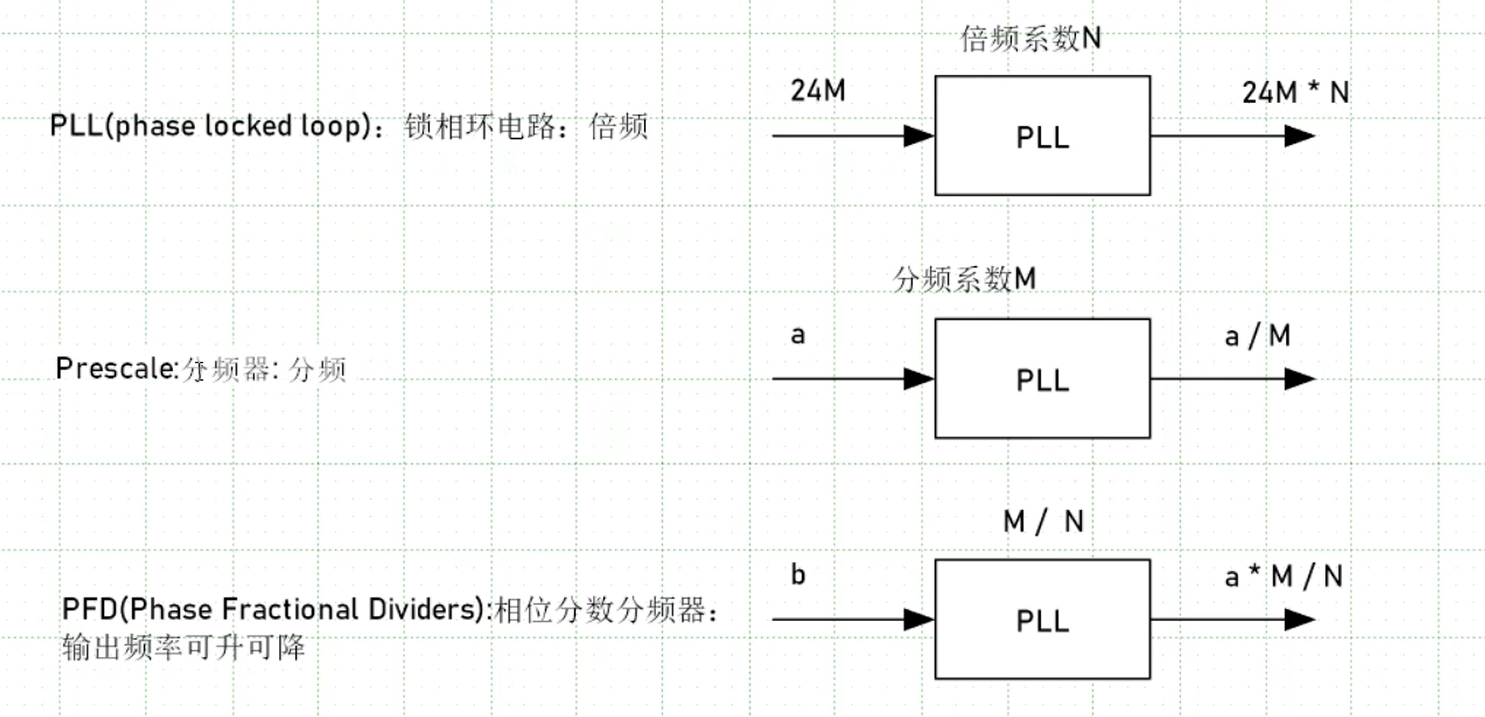

- 核心时钟部件包括锁相环(PLL)用于升频、预分频器(Prescaler)用于降频,以及相位分数分频器(PFD)支持灵活的频率变换。

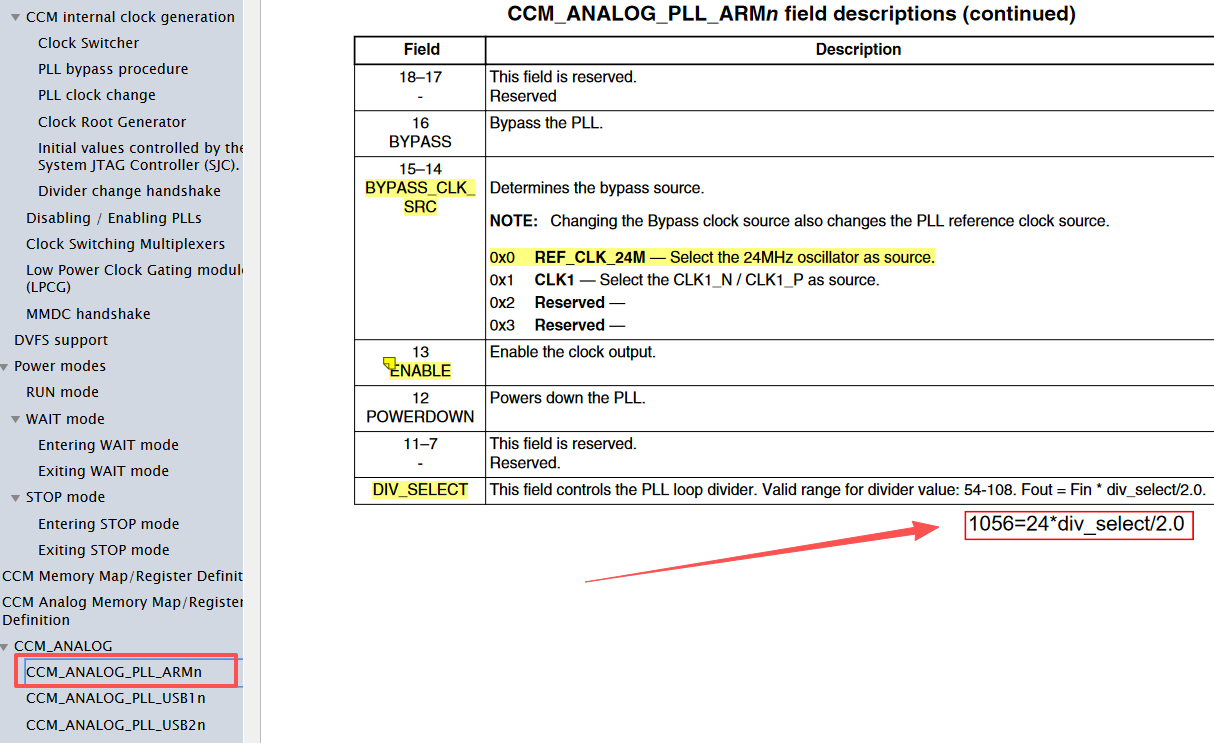

1.第一个PLL1(ARM PLL):可配置,用于生成CPU主频

tip:ARM工作时钟配置:先配分频值,再配倍频值(减小波动的影响)

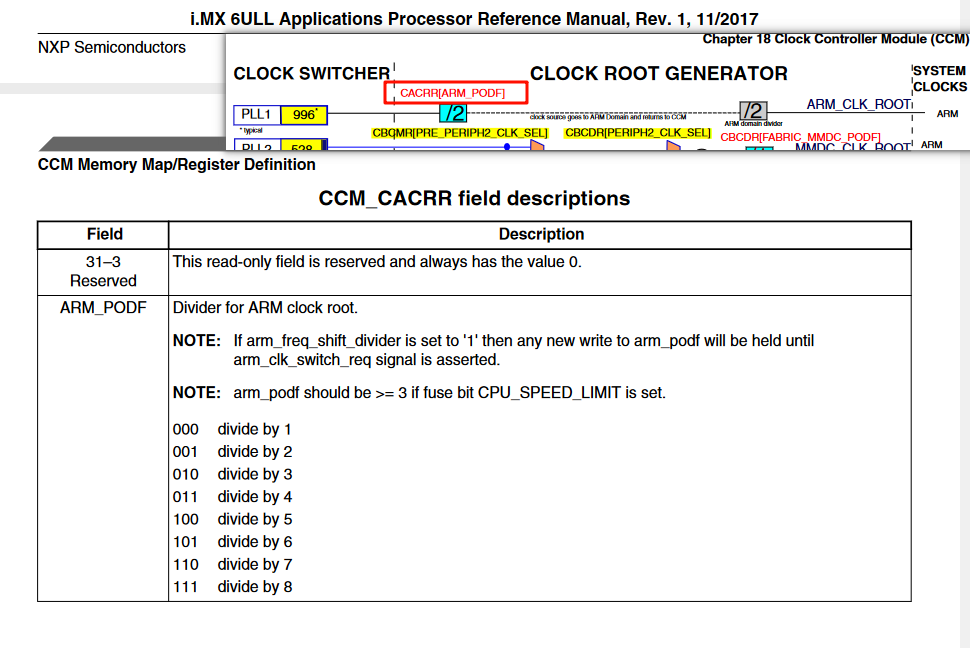

1.1CACRR[ARM_PODF] 先清零再二分频(001)

1.2、配置PLL倍频

防止倍频破坏ARM:引入备用时钟源,经过选通门先短路PLL,设置倍频,再重新链接PLL

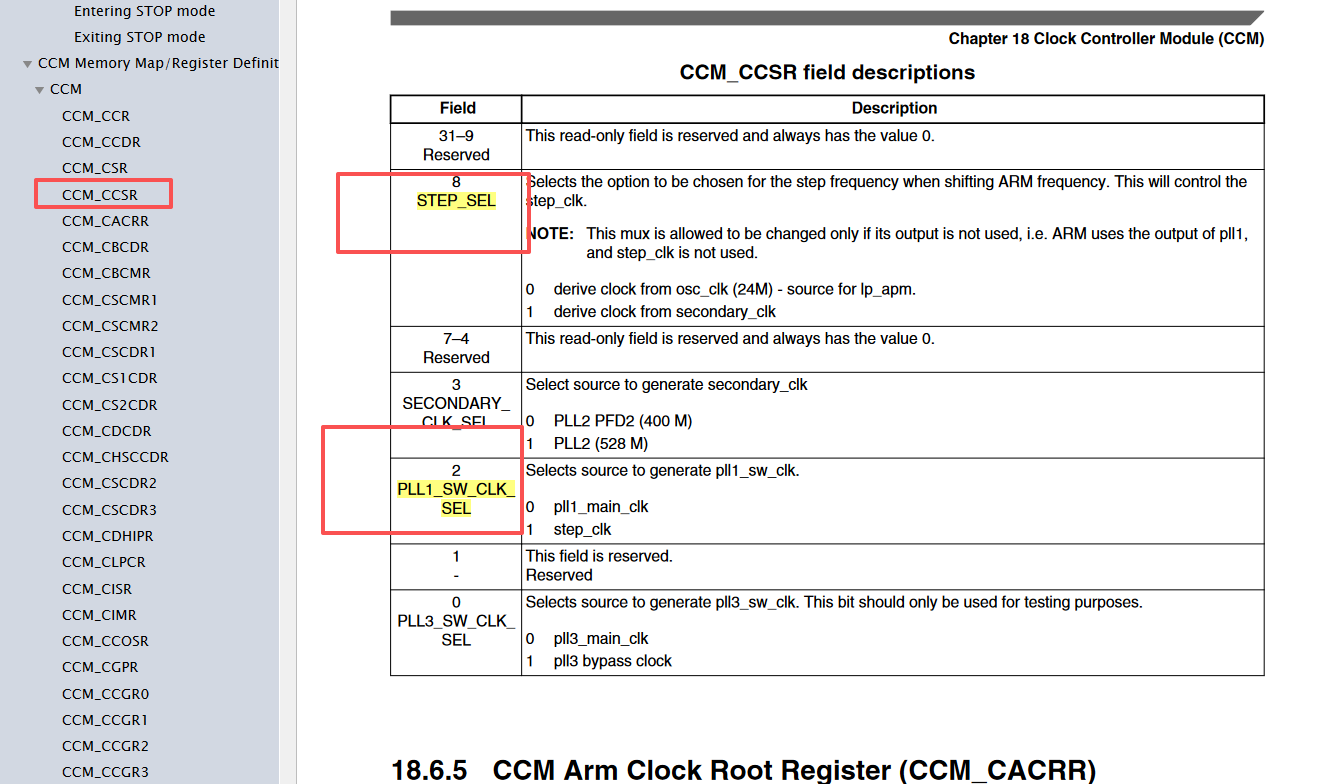

step1:CCMS_TEP_SEL(bit8置0)

step2:CCMS_PLL1_SW_CLK_ SEL设置为;step_clk(bit2 置1)

step3:PLL计算倍频系数

- 设置88倍频系数

- 使能

- 24M时钟源 选0x0

step4:CCMS_PLL1_SW_CLK_ SEL设置为;pll1_main_clk(bit2 置0)

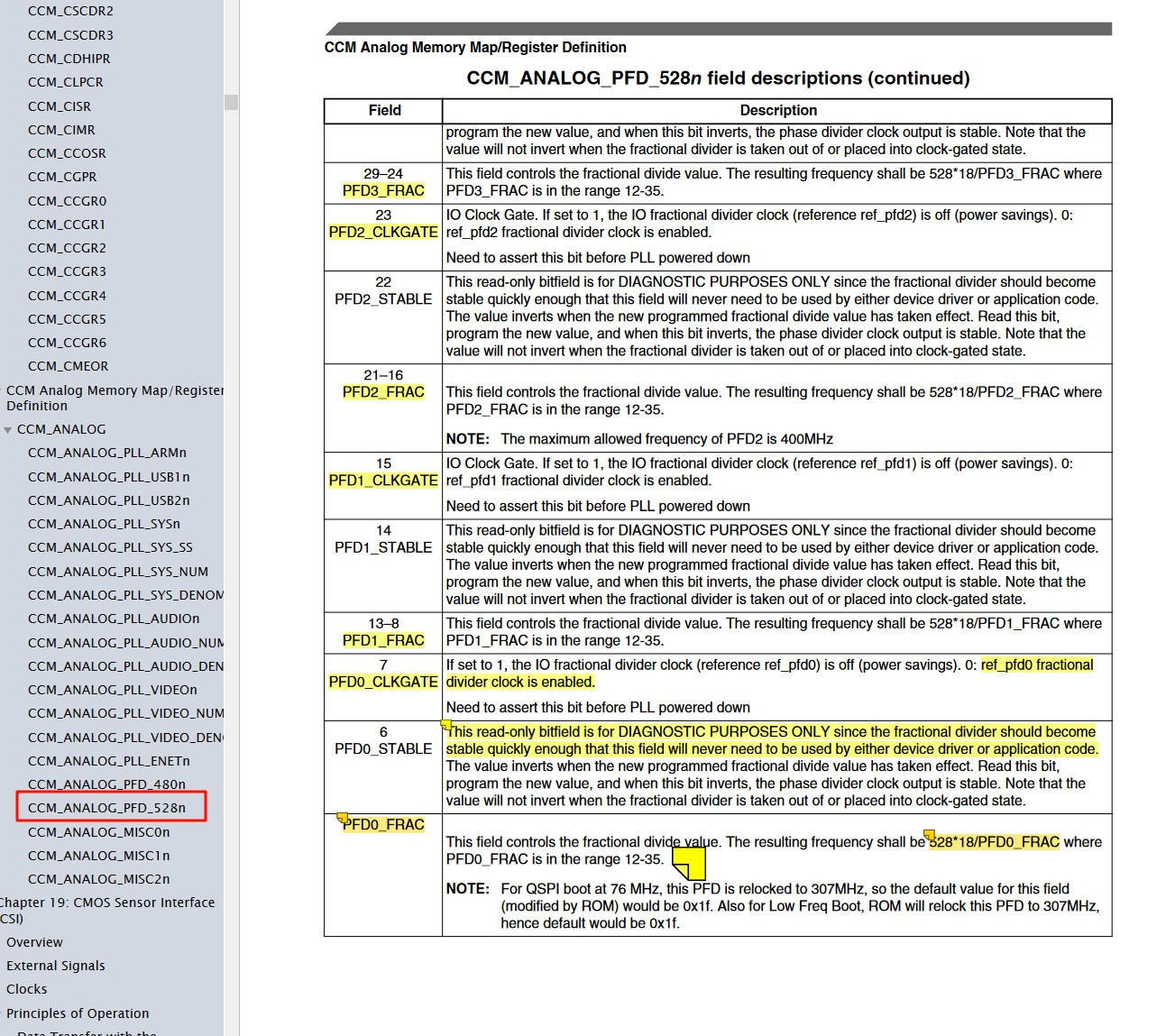

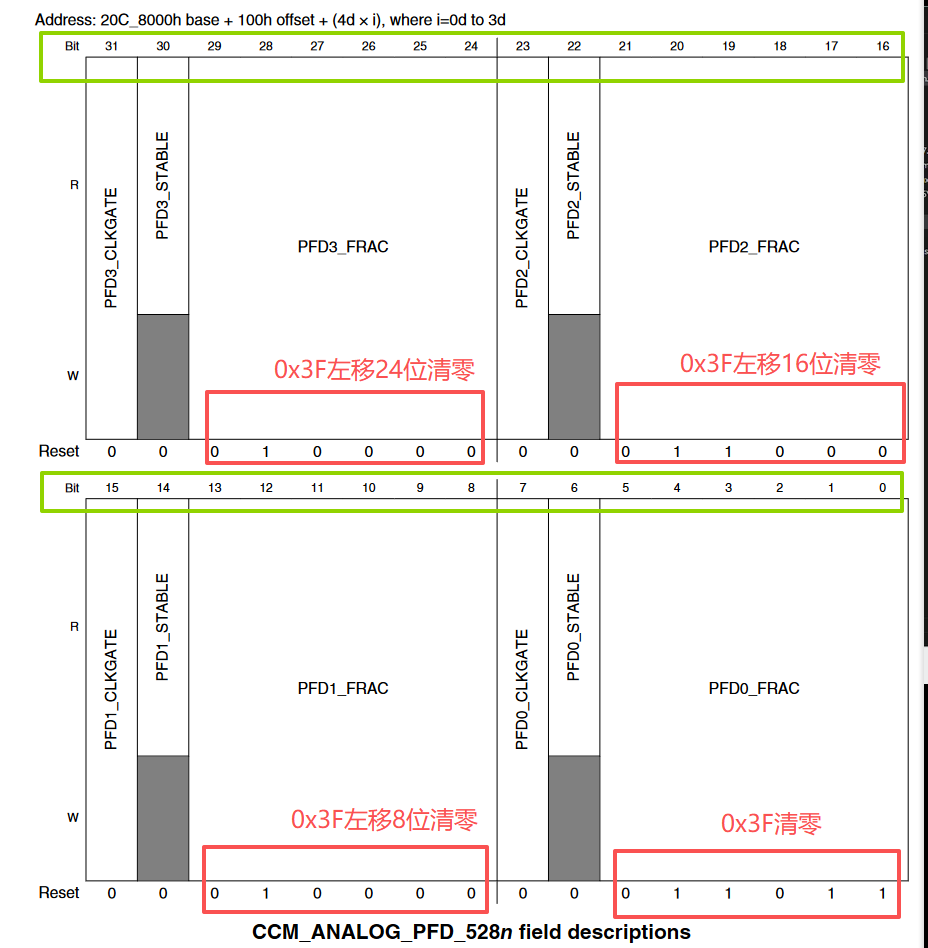

/* 1. 先让 CPU 二分频,降低频率冲击 */CCM->CACRR &= ~(7 << 0); /* 清 ARM_PODF */CCM->CACRR |= (1 << 0); /* 写 1 → ÷2 *//* 2. 切到 PLL1 旁路,锁相环可安全改倍频 */CCM->CCSR &= ~(1 << 8); /* BYPASS=0 允许旁路 */CCM->CCSR |= (1 << 2); /* PLL1_BYPASS=1 正式旁路 *//* 3. 改 PLL1 倍频系数 DIV_SELECT = 88* fvco = 24 MHz × 88 = 2112 MHz */unsigned int t = CCM_ANALOG->PLL_ARM;t &= ~(0x7F << 0); /* 清旧倍频 */t |= (88 << 0); /* 新倍频 */t |= (1 << 13); /* ENABLE=1 */t &= ~(3 << 14); /* 保留默认值 */CCM_ANALOG->PLL_ARM = t; /* 写入,PLL 重新锁定 *//* 4. 退出旁路 → 新时钟立刻送到内核 */CCM->CCSR &= ~(1 << 2); /* PLL1_BYPASS=0 */2第二个叫PLL2(528PLL)倍频锁频,固定输出528M时钟,不可通过寄存器修改,输出四个PFD

2.1计算分频系数:

2.2先清零

- t = CCM_ANALOG->PFD_528;

- t &= ~0x3F3F3F3F; /* 清 4 个 FRAC */

2.3在对应位置置数

t |= (27 << 0) | (16 << 8) | (24 << 16) | (32 << 24);

CCM_ANALOG->PFD_528 = t;

3第三个是PLL3(480PLL或USB PLL),输出四个PFD相位分数分频器

(同理):

- t = CCM_ANALOG->PFD_480;

- t &= ~0x3F3F3F3F;

- t |= (12 << 0) | (16 << 8) | (17 << 16) | (19 << 24);

- CCM_ANALOG->PFD_480 = t;

/* 5. 配置 528_PLL 的 4 路 PFD,给 AHB/IPG/USDHC 等用* PFDx = 528 MHz × 18 / PFDx_FRAC */t = CCM_ANALOG->PFD_528;t &= ~0x3F3F3F3F; /* 清 4 个 FRAC */t |= (27 << 0) | (16 << 8) | (24 << 16) | (32 << 24);CCM_ANALOG->PFD_528 = t;/* 6. 配置 480_PLL 的 4 路 PFD,给 UART/SPDIF 等用 */t = CCM_ANALOG->PFD_480;t &= ~0x3F3F3F3F;t |= (12 << 0) | (16 << 8) | (17 << 16) | (19 << 24);CCM_ANALOG->PFD_480 = t;4其他PLL

第七个PLL7(与USB2 PLL)用以测试USB1的设备,即PLL3

PLL6(用以以太网设备)

PLL5(用以视频设备)

PLL4(用以音频设备)

有源蜂鸣器(1插电即响)(2插入不同频率的PWM波 输出不同音调)

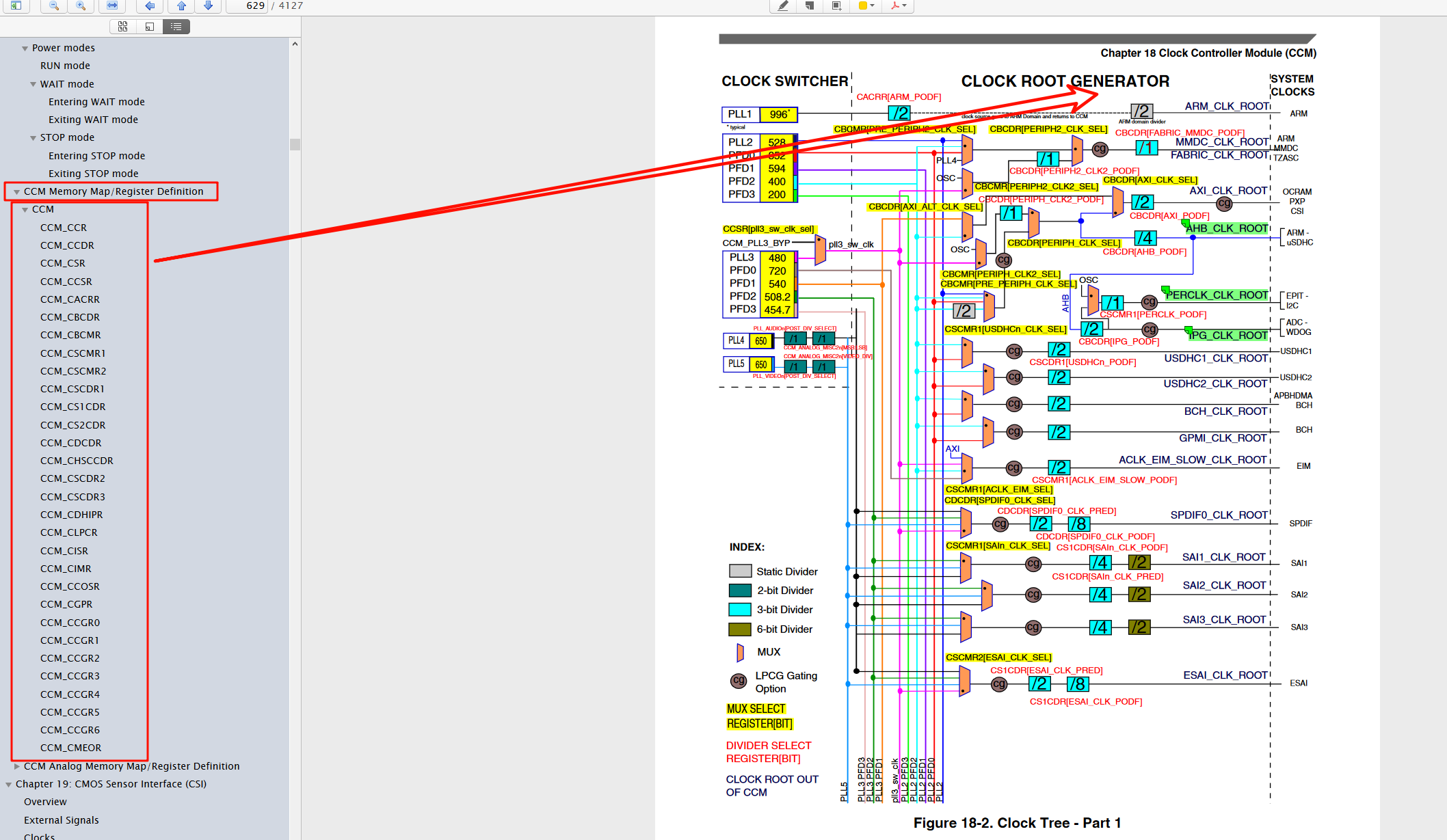

四、时钟根配置

整个时钟树分为三类:

1时钟选择器(配置在CCM Analog Memory Map/Register Definition)

2时钟根生成器(配置在CCM Memory Map/Register Definition)

3系统时钟

注意:

AHB总线时钟、IPG外设时钟等时钟根需基于主PLL输出进行二次分频,确保数据传输与CPU运算协调。

- 计划将AHB时钟设为132MHz,IPG及外设时钟设为66MHz,以平衡性能与功耗。

- 时钟门控(Clock Gating)机制可用于关闭闲置模块的时钟供应,降低系统能耗

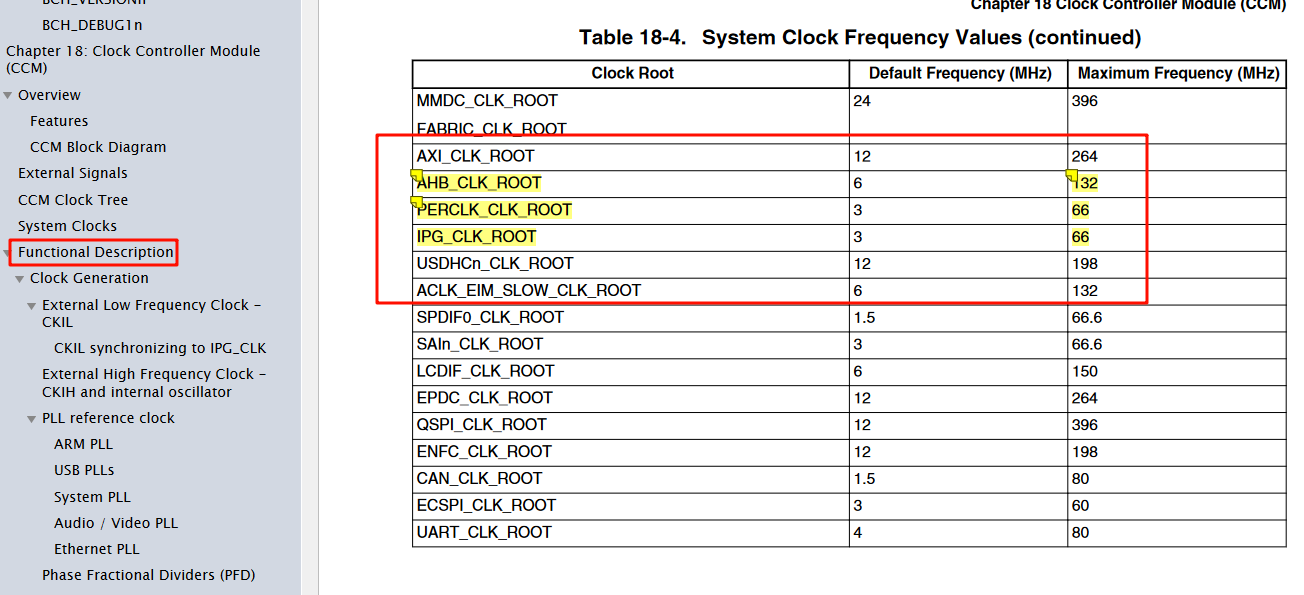

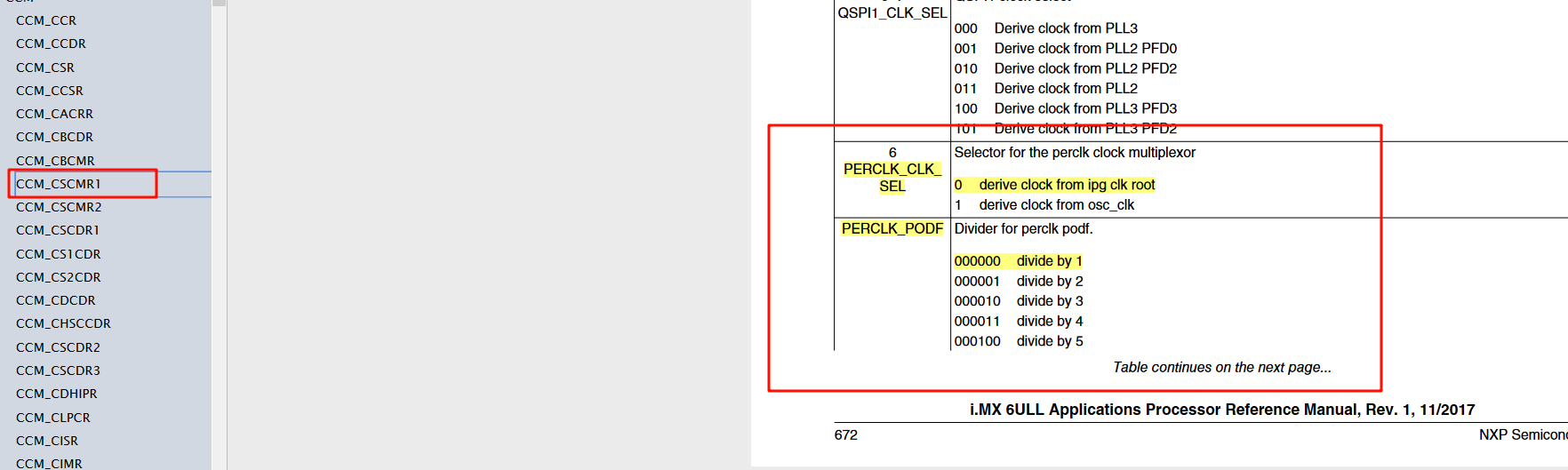

1、三种时钟根工作范围:

AHB_CLK_ROOT 6-132

PERCLK_CLK_ROOT 3-66

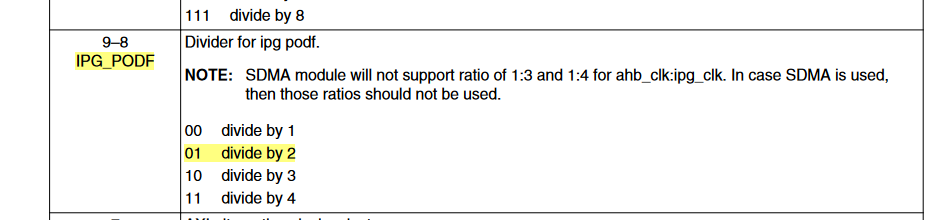

IPG_CLK_ROOT 3-66

确定好配置方案:

1配置AHB_CLK_ROOT的时钟树

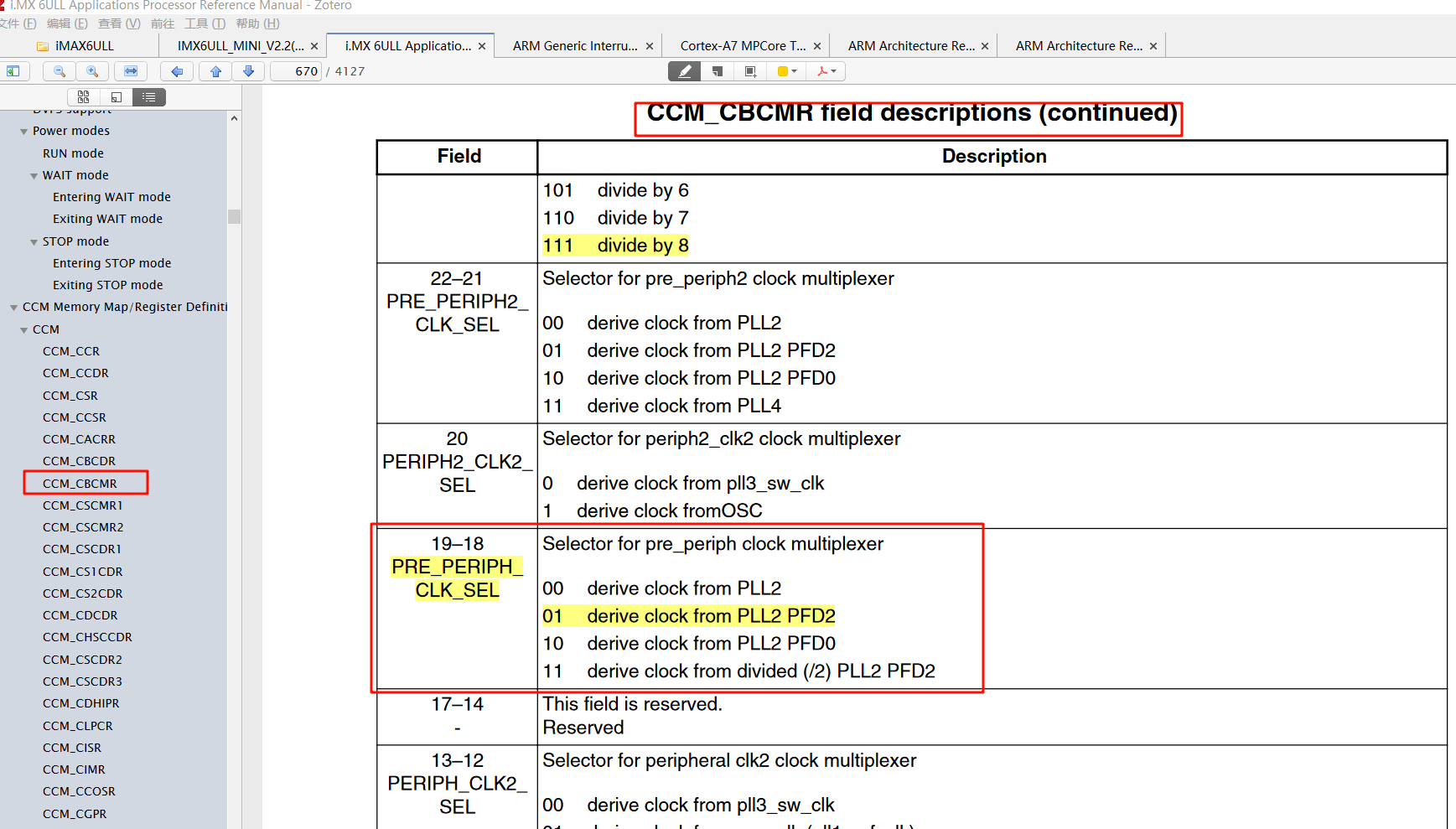

1.1CBCMR的bit18-19:PERIPH_ CLK_SEL 配置为从PFD2(先清零再置01)(396Mhz)

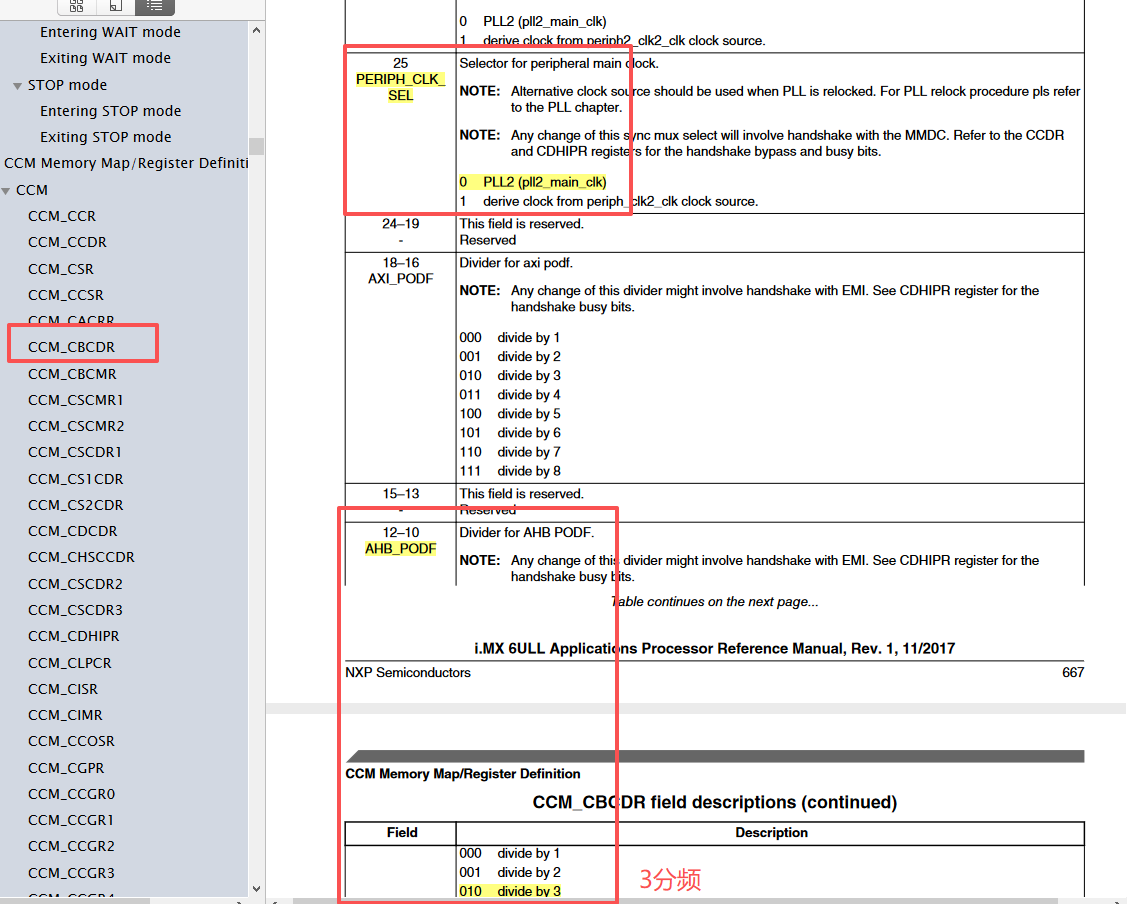

2 CBCDR要配置两个地方 10-12和 25(3分频为 132HZ )

2.配置IPG_CLK_ROOT的时钟树

在前面基础上,增加(2分频)(66Mhz)

3.配置PERCLK_ROOT的时钟树

在前面基础上增加(1分频 66MHZ)

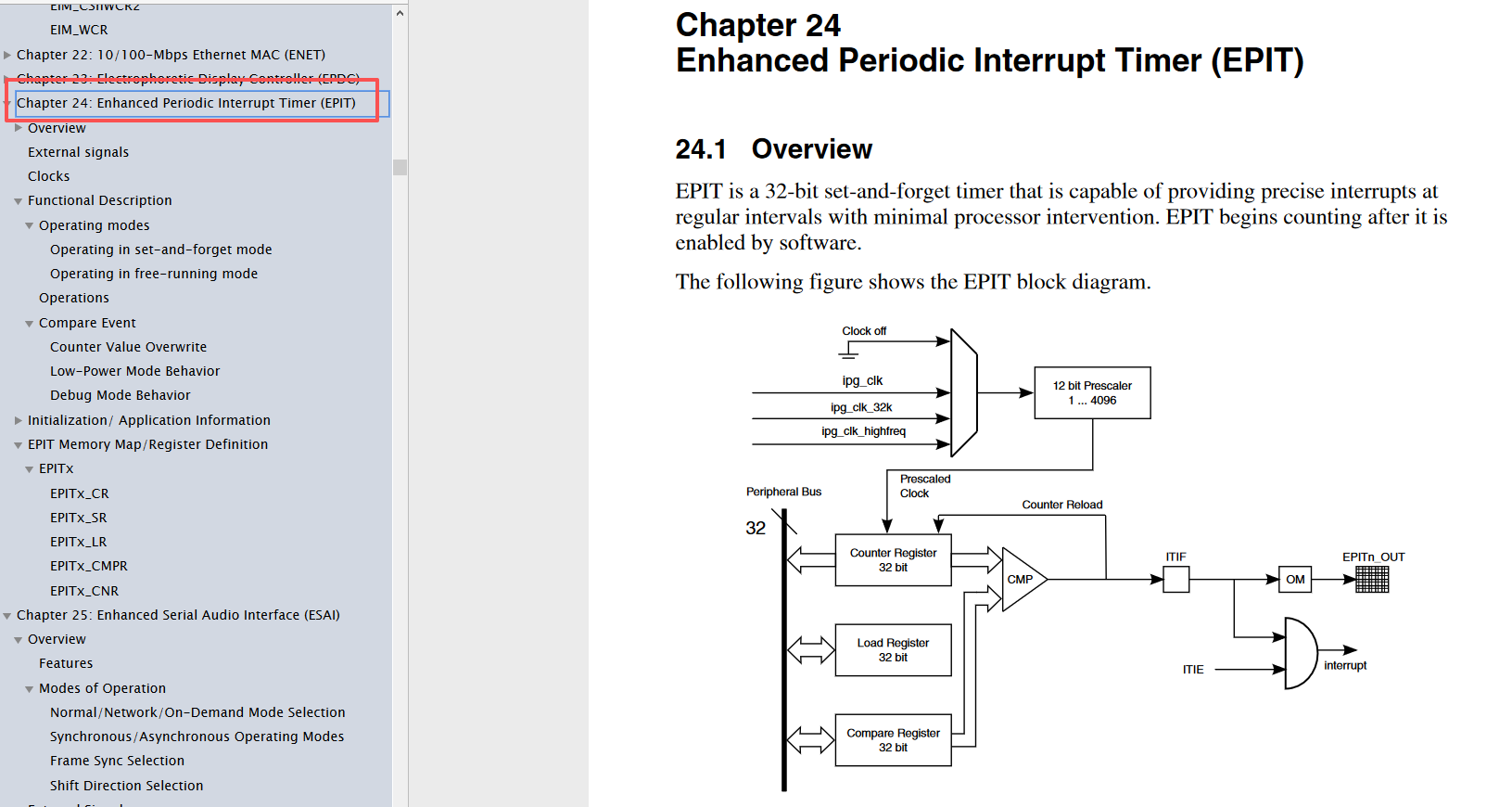

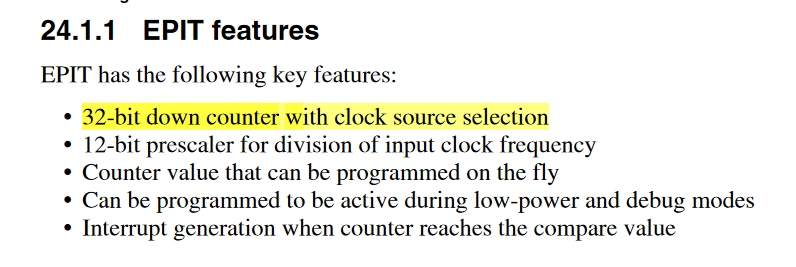

五、增强型周期中断定时器(epit)

1.32位 减类型时钟

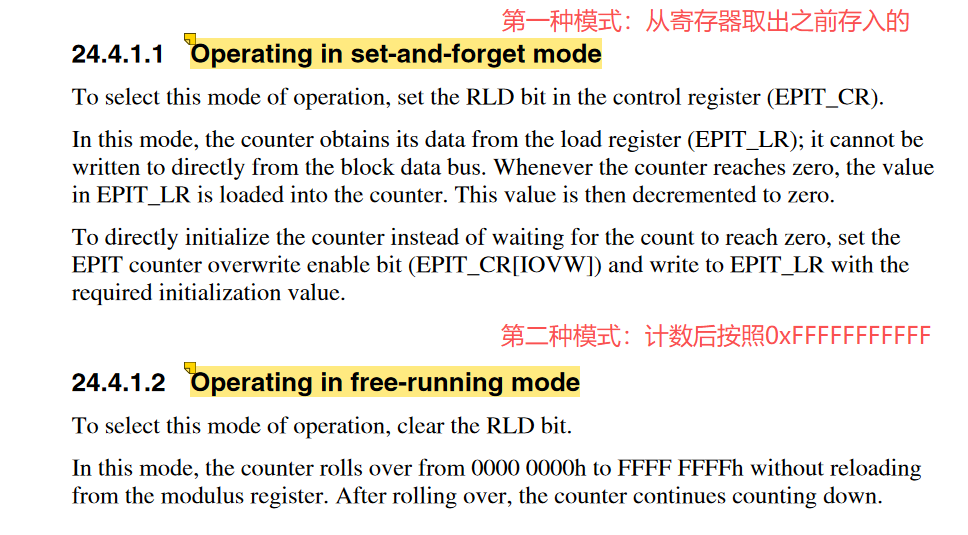

2两种模式:

0当计数器达到零时,它会从模数寄存器重新加载(设置并忘记模式)

1当计数器达到零时,它会滚动到0xFFFFFFFF(自由运行模式)

3、关于寄存器:

计数寄存器,然后减减,直到和比较寄存器相等,重复进行

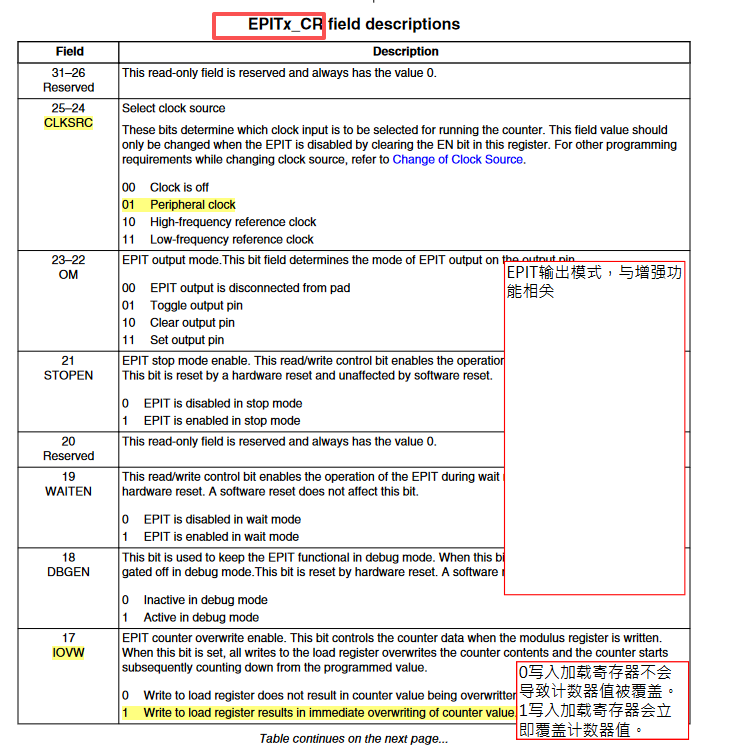

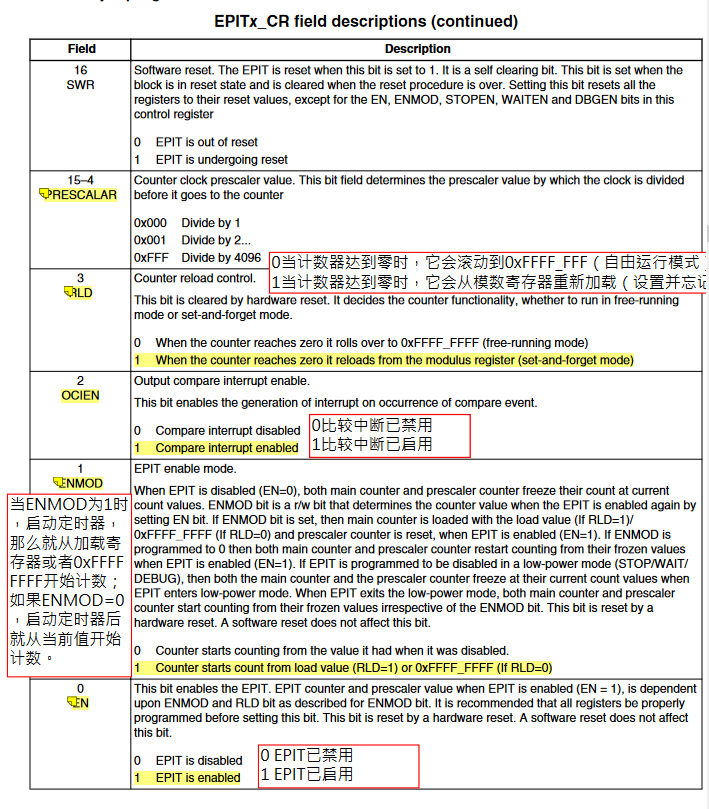

3.1EPITx_CR:

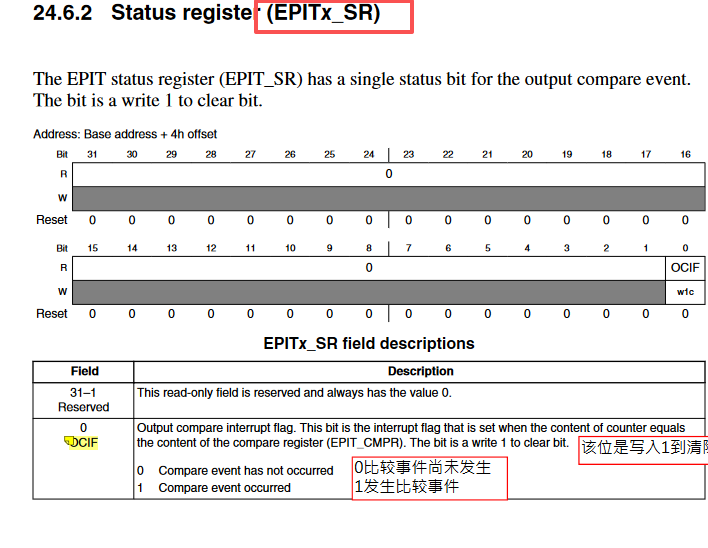

3.2EPITx_SR:

3.3EPITx_LR、3.4EPITx_CMPR、3.5CNR::

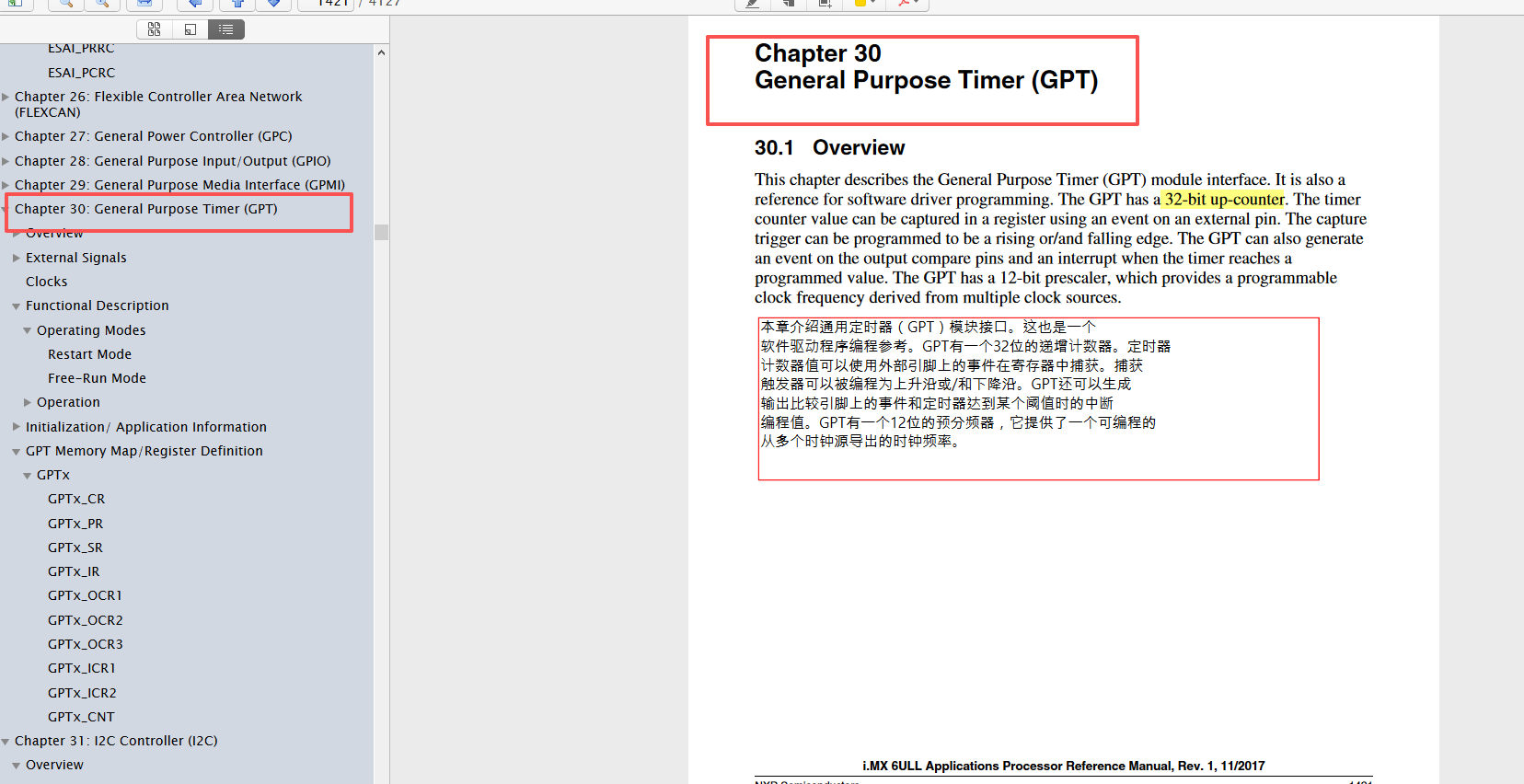

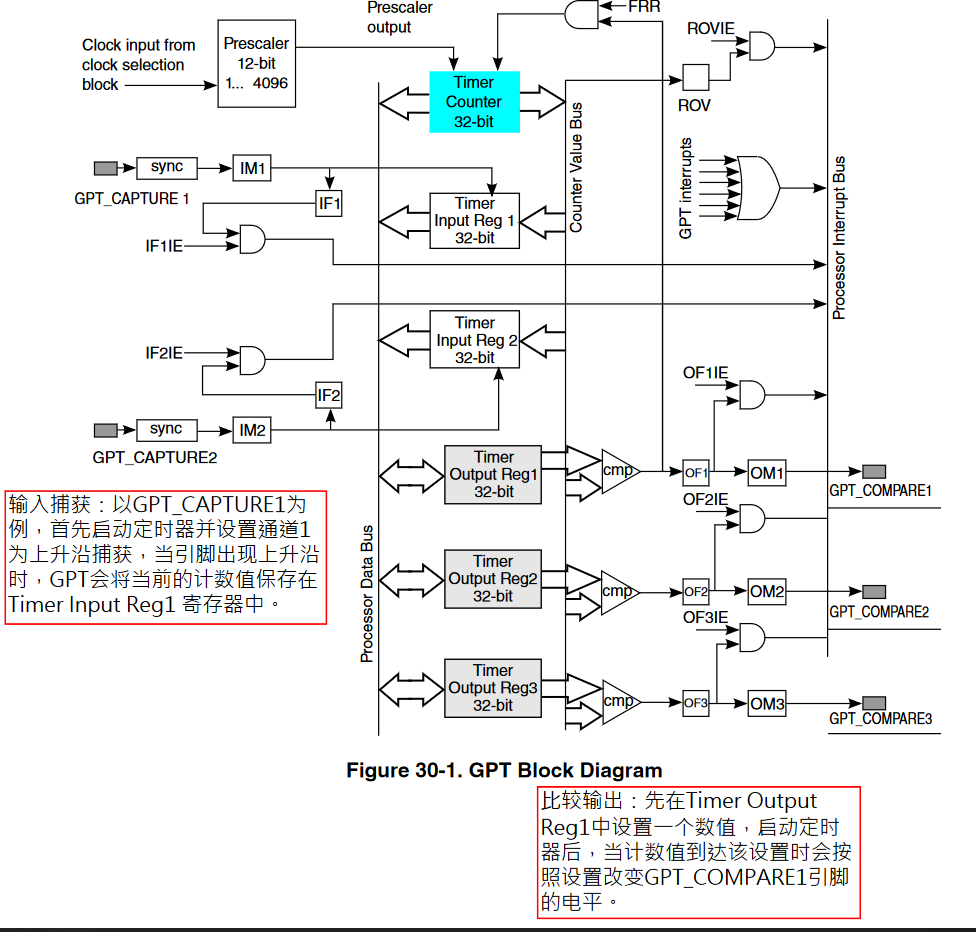

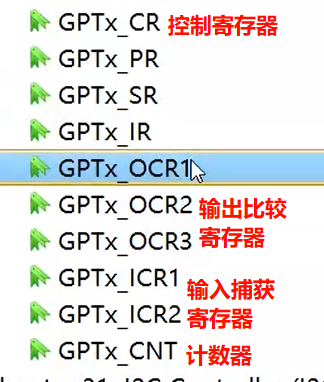

六、通用中断定时器(gpt)

GPT通用中断计数器的应用:

输入捕获(连接到一个脉冲产生器 红外对管or其他器件)、输出,计算两个脉冲之间时间对应的计数寄存器的里的指,获得了两个脉冲hi间的时间差,进一步计算到脉冲周期or频率,延伸到测速的场景:

输出比较器可以设置三个数值,当计数器的值增加到与这些比较器值相等时,会触发中断。这可以用于产生PWM(脉宽调制)信号,通过调节占空比来输出方波。PWM波可以通过外围芯片将数字信号模拟成模拟信号,如正弦波,用于驱动电机。

PWM波的应用场景之一是电机的闭环控制。通过一边控制转速的增减,另一边测试转速,可以通过闭环控制来调节电机的转动。这种方法允许精确控制电机的速度和方向,实现高效的电机驱动和控制。

- EPIT(增强型周期中断定时器)支持set-and-forget和free-running两种模式,前者只需初始化一次即可持续运行,CPU干预极少,适合实现周期性中断(如每秒翻转LED)。

- GPT(通用定时器)具备输入捕获和输出比较两大功能:输入捕获可用于测量脉冲时间差以计算频率或转速;输出比较可设置三路PWM波,通过调节占空比控制电机等设备。

- GPT在free-running模式下可封装为精准延时函数(毫秒/微秒级),其工作流程包括读取计数器初值、循环等待并累计时间差直至达到目标时长。

- EPIT常用于操作系统的时间片轮询调度,而GPT则更适用于通用外设的计时任务。