AXI4 协议

一、AXI4简介

AXI4(Advanced eXtensible Interface 4)是ARM公司推出的高性能片上总线协议,属于AMBA(Advanced Microcontroller Bus Architecture)标准的一部分。它专为高带宽、低延迟的片上通信设计,广泛应用于处理器、DSP、FPGA等复杂系统中。AXI4包含三个变体:

- AXI4:标准版本,支持高带宽内存映射通信。

- AXI4-Lite:简化版,用于寄存器等简单设备的轻量级访问。

- AXI4-Stream:无地址协议,适用于高速数据流传输(如视频、音频)。

二、写数据

一、写地址通道

一、不重要信号:

| 信号名 | 信号源 | 信号介绍 |

AWID | mastar | 写地址ID。这个信号是写地址组的标识标签的信号 |

| AWLOCK | mastar | 提供有关传输的原子特性的其他信息。 |

AWCACHE | mastar | 总线存储类型 |

AWPROT | mastar | 保护类型。他的信号表明事务的特权和安全级别,以及该事务是数据访问还是指令访问。 |

AWQOS | mastar | 服务质量,QoS为每个写事务发送的QoS标识符。仅在axis4中实现。 |

AWREGION | mastar | 区域标识符。允许从机上的单个物理接口用于多个逻辑接口。仅在axis4中实现。 |

AWUSER | mastar | 用户信号。可选写地址通道中的用户自定义信号。仅在axis4中支持 |

二、重要信号

| 信号名 | 信号源 | 信号介绍 |

AWADDR | mastar | 写地址.写地址给出了写突发事务中第一次传输的地址 |

AWLEN | mastar | 突发长度,突发长度给出了突发中传输的确切数量。此信息确定与该地址相关的数据传输的数量。这在AXI3和AXI4之间有所不同 |

AWSIZE | mastar | 突发大小。这个信号表示在突发中每次传输的大小 |

AWBURST | mastar | 突发类型。突发类型,加上大小信息(AWSIZE),详细说明了如何在突发中计算每个传输的地址。 |

AWVALID | mastar | 写地址有效。该信号表明通道正在发送有效写入信号地址和控制信息 |

AWREADY | slaver | 写地址准备好。这个信号表明从机准备好接受一个地址和相关的控制信号:1 =从机准备好了0 =从机还没有准备好 |

二、写数据通道

一、不重要信号:

| 信号名 | 信号源 | 信号介绍 |

WID | mastar | 写ID标签。这个信号是写入数据传输的ID标签。仅在axis3中支持。 |

WUSER | mastar | 用户信号。可选写数据通道中的用户自定义信号。仅在axis4中支持 |

二、重要信号:

| 信号名 | 信号源 | 信号介绍 |

WDATA | mastar | 写数据 |

WSTRB | mastar | 写选通(strobe)。这个信号指示内存中要更新的字节位置。写数据总线的每8位都有一个写选通。因此,WSTRB[n]对应于WDATA[(8 × n) + 7:(8 × n)],即每一位选通自己对应的Byte |

WLAST | mastar | 写最后一个数据。这个信号指示写突发中的最后一次传输。 |

WVALID | mastar | 写有效。这个信号表示有效的写数据和选通可用:1 = 写数据和WSTRB可用 ; 0 =写数据和WSTRB不可用。 |

WREADY | slaver | 写准备好信号。这个信号表示从机可以接受写数据 |

写选通介绍:假如32数据我们只要写入低十六位,只要将WSTRB设置为0011即可。

verilog

// 只更新低16位数据

WDATA = 32'hAABBCCDD;

WSTRB = 4'b0011; // 只使能最低两个字节// 这将导致:

// - 字节0 (DATA[7:0]) = DD (被写入)

// - 字节1 (DATA[15:8]) = CC (被写入)

// - 字节2 (DATA[23:16]) = BB (被忽略)

// - 字节3 (DATA[31:24]) = AA (被忽略)三、写响应通道信号

一、不重要信号

| 信号名 | 信号源 | 信号介绍 |

BID | slave | 写ID标签。这个信号是写入数据传输的ID标签。仅在axis3中支持。 |

BUSER | slave | 用户信号。可选写数据通道中的用户自定义信号。仅在axis4中支持 |

二、重要信号

| 信号名 | 信号源 | 信号介绍 |

BRESP | slave | 写响应。这个信号指示写事务的状态。允许的响应有OKAY、EXOKAY、SLVERR和DECERR。 |

BVALID | slave | 写响应有效。这个信号表明一个有效的写响应是可用的:1 =写响应可用0 =写响应不可用 |

BREADY | mastar | 响应ready。这个信号表示主机可以接受响应信息。1 = master就绪0 = master未就绪 |

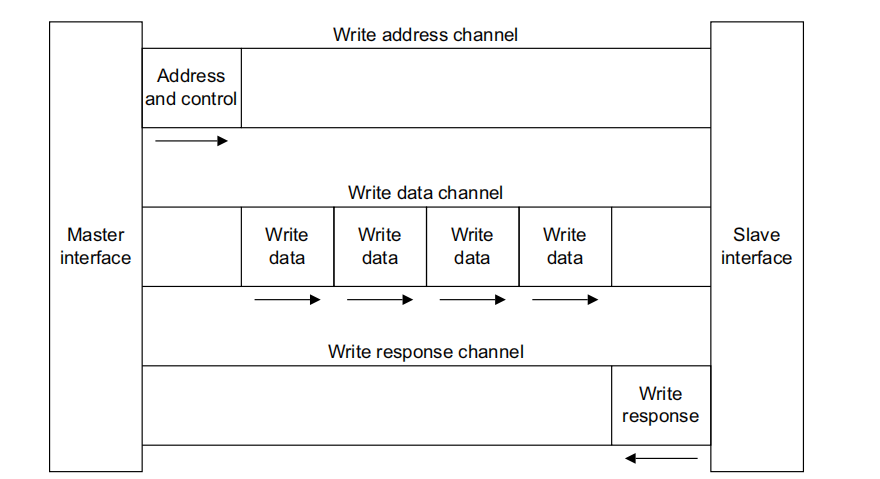

四、写通道介绍

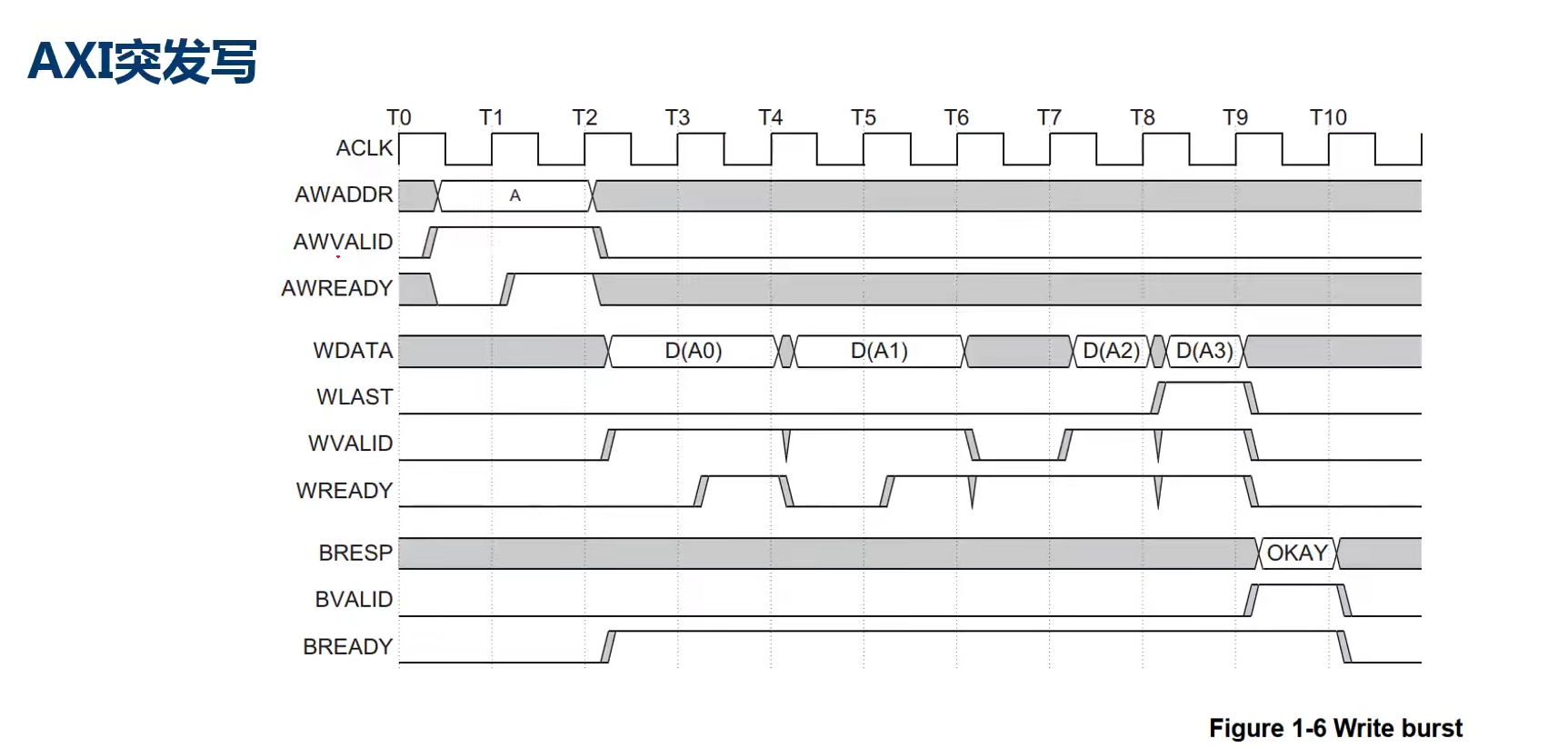

写数据的三个通道是相互独立的。显示写事务如何使用写地址、写数据和写响应通道。

三、读数据

一、读地址通道

一、不重要信号

| 信号名 | 信号源 | 信号介绍 |

ARID | mastar | 读地址ID。该信号是信号读地址组的识别标签 |

ARLOCK | mastar | 提供有关传输的原子特性的其他信息。 |

ARCACHE | mastar | 存储类型。该信号指示事务如何在系统中进行 |

ARPROT | mastar | 保护类型。该信号表示事务的特权和安全级别,以及该事务是数据访问还是指令访问 |

ARQOS | mastar | 服务质量,QoS为每个读事务发送的QoS标识符。仅实现在axis4中 |

ARREGION | mastar | 区域标识符。允许从机上的单个物理接口用于多个接口逻辑接口。仅在axis4中实现 |

ARUSER | mastar | 用户信号。可选读地址通道中自定义信号。仅在axis4中支持 |

二、重要信号

| 信号名 | 信号源 | 信号介绍 |

ARADDR | mastar | 读地址。读地址给出了读突发中第一次传输的地址事务 |

ARLEN | mastar | 突发长度。这个信号表明在一个突发中传输的确切数量。这在AXI3和AXI4之间有所不同 |

ARSIZE | mastar | 突发大小。这个信号表示在突发中每次传输的大小。 |

ARBURST | mastar | 突发类型。突发类型和大小信息决定了如何计算突发内每个传输的地址 |

ARVALID | mastar | 读地址有效。该信号表明通道正在发送有效的读地址和控制信息 |

ARREADY | Slave | 读地址准备好了。这个信号表明从机已经准备好接受一个地址以及相关的控制信号 |

二、读数据通道

一、不重要信号

| 信号名 | 信号源 | 信号介绍 |

RID | Slave | 读取ID标签。该信号是从机产生的读数据组信号的识别标签 |

RRESP | Slave | 读取响应。该信号表示读传输的状态。 |

RUSER | Slave | 用户信号。可选读数据通道中的用户自定义信号。仅在axis4中支持。 |

二、重要信号

| 信号名 | 信号源 | 信号介绍 |

RDATA | Slave | 读数据。 |

RLAST | Slave | 读最后一次。这个信号表示读突发中的最后一次传输 |

RVALID | Slave | 读有效信号。该信号表明通道正在发送所需的读取数据 |

RREADY | mastar | 都准备好信号。这个信号表示主机可以接受读取的数据和响应信息 |

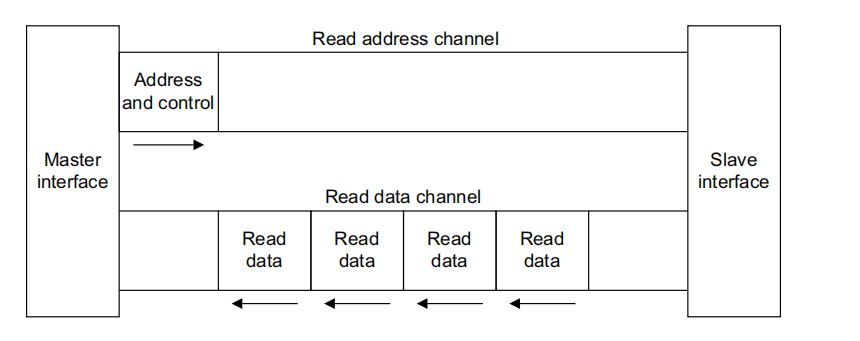

三、读数据介绍

AXI4读事务使用读地址和读数据通道示意:

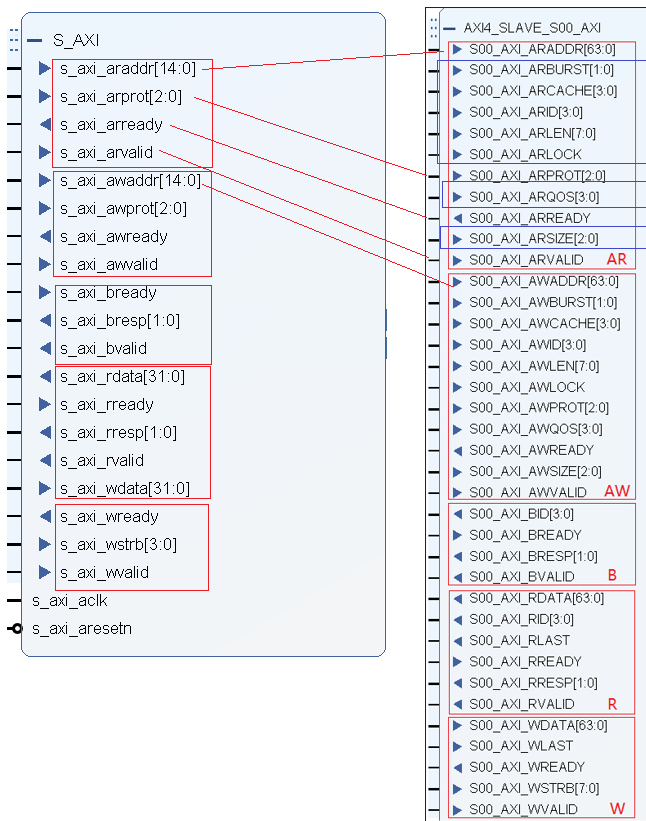

四、AXI4 LIte和AXI4接口对比图。

如下可见AXI4 lite接口相较于AXI4做了很多简化,基本上只保留重要信号。

| 特性 | AXI4-Lite | AXI4 (Full) |

|---|---|---|

| 设计目的 | 简单控制寄存器访问 | 高性能大数据量传输 |

| 突发传输 | 不支持。每次传输只读/写一个数据。 | 支持。可传输大量连续数据(最多256 beat)。 |

| 数据宽度 | 通常固定为 32bit 或 64bit | 支持更宽的数据总线(可到1024bit) |

| 通道信号 | 大幅简化 | 功能完整 |

| 读写通道 | 分离的读/写地址和数据通道 | 分离的读/写地址和数据通道 |

| 事务属性 | 极少(如:非安全、非特权、数据无关) | 丰富(如:内存类型、缓存、缓冲区策略) |

| 使用场景 | 访问IP核的控制状态寄存器(CSR) | 与高带宽内存(DDR)、DMA、高速外设通信 |

| 实现复杂度 | 低,逻辑资源占用少 | 高,逻辑资源占用多 |

| 握手信号 | 必须有(xVALID/xREADY) | 必须有(xVALID/xREADY) |

1. 突发传输 (Burst Transfer)

这是最根本的区别。

AXI4-Lite:每次事务只能传输一个数据单元。例如,要写入4个32位的数据,主设备必须发起4次独立的写事务(每次包含地址 phase 和数据 phase)。这效率低下,但控制简单。

AXI4:支持突发传输。主设备只需提供起始地址和突发长度(Burst Length,例如4),就可以在一次事务中连续传输4个数据。从设备会自动递增地址。这极大地提高了数据传输效率,减少了总线开销。

2. 通道信号简化

AXI4-Lite 移除了AXI4中与高性能操作相关的所有复杂信号,例如:

AxLEN:突发长度。AXI4-Lite 没有这个信号,因为长度固定为1。AxSIZE:突发大小。每次传输的大小必须与数据总线宽度一致(如32位总线就是4字节)。AxBURST:突发类型。固定为增量突发(Incr),但因为长度是1,所以地址也不会变。WLAST:最后一个写数据。因为每次写只有一个数据,所以这个信号不需要。RLAST:最后一个读数据。同理,不需要。AxLOCK,AxCACHE,AxQOS,AxPROT等:事务属性。大部分被移除或固定为常量值。

3.如何选择?

选择使用哪种接口取决于IP核的功能和性能需求:

使用 AXI4-Lite 当:

IP核只需要被配置(例如:设置使能位、中断掩码、控制寄存器)。

IP核只需要提供状态信息(例如:读取状态寄存器、中断状态位)。

数据传输是偶尔的、零星的,对带宽要求极低。

你想要最小化逻辑资源和功耗。

使用 AXI4 当:

IP核需要持续不断地流式传输大量数据(例如:视频帧、音频数据、网络数据包)。

IP核作为DMA控制器,需要在内存和外设之间搬移大块数据。

IP核需要高带宽和低延迟来访问系统内存(DDR)。

性能是首要考虑因素。

五、握手机制

1、基本握手机制

AXI4 使用简单的双向握手协议:

VALID 信号:由发送方驱动,表示数据/地址/控制信息已经准备好并有效

READY 信号:由接收方驱动,表示接收方已准备好接受数据

传输发生在时钟上升沿当 VALID 和 READY 同时为高时

2、AXI4 通道及其握手信号

| 通道 | 方向 | VALID 信号 | READY 信号 | 功能描述 |

|---|---|---|---|---|

| 写地址通道 | 主→从 | AWVALID | AWREADY | 传输写地址和控制信息 |

| 写数据通道 | 主→从 | WVALID | WREADY | 传输写数据和写选通 |

| 写响应通道 | 从→主 | BVALID | BREADY | 返回写操作响应 |

| 读地址通道 | 主→从 | ARVALID | ARREADY | 传输读地址和控制信息 |

| 读数据通道 | 从→主 | RVALID | RREADY | 返回读数据和响应 |

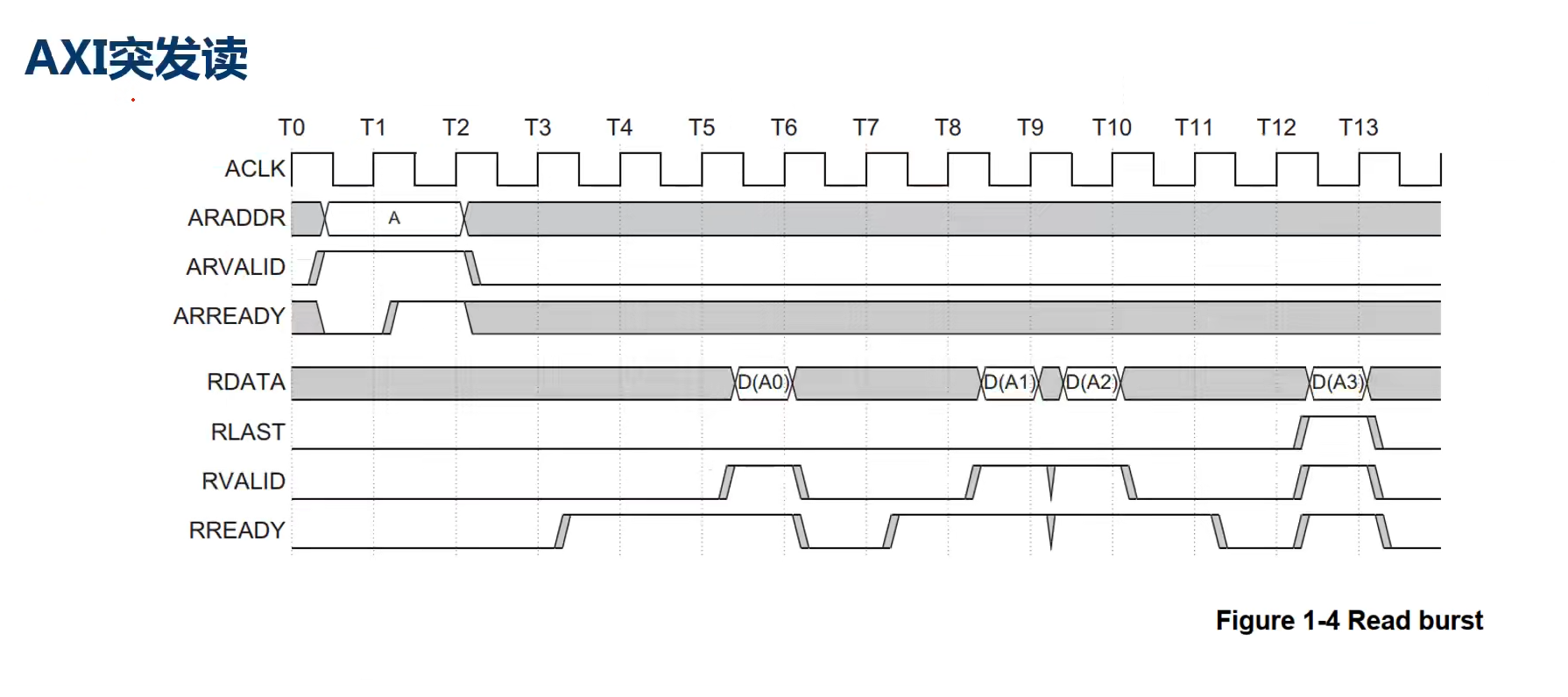

六、突发传输

由图可见在突发读时候,地址必须要在读地址有效和读地址准备信号同时有效时候才能有效。T2时刻上升沿时候可见。然后就是读数据通道。读数据通道下,读有效和读有效准备信号也是同时拉高才有效。然后在读数据通道根据我们读地址信号的数据进行突发传输。但是从机响应的准备信号拉高时和用户读有效拉高时候才传输。突发写同理不过多介绍。