GCKontrol对嵌入式设备FPGA设计流程的高效优化

1 前言

FPGA(Field-Programmable Gate Array,现场可编程逻辑门阵列)是一种可编程的半导体器件,因其硬件可重构性、硬件并行计算能力、低延迟和实时性的优势,广泛应用于数字电路设计、原型验证和系统加速等领域。但开发效率不足以及设计人员门槛较高,正在成为制约其应用落地的最大障碍。

在实际项目中,很多企业都会遇到这样的困境:算法模型已经在仿真环境中跑通,但要真正达到在FPGA芯片上实现模型的功能,却往往要经历数周甚至数月的Verilog代码开发设计、仿真测试和下板调试。这一过程不仅耗时耗力,并且对工程师也有较高的设计门槛,同时在整个开发周期中,需要算法、FPGA工程师密切配合和沟通,稍有不同步就可能导致返工,大大降低了开发验证的效率和增加人力成本。

基于这一痛点,世冠科技GCKontrol平台提供了“图形化建模到自动生成Verilog代码”的新方法,加速算法模型从理论到实践下板验证过程,帮助企业缩短FPGA开发周期和降低人力成本,促进产品化的进程,助力更高效的FPGA设计开发。

2 面临的挑战

在FPGA芯片上验证的算法模型,从理论到实践的全生命周期,以使用专业的工业软件图形化建模仿真为开始,到FPGA工程师编写Verilog代码,再到v代码的仿真测试,最后以下板调试符合预期为结束。这一传统流程存在四大挑战:

01开发周期长

代码开发和仿真时间往往占据整个项目周期的一半以上。

02跨专业协作成本高

算法工程师与FPGA工程师需要频繁沟通,模型和代码不同步的情况屡见不鲜。

03出错率高

人工编码语法或时序错误会导致大量返工与重复测试。

04代码质量不稳定

人工编写的代码质量由工程师的水平决定,不同的工程师开发的代码质量参差不齐,代码风格不统一,不利于产品化。

对于追求快速原型验证和产品迭代的企业而言,这些问题无疑严重制约了效率和竞争力。

3 解决方案

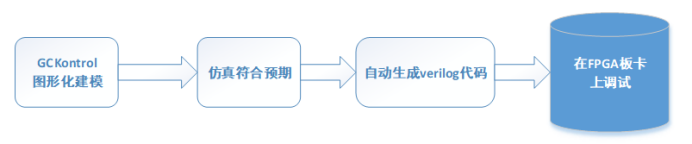

基于世冠科技GCKontrol平台,提供了一种可以自动生成Verilog代码的技术路线:工程师使用GCKontrol建模软件,进行图形化建模之后,经过一系列的操作,即可自动生成Verilog代码,从而跳过人工编写代码和仿真测试的环节,通过IDE软件将代码综合编译后,将bit文件下载到FPGA芯片板卡上,实现对FPGA设计流程的高效优化。

其方案框图如图1所示:

图 1 方案框图

接下来简单介绍下目前GCKontrol建模软件支持自动生成Verilog代码的基础模块。

3.1 支持自动生成Verilog的基础单元

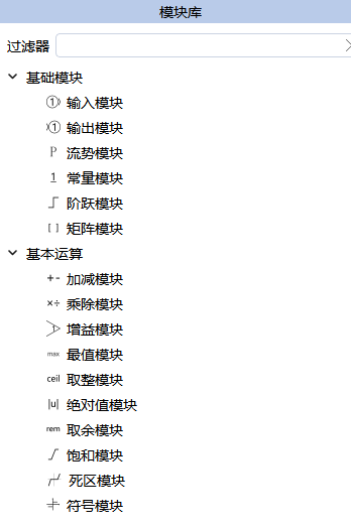

图 2 支持自动生成Verilog代码的基础模块

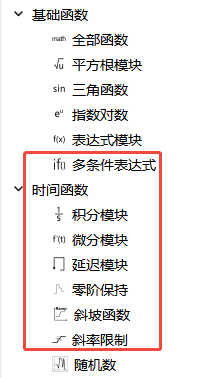

图 3 支持自动生成Verilog代码的模块

由图2和图3可知,目前支持自动生成Verilog代码的基础模块有输入输出模块,常量模块,加减模块,乘除模块,增益模块,最值模块,取整模块,绝对值模块,取余模块,饱和模块,死区模块,符号模块,积分模块,微分模块,延迟模块,位转换模块,多条件表达式模块,零阶保持,斜坡函数,斜率限制函数等。

这些都是算法模型搭建的必要单元,这些模块支持自动生成Verilog代码,为满足不同要求的算法模型的搭建提供了前提条件。目前还正在开发较为复杂的基础函数和各种信号发生器等模块,从而支持后续复杂度更高的模型搭建和下板验证。

3.2 包含基础运算模块的工程示例

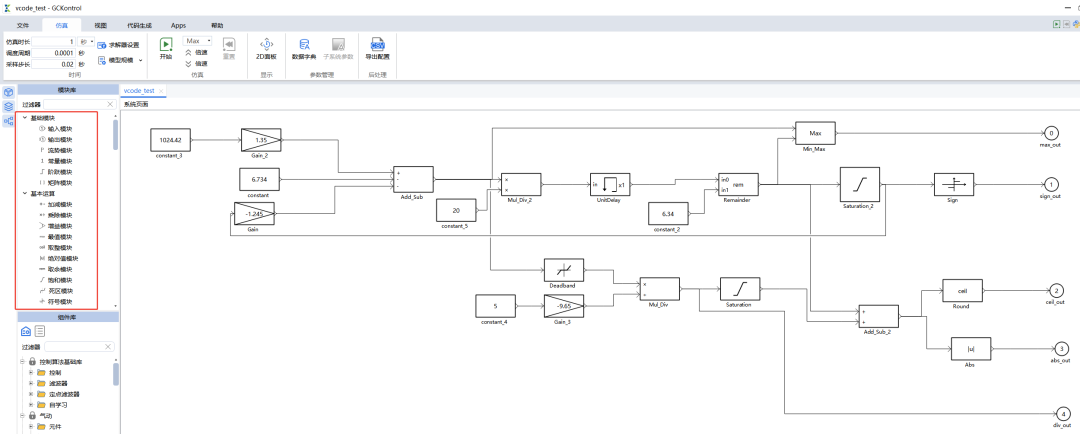

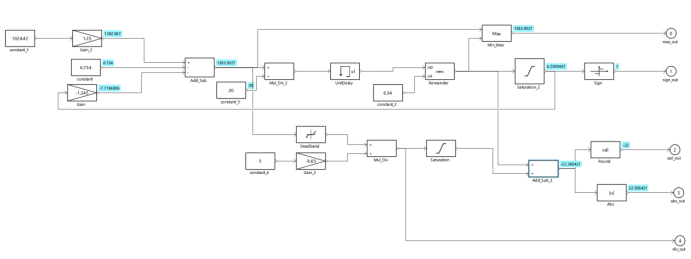

图 4 搭建包含基础运算模块的gck工程

如图4所示,可使用全部基本运算模块搭建一个gck工程。点击仿真后,如图5所示,用户可在界面上查看每个模块的结果,也可通过2D面板灵活添加数据,查看任意模块的仿真输出。

图 5 仿真结果显示

价值点

工程师能够在建模阶段快速验证算法逻辑,减少后期跨团队的沟通与调试成本。

3.3 自动生成Verilog代码

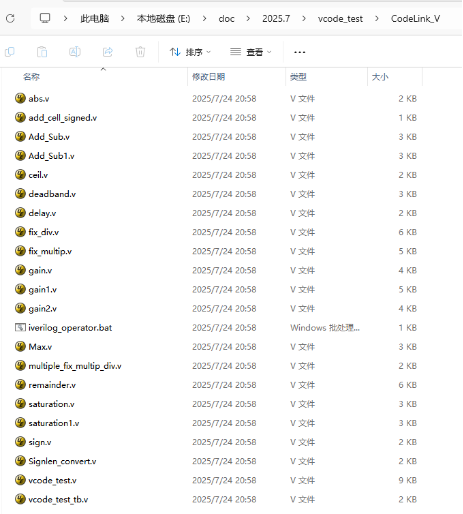

图 6 自动生成Verilog代码路径

由图6可知,在工程路径的CodeLink_v的文件夹下,可以看到自动生成Verilog代码的所有v文件。这些代码符合行业规范,支持综合编译成bit文件并下板调试。

价值点

·自动生成的Verilog代码与模型保持完全同步,杜绝“模型更新但代码未更新”的问题;

·避免人工编码语法错误和代码质量不稳定的情形,提高一次性验证成功率;

·直接可用的代码显著缩短下板调试周期。

3.4 附加功能——代码预览

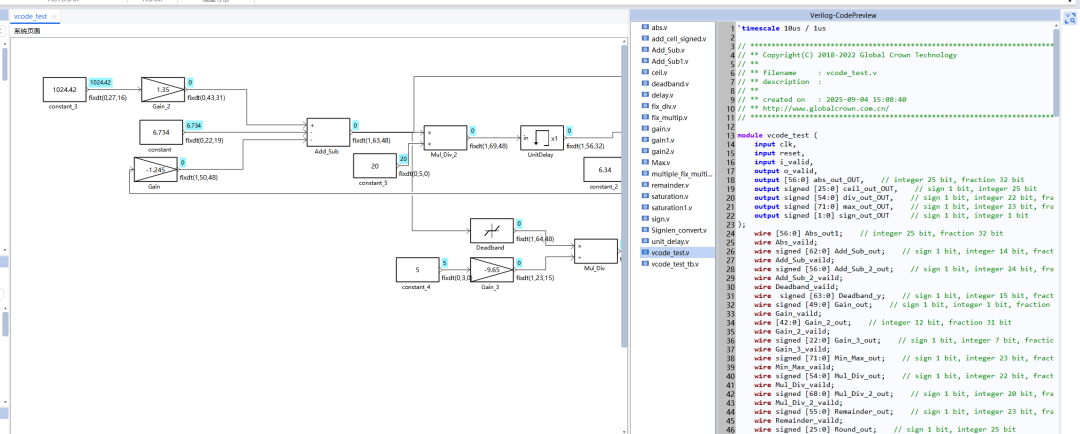

图 7 Verilog代码预览

由图7可知,GCKontrol软件自动生成Verilog代码后,支持在界面对生成的代码进行在线预览,方便在模型级随时查看自动生成的Verilog代码。

价值点

模型与代码实时对照,工程师在建模阶段即可检查逻辑,提前发现偏差,减少后期返工。

4 总结与展望

基于世冠科技GCKontrol平台,通过将图形化建模工程直接自动生成Verilog代码,大大缩短了项目开发周期,节省了人力成本,并保证了代码风格的稳定性和可靠性,极大的优化了FPGA的设计流程。

未来,GCKontrol将持续扩展模块库,支持通信、雷达、工业控制等更复杂的算法场景。助力更高效的FPGA设计开发,为复杂算法模型从理论到实践的一键转换提供更强有力的支持。