FPGA学习篇——Verilog学习MUX的实现

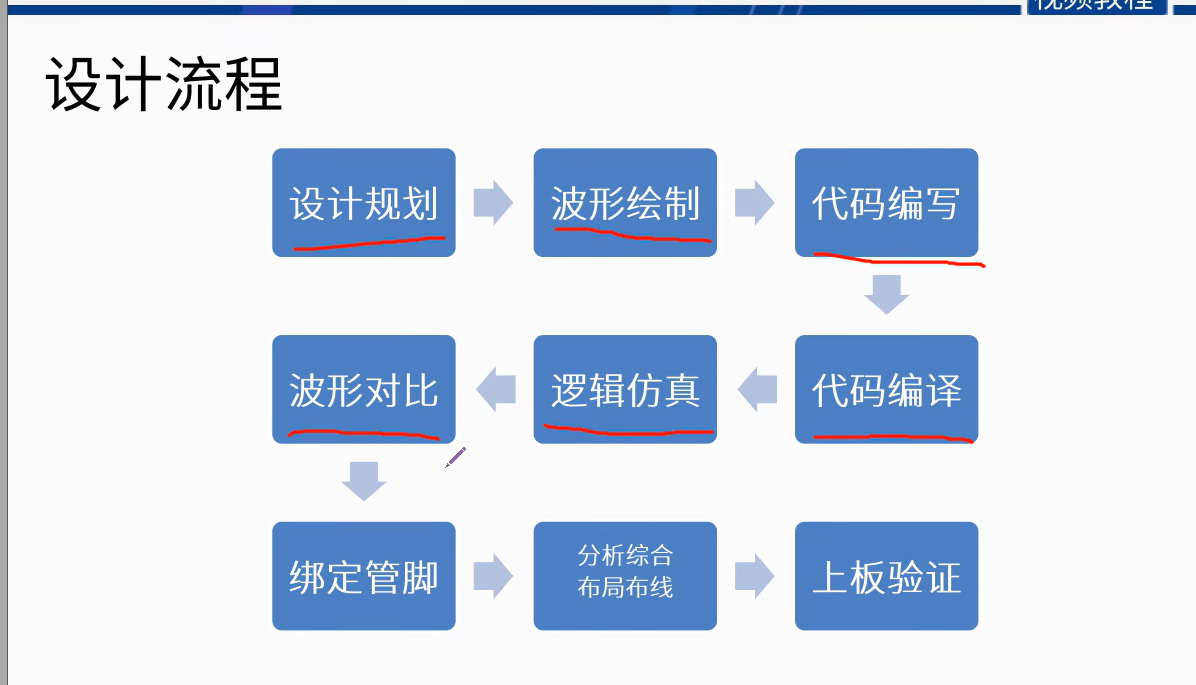

PS:目前手上仍然没有板子,按照野火视频的讲解,目前我们只能做到前面六步(其实第一步设计规划也是需要看板子的硬件的,但是现在没有板子就完全与野火传授的板子一致来看)

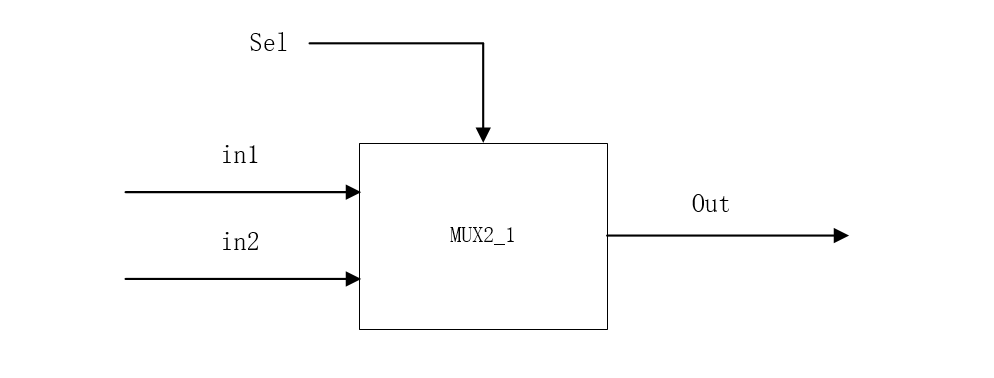

首先我们以最简单的2路选择器MUX2_1为例。

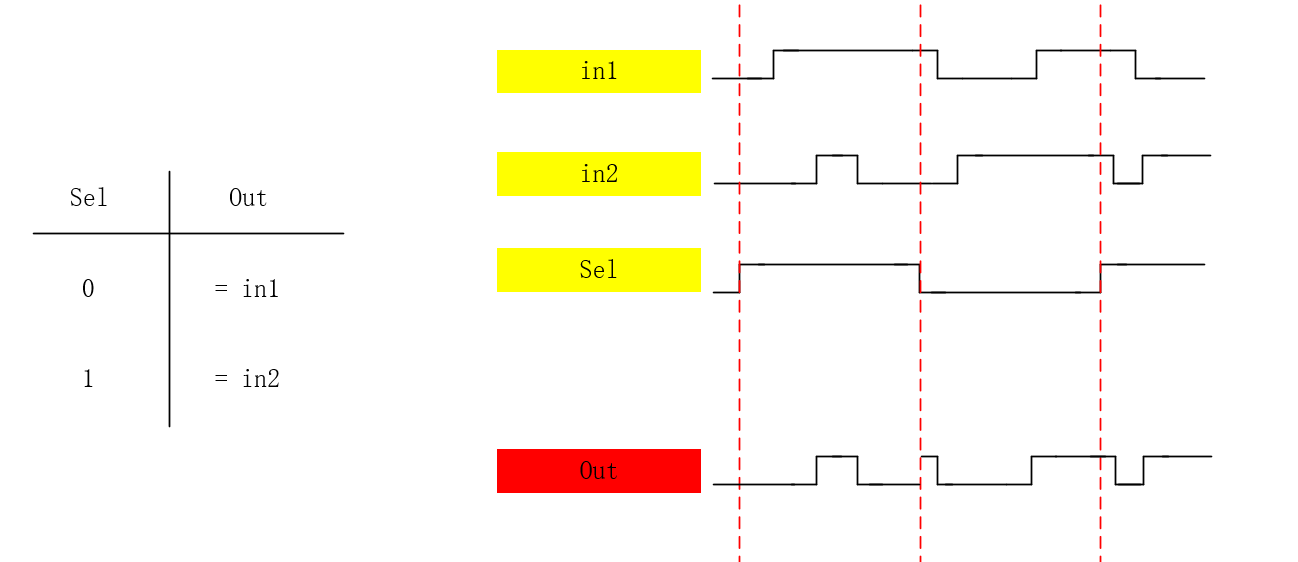

1 设计规划及波形绘制

设计规划:MUX的原理是根据sel的值选择对应输入连到输出。

对应的真值表及波形图绘制如下:

2 代码编写

rtl文件:(这里用always进行功能描述,故输入必须是reg型)

module MUX2_1

(input in1,in2,sel,output reg out);always@(*)if(sel == 1'b0)out = in1;elseout = in2;endmodule3 逻辑仿真及波形验证

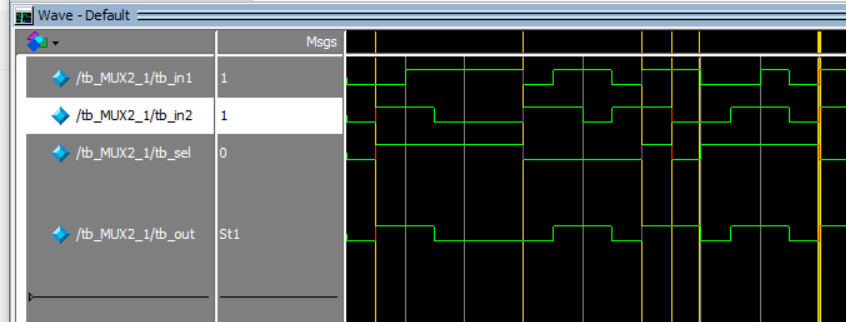

仿真文件编写如下:

`timescale 1ns/1nsmodule tb_MUX2_1();reg tb_in1,tb_in2,tb_sel;

wire tb_out;initial begintb_in1 <= 1'b0;tb_in2 <= 1'b0;tb_sel <= 1'b0; endalways #10 tb_in1 <= {$random} % 2;

always #10 tb_in2 <= {$random} % 2;

always #10 tb_sel <= {$random} % 2;MUX2_1 MUX2_1_inst

(.in1 (tb_in1),.in2 (tb_in2),.sel (tb_sel),.out (tb_out)

); endmodule

得到的仿真波形图如下(注意:1中画出的波形图是自己随意画的一个波形,而这里仿真文件是随机生成Sel,in1和in2的,所以这三个与1中画的输入就不同,输出也自然不同,但是依然可以看到,输出根据sel选择对应的输入,仿真通过。)

(本贴仅是个人经验,参考哔哩哔野火视频:05-第五讲-点亮你的LED灯_哔哩哔哩_bilibili。如有侵权请联系我~)