STM32F103C8T6通过SPI协议驱动74HC595数码管完全指南:从硬件原理到级联实现

STM32F103C8T6通过SPI协议驱动74HC595数码管完全指南:从硬件原理到级联实现

硬件原理与核心组件解析

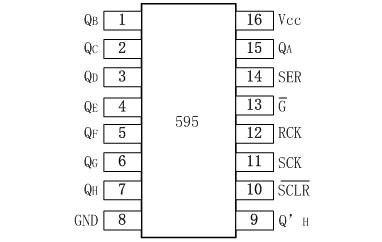

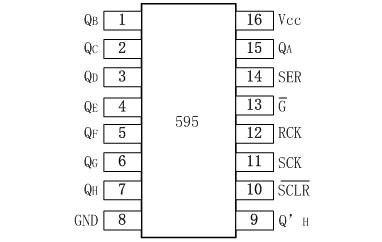

74HC595芯片功能与结构

74HC595是一款8位串行输入/并行输出移位寄存器,内置独立控制的移位寄存器与存储寄存器,具备三态输出功能,广泛应用于IO扩展场景(如数码管驱动、LED矩阵控制等)[1][2]。其核心优势在于通过串行数据输入实现并行输出,可显著减少主控芯片的IO占用,同时支持多片级联扩展以满足更多输出需求[3][4]。

一、内部结构与核心寄存器

芯片内部包含两个关键功能单元,采用独立时钟控制机制,确保数据移位与锁存过程解耦:

-

移位寄存器

8位串行输入寄存器,通过SHCP/SRCLK(移位时钟,11脚) 的上升沿触发数据移位。串行数据从DS/SER(14脚) 输入,每触发一次上升沿,数据在寄存器内整体左移一位,最早输入的高位数据最终从Q7S(9脚,级联输出端) 溢出,支持多片级联[2][5]。移位寄存器还支持通过MR/SCLR‾\overline{SCLR}SCLR(10脚,低电平有效) 异步复位,低电平时直接清零内部数据[6][7]。 -

存储寄存器

8位并行输出寄存器,通过STCP/RCLK(锁存时钟,12脚) 的上升沿将移位寄存器数据锁存至输出端。输出使能端OE/OE‾\overline{OE}OE(13脚,低电平有效) 控制输出状态:低电平时Q0-Q7(15脚及1-7脚)输出存储寄存器数据,高电平时呈高阻态(Z-state)[4][8]。

二、引脚配置与功能定义

74HC595采用16引脚双列直插(DIP)或表面贴装(SOIC/TSSOP)封装,顶视引脚分布如下表所示:

| 引脚号 | 符号 | 功能描述 | 典型连接方式 |

|---|---|---|---|

| 1-7,15 | Q0-Q7 | 8位并行数据输出端,直接驱动外部负载(如数码管段选/位选) | 接数码管引脚或LED驱动电路 |

| 8 | GND | 电源地 | 与主控系统共地 |

| 9 | Q7S/Q’H | 串行级联输出端,输出移位寄存器最高位数据,用于扩展级联 | 接下一级74HC595的DS引脚(14脚) |

| 10 | MR/SCLR‾\overline{SCLR}SCLR | 移位寄存器复位端(低电平有效),低电平时清零移位寄存器 | 接高电平(禁用复位)或主控复位引脚 |

| 11 | SHCP/SRCLK | 移位时钟输入端,上升沿时移位寄存器数据左移并接收SER引脚新数据 | 接STM32的SPI时钟引脚(如PA5) |

| 12 | STCP/RCLK | 锁存时钟输入端,上升沿时将移位寄存器数据锁存至存储寄存器并更新输出 | 接STM32的GPIO引脚(如PA4) |

| 13 | OE/OE‾\overline{OE}OE | 输出使能端(低电平有效),低电平时并行输出有效,高电平时输出高阻态 | 接地(始终使能输出)或接主控控制引脚 |

| 14 | DS/SER | 串行数据输入端,接收主控发送的串行数据位 | 接STM32的SPI数据输出引脚(如PA7) |

| 16 | VCC | 电源正极,工作电压范围2V~6V(推荐3.3V或5V) | 接系统电源(与主控逻辑电平匹配) |

注:引脚编号遵循顶视视角,左侧为1-8脚,右侧为9-16脚,芯片中央圆形标记为引脚1定位点[9][10]。

三、时序特性与工作机制

74HC595的核心工作流程遵循**“先移位后锁存”**原则,其关键时序参数与控制逻辑如下:

1. 移位时序(SRCLK控制)

- 数据输入:串行数据(SER)需在SRCLK上升沿前保持稳定,建立时间(tSU)≥20ns,上升沿后保持稳定保持时间(tH)≥20ns[11]。

- 移位方向:数据以高位(MSB)优先方式移入,例如连续输入

10110010,移位寄存器内数据序列为Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 = 1 0 1 1 0 0 1 0[3][12]。 - 时钟频率:SRCLK最小周期为42ns(约24MHz),确保高频数据传输能力[13]。

2. 锁存时序(RCLK控制)

- 锁存触发:RCLK上升沿将移位寄存器当前数据复制到存储寄存器,此时Q0-Q7输出更新。为避免数据错乱,需在8位数据完全移入后再触发RCLK[14]。

- 输出延迟:从RCLK上升沿到输出稳定的传输延迟(tpd)典型值为13ns,确保高速响应[1]。

关键时序约束:

- 移位阶段:SER数据需与SRCLK上升沿严格同步,避免亚稳态。

- 锁存阶段:RCLK脉冲应在SRCLK停止后产生,防止移位未完成时误锁存。

- 级联扩展:多片级联时,总移位时钟数=片数×8,锁存信号需同时作用于所有芯片。

四、功能真值表与核心特性

1. 功能真值表

| SRCLK | RCLK | SRCLR‾\overline{SRCLR}SRCLR | SER | 移位寄存器状态 | 存储寄存器状态 | Q0-Q7输出 |

|---|---|---|---|---|---|---|

| ↑ | X | H | D | 左移1位,SER输入D | 保持不变 | 保持不变 |

| X | ↑ | H | X | 保持不变 | 锁存移位寄存器数据 | 更新为存储寄存器数据 |

| X | X | L | X | 清零(全0) | 保持不变 | 保持不变 |

| X | X | H | X | 保持不变 | 保持不变 | 存储寄存器数据 |

注:“↑”表示上升沿,“X”表示任意状态,“H”为高电平,“L”为低电平[6][11]。

2. 核心电气特性

- 工作电压:2V~6V(兼容3.3V和5V逻辑系统)[2]。

- 输出能力:每路输出可驱动15个LSTTL负载,5V时输出电流达±6mA,支持直接驱动LED等外设[1][7]。

- 低功耗:静态供电电流最大80µA,待机功耗极低[15]。

- ESD保护:HBM(人体放电模式)>2000V,CDM(带电器件模式)>1000V,提高系统可靠性[16]。

通过上述结构与机制,74HC595实现了“串行数据输入-并行数据输出”的高效转换,为资源受限的微控制器(如STM32F103C8T6)提供了经济实用的IO扩展解决方案。

数码管显示原理与段码表

数码管结构与类型

数码管本质是由8颗LED(含7个显示段A-G和1个小数点段DP)按"8"字形排列组成的显示器件,根据公共电极连接方式分为共阴极和共阳极两种类型[17][18]。其核心区别在于点亮逻辑的差异:

共阴极数码管:公共端(COM)接GND,段选端(A-G、DP)输入高电平(逻辑1)时对应LED点亮

共阳极数码管:公共端(COM)接VCC,段选端(A-G、DP)输入低电平(逻辑0)时对应LED点亮

两种类型的段选信号逻辑完全相反,因此在实际应用中需根据硬件选型匹配对应的段码表。

共阴极数码管段码表(0-F)

段码表定义了显示字符与段选信号的映射关系,通过十六进制数值表示8段LED的开关状态(高电平为1,低电平为0)。共阴极数码管的标准段码表如下(含小数点段控制):

| 显示字符 | 段码(十六进制) | 二进制表示 | 段点亮状态 |

|---|---|---|---|

| 0 | 0x3F | 00111111 | A,B,C,D,E,F |

| 1 | 0x06 | 00000110 | B,C |

| 2 | 0x5B | 01011011 | A,B,G,E,D |

| 3 | 0x4F | 01001111 | A,B,G,C,D |

| 4 | 0x66 | 01100110 | F,G,B,C |

| 5 | 0x6D | 01101101 | A,F,G,C,D |

| 6 | 0x7D | 01111101 | A,F,G,C,D,E |

| 7 | 0x07 | 00000111 | A,B,C |

| 8 | 0x7F | 01111111 | A,B,C,D,E,F,G,DP |

| 9 | 0x6F | 01101111 | A,B,C,D,F,G |

| A | 0x77 | 01110111 | A,B,C,E,F,G |

| B | 0x7C | 01111100 | C,D,E,F,G |

| C | 0x39 | 00111001 | A,F,E,D |

| D | 0x5E | 01011110 | B,C,D,E,G |

| E | 0x79 | 01110101 | A,F,G,D,E |

| F | 0x71 | 01110001 | A,F,G,E |

| .(小数点) | 0x80 | 10000000 | DP |

在C语言中,可通过数组直接定义段码表以便快速调用:

unsigned char table_K[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};[17]。若需显示带小数点的字符(如"0."),只需将对应段码与0x80进行按位或运算(0x3F | 0x80 = 0xBF)[19]。

动态扫描显示原理

当需要显示多位数字时,静态显示(每位独立驱动)会占用大量I/O资源,因此实际应用中普遍采用动态扫描技术。其核心原理是基于人眼视觉暂留效应(视觉残留时间约100ms),通过分时复用段选线实现多位数显示[18][20]。

动态扫描三步骤:

- 位选通:通过位选信号选中当前待显示的数码管(共阴低电平有效,共阳高电平有效)

- 段码输出:向段选线发送当前位的段码数据

- 快速切换:延时1-2ms后关闭当前位,切换至下一位重复上述过程

为确保显示无闪烁,需满足刷新频率≥50Hz(即扫描周期≤20ms)。例如4位数码管需保证每位扫描时间≤5ms(20ms/4位),此时人眼会将快速切换的离散图像感知为连续显示[21]。对于更多位显示(如8位),可通过级联74HC595扩展段选/位选控制能力,进一步降低MCU的I/O占用[6]。

STM32 SPI引脚配置与硬件连接

引脚功能定义与映射关系

STM32F103C8T6与74HC595的SPI通信需明确三类引脚功能:SPI总线引脚负责数据传输与时钟同步,控制引脚管理锁存与复位逻辑,电源引脚保障电平匹配。具体映射关系如下表所示:

| SPI功能 | STM32引脚 | 74HC595引脚 | 硬件配置 | 作用说明 |

|---|---|---|---|---|

| 移位时钟 | PA5 | SRCLK(11) | 复用推挽输出 | 提供数据移位同步时钟 |

| 串行数据输出 | PA7 | SER(14) | 复用推挽输出 | 发送串行数据至移位寄存器 |

| 锁存控制 | PA4 | RCLK(12) | 通用推挽输出 | 控制移位寄存器数据锁存至输出 |

| 复位禁用 | - | /SRCLR(10) | 接3.3V | 禁用移位寄存器复位功能 |

| 输出使能 | - | /OE(13) | 接GND | 始终使能并行输出端 |

| 电源 | - | VCC(16) | 3.3V | 逻辑电平与STM32匹配 |

| 接地 | - | GND(8) | 共地连接 | 确保参考电平一致 |

其中SPI总线引脚(PA5、PA7)需配置为复用功能,而锁存控制引脚(PA4)作为普通GPIO使用,这是因为74HC595的锁存信号(RCLK)需独立于SPI时钟控制时序[5][22]。

电气参数配置与初始化

GPIO复用配置是实现SPI通信的核心。STM32F103C8T6的SPI1接口默认引脚(SCK=PA5、MOSI=PA7)需配置为复用推挽输出模式(GPIO_Mode_AF_PP),该模式允许引脚通过外设功能输出强驱动信号,同时支持50MHz高速率传输[23][24]。典型初始化代码需包含外设时钟使能与引脚模式设置:

// 使能SPI1与GPIOA时钟

RCC_APB2PeriphClockCmd(RCC_APB2Periph_SPI1 | RCC_APB2Periph_GPIOA, ENABLE);// 配置PA5(SCK)、PA7(MOSI)为复用推挽输出

GPIO_InitTypeDef GPIO_InitStruct;

GPIO_InitStruct.GPIO_Pin = GPIO_Pin_5 | GPIO_Pin_7;

GPIO_InitStruct.GPIO_Mode = GPIO_Mode_AF_PP; // 复用推挽输出

GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz; // 高速模式

GPIO_Init(GPIOA, &GPIO_InitStruct);// 配置PA4(RCLK)为通用推挽输出

GPIO_InitStruct.GPIO_Pin = GPIO_Pin_4;

GPIO_InitStruct.GPIO_Mode = GPIO_Mode_Out_PP; // 普通推挽输出

GPIO_Init(GPIOA, &GPIO_InitStruct);

关键配置说明:

- 复用功能选择:需确保PA5/PA7引脚复用映射至SPI1外设(通过AFIO寄存器配置,F103系列默认映射无需额外设置)[25]。

- 速度匹配:50MHz速率需与74HC595的最大移位时钟频率(典型值100MHz)匹配,预留裕量保障信号完整性[5]。

硬件连接示意图与关键设计要点

典型连接电路需遵循信号完整性与电平兼容原则,具体连接如下所示:

+3.3V│├─[10kΩ]─→ /SRCLR (10) // 禁用复位,下拉电阻防干扰│

STM32 │ 74HC595

PA7(MOSI)─┼─────────→ SER (14) // 串行数据输入

PA5(SCK) ├─────────→ SRCLK (11) // 移位时钟输入

PA4(GPIO) ├─────────→ RCLK (12) // 锁存控制信号

GND ├─────────→ /OE (13) // 始终使能输出│ │└─────────→ VCC (16) // 3.3V电源输入

GND └─────────→ GND (8) // 共地连接│

Q0-Q7 (1-7,15) ─────→ 数码管段选 // 并行数据输出

QH' (9) ───────────→ 下一级SER // 级联扩展端(未级联时悬空)

信号稳定性设计需注意以下两点:

- 上拉电阻的作用:在SDA(MOSI)与SCL(SCK)线上串联4.7kΩ上拉电阻,可抑制信号反射与噪声,尤其在布线长度超过10cm或多器件级联场景下效果显著[5]。

- 电源滤波:74HC595的VCC与GND间需并联100nF陶瓷电容,滤除电源纹波对移位寄存器的干扰,电容应靠近芯片引脚放置以缩短高频回路[3]。

连接禁忌:

- 禁止将/OE引脚悬空:悬空会导致输出端高阻态,数码管无显示;必须直接接地以确保输出使能[4]。

- 避免/SRCLR引脚接低电平:低电平会强制清空移位寄存器,导致数据传输失效,需通过10kΩ上拉电阻接3.3V保持禁用状态[7]。

实际硬件布局时,STM32与74HC595的PCB布线应遵循短路径、等长原则,SPI信号线长度差异控制在5mm以内,且远离电源噪声源(如DC-DC转换器),以减少电磁干扰对串行通信的影响。

SPI协议深度解析与配置

SPI时序逻辑与信号规范

信号定义与时序关系

SPI协议通过四条核心信号线实现通信:片选信号(CS/NSS)、串行时钟(SCK/SHCP)、主发从收数据(MOSI/DS) 和主收从发数据(MISO,驱动74HC595时可悬空)。典型SPI读写操作时序如图所示,其中CSN为低电平有效,呈现持续低电平脉冲以选中从设备;SCK为规则方波,控制数据传输节奏;MOSI则以高低电平脉冲形式传输二进制位数据[26]。

对于74HC595移位寄存器,其与SPI的时序配合需重点关注三个信号:

- 移位时钟(SHCP):采用占空比约50%的连续方波,数据在SHCP的上升沿被移入移位寄存器,因此需在下降沿更新数据以满足建立时间要求[8][12]。

- 数据信号(DS):在SHCP脉冲期间需保持稳定电平,单个数据位持续时间应长于SHCP周期,确保采样可靠[8]。

- 锁存时钟(STCP):在8位数据移位完成后产生上升沿,将移位寄存器数据锁存至输出端,与SHCP存在严格时序配合,两组脉冲间需有明显间隔[8]。

数据传输遵循高位优先(MSB) 原则,以发送数据10110010为例,其时序关系如下:

SI: __1___0___1___1___0___0___1___0____

SCK: _| |_| |_| |_| |_| |_| |_| |_↑ ↑ ↑ ↑ ...(共8个上升沿移位)

RCK: _____________________________|↑|____

[5]

关键时序参数与配置

74HC595的可靠工作依赖于严格的时序参数控制,主要包括:

- 建立时间(tSU):数据信号在SHCP上升沿前需保持稳定的最小时间,典型值为50ns;保持时间(tH):数据信号在SHCP上升沿后需保持稳定的最小时间,典型值为5ns[27]。

- 时钟频率:5V供电时SHCP最大频率为24MHz,实际应用中建议留有裕量,如STM32系统时钟72MHz下,通过SPI分频配置(如分频4)得到18MHz时钟,可确保稳定通信[1][12]。

STM32 SPI需配置为模式0(CPOL=0,CPHA=0) 以匹配74HC595时序:

- 时钟极性(CPOL):设为低电平(SPI_CPOL_Low),即SCK空闲时为低电平[24]。

- 时钟相位(CPHA):设为第一个边沿采样(SPI_CPHA_1Edge),即上升沿采样数据[24]。

不同SPI模式与74HC595的兼容性如下表所示:

| 模式 | CPOL | CPHA | 时钟空闲电平 | 数据采样沿 | 74HC595兼容性 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 低电平 | 上升沿 | 推荐 |

| 1 | 0 | 1 | 低电平 | 下降沿 | 不推荐 |

| 2 | 1 | 0 | 高电平 | 下降沿 | 需修改时序 |

| 3 | 1 | 1 | 高电平 | 上升沿 | 需修改时序 |

常见时序错误与波形对比

1. 时钟极性(CPOL)配置错误

若误将CPOL配置为高电平(模式2/3),SCK空闲时为高电平,导致74HC595在错误的边沿采样数据。正确时序中SCK空闲为低电平,上升沿稳定采样;错误时序中SCK空闲高电平,下降沿采样导致数据错位。

2. 数据建立时间不足

当SPI时钟频率过高(如超过24MHz)或数据更新延迟,会导致DS信号在SHCP上升沿前未稳定,表现为示波器波形中数据跳变与SHCP边沿重叠,造成移位寄存器接收错误数据。

调试建议:使用示波器同时监测SHCP和DS信号,确保数据在SHCP上升沿前至少稳定50ns。正确时序中DS波形应在SHCP脉冲间隔内保持平直,错误时序则会出现数据与时钟边沿交叉的"毛刺"现象。

3. 锁存时钟(STCP)时序错位

STCP若在数据未完全移位时产生上升沿,会导致部分数据未被锁存。正确操作应为8个SHCP脉冲后,STCP产生单个上升沿;错误时序中STCP脉冲与SHCP脉冲重叠,导致输出端数据不完整。

通过严格匹配SPI模式0配置、控制时钟频率在24MHz以内,并确保STCP与SHCP的时序配合,可有效避免上述错误,实现74HC595的稳定驱动。

STM32 SPI外设初始化配置

寄存器级配置实现

STM32 SPI外设的寄存器级初始化需完成时钟使能、GPIO配置及核心通信参数设置,具体步骤如下:

1. 时钟使能

SPI1外设挂载于APB2总线,初始化前需通过RCC_APB2ENR寄存器使能SPI1时钟及对应GPIO时钟。例如:

RCC->APB2ENR |= RCC_APB2ENR_SPI1EN; // 使能SPI1时钟

RCC->APB2ENR |= RCC_APB2ENR_IOPAEN; // 使能GPIOA时钟(假设使用GPIOA引脚)

APB2总线时钟频率通常为72 MHz(STM32F103系列),为SPI通信提供基础时钟源[28][29]。

2. GPIO引脚配置

SPI通信需配置SCK(时钟)、MOSI(数据输出)引脚为复用推挽输出模式,若使用软件控制片选(NSS),还需将RCK(锁存)引脚配置为通用推挽输出:

// 配置SCK(PA5)、MOSI(PA7)为复用推挽输出,速度50MHz

GPIOA->CRL &= ~(GPIO_CRL_MODE5 | GPIO_CRL_CNF5 | GPIO_CRL_MODE7 | GPIO_CRL_CNF7);

GPIOA->CRL |= (GPIO_CRL_MODE5_1 | GPIO_CRL_MODE5_0 | GPIO_CRL_CNF5_1 | GPIO_CRL_MODE7_1 | GPIO_CRL_MODE7_0 | GPIO_CRL_CNF7_1);

// 配置RCK(PA8)为通用推挽输出

GPIOA->CRH &= ~(GPIO_CRH_MODE8 | GPIO_CRH_CNF8);

GPIOA->CRH |= (GPIO_CRH_MODE8_1 | GPIO_CRH_MODE8_0 | GPIO_CRH_CNF8_0);

复用功能确保引脚信号由SPI外设直接驱动,提高通信稳定性[23][29]。

3. SPI核心参数配置

通过SPI_CR1寄存器配置通信参数,需与74HC595时序匹配(通常CPOL=0、CPHA=0):

- 波特率:BR[2:0]位设置分频系数,如

BR=000(2分频)时,SPI时钟频率为72 MHz/2=36 MHz; - 时钟极性/相位:

CPOL=0(空闲时SCL低电平),CPHA=0(第一个时钟边沿采样数据); - 数据格式:

DFF=0(8位数据帧),LSBFIRST=0(高位先行); - NSS管理:

SSM=1(软件控制)、SSI=1(内部NSS信号拉高); - 主模式使能:

MSTR=1(主设备模式),SPE=1(SPI外设使能)。

配置代码示例:

SPI1->CR1 = 0; // 复位CR1寄存器

SPI1->CR1 |= (0 << 3) | // BR[2:0]=000(2分频)(0 << 1) | // CPOL=0(空闲低电平)(0 << 0) | // CPHA=0(第一个边沿采样)(0 << 11) | // DFF=0(8位数据)(0 << 7) | // LSBFIRST=0(高位先行)(1 << 9) | // SSM=1(软件NSS)(1 << 8) | // SSI=1(内部NSS拉高)(1 << 2); // MSTR=1(主模式)

SPI1->CR1 |= (1 << 6); // SPE=1(使能SPI)

关键配置要点:74HC595的最大时钟频率通常为25 MHz(典型值),需确保SPI时钟不超过此限制。若系统时钟为72 MHz,推荐使用4分频(18 MHz)或8分频(9 MHz)以预留裕量[5][30]。

库函数实现对比

使用标准库或HAL库可简化初始化流程,核心参数与寄存器配置一一对应。

1. 标准库配置(SPI_InitTypeDef)

通过结构体统一配置参数,代码可读性更高:

SPI_InitTypeDef SPI_InitStructure;

SPI_InitStructure.SPI_Direction = SPI_Direction_2Lines_FullDuplex; // 双线全双工

SPI_InitStructure.SPI_Mode = SPI_Mode_Master; // 主设备模式

SPI_InitStructure.SPI_DataSize = SPI_DataSize_8b; // 8位数据帧

SPI_InitStructure.SPI_CPOL = SPI_CPOL_Low; // CPOL=0

SPI_InitStructure.SPI_CPHA = SPI_CPHA_1Edge; // CPHA=0(第一个边沿)

SPI_InitStructure.SPI_NSS = SPI_NSS_Soft; // 软件NSS

SPI_InitStructure.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_4; // 4分频(18 MHz)

SPI_InitStructure.SPI_FirstBit = SPI_FirstBit_MSB; // 高位先行

SPI_InitStructure.SPI_CRCPolynomial = 7; // CRC禁用时可忽略

SPI_Init(SPI1, &SPI_InitStructure);

SPI_Cmd(SPI1, ENABLE); // 使能SPI外设

```[[24](https://blog.csdn.net/weixin_58038206/article/details/145639242)][[31](https://bbs.21ic.com/icview-3379962-1-1.html)]**2. HAL库配置(MX_SPI1_Init)**

HAL库进一步封装底层操作,初始化函数自动完成时钟和GPIO配置:

```c

SPI_HandleTypeDef hspi1;

void MX_SPI1_Init(void) {hspi1.Instance = SPI1;hspi1.Init.Mode = SPI_MODE_MASTER;hspi1.Init.Direction = SPI_DIRECTION_1LINE_TX; // 仅发送模式(适配74HC595)hspi1.Init.DataSize = SPI_DATASIZE_8BIT;hspi1.Init.CLKPolarity = SPI_POLARITY_LOW; // CPOL=0hspi1.Init.CLKPhase = SPI_PHASE_1EDGE; // CPHA=0hspi1.Init.NSS = SPI_NSS_SOFT;hspi1.Init.BaudRatePrescaler = SPI_BAUDRATEPRESCALER_4; // 18 MHzhspi1.Init.FirstBit = SPI_FIRSTBIT_MSB;hspi1.Init.TIMode = SPI_TIMODE_DISABLE;hspi1.Init.CRCCalculation = SPI_CRCCALCULATION_DISABLE;HAL_SPI_Init(&hspi1); // 初始化外设及GPIO

}

```[[5](https://blog.csdn.net/fengidea/article/details/146426052)]#### 硬件SPI与软件模拟对比

| **特性** | **硬件SPI** | **软件模拟SPI** |

|----------------|-----------------------------------------|---------------------------------------|

| **传输速度** | 快(最高36 MHz@STM32F103) | 慢(受CPU指令周期限制,通常<1 MHz) |

| **CPU占用** | 低(硬件自动传输,支持DMA) | 高(需循环延时控制时序) |

| **引脚灵活性** | 固定(依赖SPI外设引脚) | 灵活(任意GPIO均可) |

| **配置复杂度** | 较高(需配置时钟、复用功能) | 低(直接操作GPIO寄存器) |

| **级联能力** | 强(高速传输支持多片级联) | 弱(速度受限,级联延迟明显) |**应用推荐**:驱动74HC595数码管时,硬件SPI是最优选择。尤其是级联多片(如8片以上)时,硬件SPI可通过18 MHz时钟实现微秒级数据更新,避免软件模拟导致的显示闪烁或延迟[[29](https://www.cnblogs.com/mangorange/articles/16308090)][[30](https://wenku.csdn.net/column/7tbftdrte6)]。软件模拟仅建议用于引脚资源紧张或低速场景(如单片片选控制)。### 数据传输格式与SPI通信流程#### 数据传输格式

SPI与74HC595的通信需采用**8位数据帧格式**,与74HC595内部8位移位寄存器的位数完全匹配,确保每次传输的数据能直接映射到并行输出端口[[5](https://blog.csdn.net/fengidea/article/details/146426052)][[23](https://blog.csdn.net/qinrenzhi/article/details/82154815)]。数据传输遵循**高位先行(MSB)** 原则,即每个字节的最高位(D7)首先通过MOSI线发送,这与74HC595的移位寄存器输入逻辑一致,需在STM32中配置`SPI_FirstBit_MSB`参数[[1](https://www.ti.com.cn/product/cn/SN74HC595)][[31](https://bbs.21ic.com/icview-3379962-1-1.html)]。 在级联应用中(如多片74HC595控制多位数码管),需采用**多字节传输模式**:每级联N片芯片,需连续发送N×8位数据,且高位字节对应前级芯片,低位字节对应后级芯片,确保数据在移位过程中依次传递到各级寄存器[[3](https://blog.csdn.net/dahuivolition/article/details/148748795)]。#### SPI通信流程

SPI与74HC595的通信流程可概括为**“发送数据→移位时钟→锁存时钟”** 三阶段,具体如下: 1. **选中从设备**:主设备(STM32)拉低SS(片选)引脚信号,选中74HC595从设备。由于74HC595无专用SS引脚,实际应用中可通过软件控制GPIO模拟片选逻辑[[31](https://bbs.21ic.com/icview-3379962-1-1.html)][[32](https://blog.csdn.net/fengidea/article/details/146718814)]。 2. **发送数据与移位**:主设备通过MOSI线发送8位数据,同时SPI外设自动生成SCK(移位时钟)信号。数据在SCK的**上升沿**被74HC595移位寄存器采样并逐位移入,8个时钟周期后完成1字节数据的移位[[5](https://blog.csdn.net/fengidea/article/details/146426052)][[33](https://blog.csdn.net/xianfajushi/article/details/112003216)]。 3. **锁存数据**:数据发送完成后,STM32控制RCK(锁存时钟)引脚产生**上升沿**,将移位寄存器中的数据锁存到存储寄存器,此时74HC595的Q0-Q7并行输出端口更新为新数据[[3](https://blog.csdn.net/dahuivolition/article/details/148748795)][[18](https://blog.51cto.com/u_13681435/10175584)]。 **关键流程总结**

1. 发送阶段:通过SPI外设发送8位数据,SCK自动生成8个时钟脉冲

2. 移位阶段:数据在SCK上升沿移入74HC595移位寄存器

3. 锁存阶段:RCK上升沿触发数据锁存,并行输出更新 #### 代码示例

以下为基于STM32 HAL库的SPI发送与锁存流程实现,以发送数据`0x55`(二进制`01010101`)为例: ```c

void SPI_SendTo595(uint8_t data) {// 1. 发送8位数据至移位寄存器HAL_SPI_Transmit(&hspi1, &data, 1, HAL_MAX_DELAY); // 通过SPI发送数据,SCK自动产生时钟// 2. 产生RCK上升沿锁存数据HAL_GPIO_WritePin(RCK_GPIO_Port, RCK_Pin, GPIO_PIN_SET); // RCK拉高HAL_Delay(1); // 延时确保锁存稳定HAL_GPIO_WritePin(RCK_GPIO_Port, RCK_Pin, GPIO_PIN_RESET); // RCK拉低复位

}

上述代码中,HAL_SPI_Transmit函数会自动处理SPI发送缓冲区状态(等待TXE标志)和传输完成判断(BSY标志清零),无需手动轮询[23][34]。

逻辑分析仪时序标注

理想的逻辑分析仪截图应包含以下关键信息(如图1所示):

- SPI传输序列:MOSI线上的8位数据(

0x55,即01010101),SCK线同步产生8个时钟脉冲,每个脉冲对应1位数据移位; - 锁存信号:RCK线在数据发送完成后产生一个清晰的上升沿;

- 74HC595输出:Q0-Q7端口在RCK上升沿后输出

01010101,对应数码管的段选信号状态。

通过时序图可直观观察到:数据在SCK上升沿被采样移位,RCK上升沿后移位寄存器数据被锁存至输出寄存器,实现并行数据更新[5][33]。

驱动代码实现与核心函数解析

SPI外设与GPIO初始化

STM32F103C8T6与74HC595的SPI通信接口初始化需严格遵循时钟使能-GPIO配置-SPI参数配置的流程,确保硬件接口时序与74HC595的电气特性匹配。以下从底层实现角度详细说明各步骤的原理与代码实现。

时钟使能

SPI外设与GPIO端口的时钟使能是初始化的首要步骤。由于SPI1挂载于APB2总线(最高频率72 MHz),而GPIOA同样由APB2总线控制,因此需通过RCC_APB2PeriphClockCmd函数同时使能两者的时钟:

RCC_APB2PeriphClockCmd(RCC_APB2Periph_SPI1 | RCC_APB2Periph_GPIOA, ENABLE);

该操作通过设置RCC寄存器的对应位,为SPI1外设和GPIOA端口提供工作时钟。若时钟未使能,后续的GPIO配置和SPI通信将无法正常工作[31]。

GPIO配置

SPI通信需使用特定功能引脚,其中SCK(串行时钟) 和MOSI(主输出从输入) 是控制74HC595的核心信号。对于SPI1,推荐使用PA5(SCK)和PA7(MOSI)引脚,配置为复用推挽输出模式(AF_PP),并设置50 MHz输出速度以满足高速通信需求:

GPIO_InitTypeDef GPIO_InitStructure;

// 配置SCK(PA5)和MOSI(PA7)为复用推挽输出

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_5 | GPIO_Pin_7;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; // 复用推挽输出(SPI功能)

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz; // 高速驱动能力

GPIO_Init(GPIOA, &GPIO_InitStructure);

复用推挽模式确保引脚能通过SPI外设控制信号输出,而50 MHz速度等级可满足SPI最高通信速率需求。若需控制74HC595的锁存信号(STCP),还需额外配置一个普通GPIO推挽输出引脚(如PA2),用于将移位寄存器数据锁存到输出寄存器[4][31]。

SPI参数配置

SPI参数需严格匹配74HC595的时序特性,关键配置包括通信模式、数据格式、时钟极性/相位及波特率。以下是基于标准库的SPI1初始化代码:

SPI_InitTypeDef SPI_InitStructure;

// SPI基础配置

SPI_InitStructure.SPI_Direction = SPI_Direction_1Line_Tx; // 单线发送模式(仅需MOSI)

SPI_InitStructure.SPI_Mode = SPI_Mode_Master; // 主设备模式

SPI_InitStructure.SPI_DataSize = SPI_DataSize_8b; // 8位数据帧格式

SPI_InitStructure.SPI_CPOL = SPI_CPOL_Low; // 时钟极性:空闲时低电平

SPI_InitStructure.SPI_CPHA = SPI_CPHA_1Edge; // 时钟相位:第一个边沿采样

SPI_InitStructure.SPI_NSS = SPI_NSS_Soft; // 软件控制NSS(无需硬件片选)

SPI_InitStructure.SPI_BaudRatePrescaler = SPI_BaudRatePrescaler_2; // 分频2(36 MHz)

SPI_InitStructure.SPI_FirstBit = SPI_FirstBit_MSB; // 高位先行(符合74HC595数据格式)

SPI_InitStructure.SPI_CRCPolynomial = 7; // CRC校验多项式(禁用CRC时无影响)

SPI_Init(SPI1, &SPI_InitStructure);

SPI_Cmd(SPI1, ENABLE); // 使能SPI1外设

参数匹配原理:

- CPOL=0与CPHA=1Edge:74HC595在SCK上升沿移位数据,此配置下SCK空闲时为低电平,第一个边沿(上升沿)触发数据移位,与芯片时序完全匹配[4]。

- 36 MHz波特率:APB2总线频率为72 MHz,分频2后SPI时钟为36 MHz,远低于74HC595的最大移位时钟频率(典型值100 MHz),确保数据传输稳定无失真。

- 单线发送模式:74HC595仅需接收数据(MOSI),无需MISO引脚,节省GPIO资源。

通过上述配置,STM32的SPI1外设可通过PA5(SCK)和PA7(MOSI)引脚与74HC595建立可靠通信,为后续数码管显示控制奠定硬件基础。实际应用中需注意,SPI发送完成后需通过锁存引脚(如PA2)产生上升沿,将移位寄存器数据锁存至输出寄存器,实现数码管显示更新[3]。

74HC595数据发送与锁存控制

74HC595的数据传输核心在于**“移位-锁存”双阶段控制**:通过移位时钟(SHCP/SRCLK)将串行数据逐位移入移位寄存器,再通过锁存时钟(STCP/RCLK)的上升沿将移位寄存器数据批量锁存至输出寄存器。这一过程需严格控制时序参数,确保数据建立时间与保持时间满足芯片要求(典型工作频率需匹配74HC595的时序参数)[35]。

单字节数据发送实现

单字节发送采用**“循环移位-时钟控制”结构**,通过8次循环完成1字节数据的逐位传输,关键在于移位时钟与数据位的同步。以下为GPIO模拟时序的典型实现:

void HC595_Out1Byte(uint8_t dat) {unsigned char i; HC595_LATCH_LOW(); // 拉低锁存信号(RCK),避免移位过程中误锁存Delay_us(1); // 确保信号稳定(>几十纳秒)for(i=0; i<8; i++) {HC595_SRCLK_LOW(); // 拉低移位时钟(SCK),准备数据输入Delay_us(1);// 根据当前最高位设置串行数据(SER)if(dat & 0x80) HC595_SER_HIGH(); // 最高位为1,SER置高else HC595_SER_LOW(); // 最高位为0,SER置低dat <<= 1; // 数据左移,准备下一位HC595_SRCLK_HIGH(); // SCK上升沿,数据移入移位寄存器Delay_us(1); }HC595_LATCH_HIGH(); // RCK上升沿,移位寄存器数据锁存至输出寄存器Delay_us(1); HC595_LATCH_LOW(); // 拉低锁存信号,等待下次操作

}

关键时序控制要点:

- 数据建立:SRCLK低电平期间修改SER数据,确保数据在上升沿前稳定

- 移位触发:SRCLK上升沿时,移位寄存器数据左移一位,新数据进入最低位

- 锁存时机:所有8位数据移位完成后,通过RCK上升沿一次性锁存

锁存控制的硬件实现

锁存控制通过RCLK引脚的电平跳变实现,核心是产生清晰的上升沿。STM32中可通过GPIO库函数直接操作引脚电平,典型代码如下:

void HC595_Latch(void) {GPIO_ResetBits(GPIOB, GPIO_Pin_12); // RCK拉低(准备阶段)Delay_Us(1); // 延时满足芯片最小低电平宽度要求GPIO_SetBits(GPIOB, GPIO_Pin_12); // RCK拉高(上升沿触发锁存)Delay_Us(1); // 保持高电平,确保锁存稳定

}

该操作会将移位寄存器中的8位数据并行输出至QA-QH引脚,同时OE引脚需保持低电平使能输出(高电平时输出为高阻态,可用于显示消隐)[8]。

单字节与多字节(级联)发送的核心差异

当多片74HC595级联时(如驱动多位数码管),数据发送逻辑需进行调整,核心区别在于锁存时机的控制:

| 发送模式 | 数据流向 | 锁存触发时机 | 典型应用 |

|---|---|---|---|

| 单字节发送 | 1字节→单个移位寄存器 | 每发送1字节后立即锁存 | 单数码管显示 |

| 多字节级联发送 | N字节→N个级联移位寄存器(前级QH’→后级SER) | 所有N字节发送完成后统一锁存 | 多位数码管、矩阵键盘 |

级联发送代码示例(以2片级联发送16位数据为例):

void HC595_SendData_2Chip(uint16_t data) {uint8_t byte_high = (data >> 8) & 0xFF; // 高位字节(第一片595)uint8_t byte_low = data & 0xFF; // 低位字节(第二片595)// 连续发送2字节,数据自动通过QH'级联传递HC595_OutByte(byte_high); // 先发高位,暂存于第一片移位寄存器HC595_OutByte(byte_low); // 再发低位,暂存于第二片移位寄存器HC595_Latch(); // 统一锁存,两片数据同时输出

}

级联关键注意事项:

- 禁止每发送1字节就触发锁存,否则前级数据会被后级移位操作覆盖

- 移位时钟(SRCLK)需保持连续,确保数据在级联链中正确传递

- 总数据位数=级联芯片数×8,需匹配发送字节数与芯片数量

通过上述控制逻辑,可实现对74HC595的高效驱动,既适用于单芯片简单场景,也可扩展至多芯片级联的复杂应用,为STM32F103C8T6控制多位数码管提供可靠解决方案。

数码管动态扫描与显示函数

数码管动态扫描技术基于人眼视觉暂留原理(视觉残留时间约100ms),通过快速循环选通多位数码管并更新显示内容,使肉眼感知为稳定的多位数字显示。其核心是控制每位数码管的显示时间与刷新频率:单数码管显示间隔需≤20ms(通常设置1~5ms),总刷新率需≥50Hz以避免闪烁。例如,4位数码管采用2ms间隔扫描时,总刷新率为1/(4×2ms)=125Hz,远高于50Hz的视觉临界值,可实现无闪烁显示[21][35]。

共阴极段码表定义

段码表是动态扫描的基础,用于将显示数字映射为数码管各段的驱动信号。共阴极数码管中,段选信号为低电平有效(即段码对应位为0时点亮该段),其段码表(0~9)定义如下:

// 共阴极段码表(0~9,DP段未启用)

uint8_t segCode[] = {0x3F, // 0:a+b+c+d+e+f(00111111)0x06, // 1:b+c(00000110)0x5B, // 2:a+b+g+e+d(01011011)0x4F, // 3:a+b+g+c+d(01001111)0x66, // 4:f+g+b+c(01100110)0x6D, // 5:a+f+g+c+d(01101101)0x7D, // 6:a+f+g+c+d+e(01111101)0x07, // 7:a+b+c(00000111)0x7F, // 8:全段点亮(01111111)0x6F // 9:a+b+c+d+f+g(01101111)

};

段码表中,索引值直接对应显示数字(如segCode[1]对应数字“1”的段码0x06),这种映射关系简化了数字到段码的转换过程[18][19]。

动态扫描函数实现

动态扫描函数通过“位选-段选-延时”的时序配合,实现多位数码管的循环刷新。以4位共阴极数码管为例(两片74HC595分别控制位选和段选),关键步骤如下:

动态扫描时序流程

- 消影处理:段选74HC595发送0x00,关闭所有段选信号,避免上一位残影干扰[36]。

- 位选控制:位选74HC595发送位选码(低电平选中),选通当前数码管(如0xfe选中第1位)。

- 段选更新:段选74HC595发送当前位对应的段码(从段码表读取)。

- 延时稳定:延时2ms确保段选信号稳定输出,再切换至下一位循环。

位选码表需与数码管位数匹配(4位示例),低电平有效:

// 4位数码管位选码表(低电平选中,从左至右0~3位)

uint8_t bitCode[] = {0xFE, 0xFD, 0xFB, 0xF7};

// 0xFE = 11111110(第0位低电平选中),0xFD=11111101(第1位选中),以此类推

基于上述逻辑,动态扫描函数实现如下:

// 通过74HC595发送段选数据(需提前实现SPI通信函数)

void HC595_SendData_Seg(uint8_t data) {// SPI发送段选数据至段选控制74HC595SPI_SendByte(data); HC595_Latch(); // 锁存信号触发,更新段选输出

}// 通过74HC595发送位选数据

void HC595_SendData_Bit(uint8_t data) {// SPI发送位选数据至位选控制74HC595SPI_SendByte(data); HC595_Latch(); // 锁存信号触发,更新位选输出

}// 在指定位置(0~3)显示数字(0~9)

void Display_Digit(uint8_t pos, uint8_t num) {if (pos >= 4 || num > 9) return; // 参数合法性检查HC595_SendData_Seg(0x00); // 消影:段选置0HC595_SendData_Bit(bitCode[pos]); // 位选:选中pos位HC595_SendData_Seg(segCode[num]); // 段选:显示num对应的段码HAL_Delay(2); // 延时2ms,确保人眼感知稳定

}

多位数字显示示例(以“1234”为例)

要显示“1234”,需将数字分解为个位、十位、百位、千位,通过循环调用扫描函数逐位显示。具体实现如下:

// 扫描显示4位数字(如1234)

void Display_Scan(uint16_t num) {uint8_t digits[4]; // 存储分解后的各位数字// 分解数字(假设num≤9999,不足4位高位补0)digits[0] = num / 1000; // 千位(1234→1)digits[1] = (num / 100) % 10; // 百位(1234→2)digits[2] = (num / 10) % 10; // 十位(1234→3)digits[3] = num % 10; // 个位(1234→4)// 循环扫描4位数码管for (uint8_t i = 0; i < 4; i++) {Display_Digit(i, digits[i]); // 第i位显示digits[i]}

}// 主函数调用示例

int main(void) {// 初始化SPI、74HC595、延时函数System_Init(); while (1) {Display_Scan(1234); // 持续扫描显示“1234”}

}

关键说明:

- 数字分解时,

digits[0]对应最高位(千位),digits[3]对应最低位(个位),与位选码表的顺序一致; - 每次循环调用

Display_Scan(1234)时,函数内部依次对4位数码管执行“消影-位选-段选-延时”流程,总耗时约8ms(4位×2ms),刷新率125Hz,满足无闪烁要求[20]。

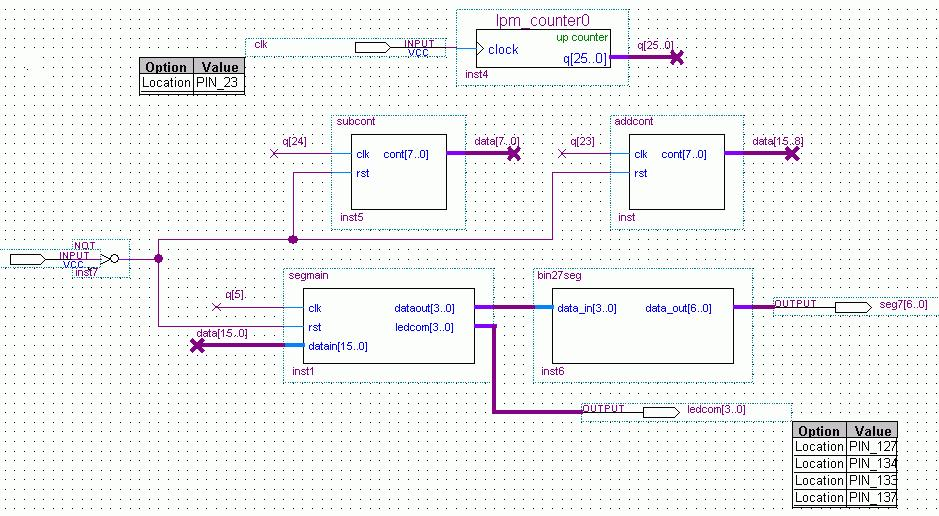

下图为数码管动态扫描控制模块的电路逻辑示意图,通过ledcom[3..0]信号选通不同数码管,配合段选数据实现动态显示:

通过上述设计,STM32F103C8T6可通过SPI驱动74HC595实现稳定的多位数码管动态显示,兼顾硬件资源优化与显示效果。

级联扩展与多片驱动实现

级联硬件连接与信号传输路径

单片与多片连接架构对比

在74HC595驱动数码管的硬件设计中,单片连接需重点关注三个核心信号引脚的连接逻辑:串行数据输入端(SER,14脚)连接STM32的SPI_MOSI引脚,移位时钟(SRCLK,11脚)与锁存时钟(RCLK,12脚)分别连接SPI_SCK与GPIO控制引脚,实现单芯片8位并行输出控制。而多片级联则通过扩展串行数据传输路径,在保留单片控制逻辑基础上,增加芯片间的数据级联通道,从而实现更多并行端口扩展。

多片级联硬件连接规范

级联核心路径依赖74HC595的串行数据溢出机制实现。芯片的9脚(QH’)为级联串行数据输出端,在扩展时需将前一级芯片的QH’引脚直接连接至后一级芯片的SER引脚(14脚),形成“数据链”结构。以两片级联为例,具体连接步骤如下:

级联连接三步骤

- 数据级联:第一片74HC595的QH’(9脚)→ 第二片的SER(14脚),实现数据串行传递

- 时钟同步:所有芯片的SRCLK(11脚)与RCLK(12脚)并联,由STM32同一组SPI时钟和锁存信号控制

- 电源共地:各芯片VCC(16脚)接+5V,GND(8脚)共地,确保逻辑电平一致性

典型应用场景中,多片级联可分别控制数码管的段选与位选信号。例如2片74HC595级联时,一片负责8位段选信号输出,另一片控制8位位选信号,配合4位七段数码管模块(如LED2、LED3)可实现8位数码管动态扫描显示,形成多模块连接架构[37].

信号传输路径与时序特性

级联系统的信号传输遵循“移位-溢出-锁存”机制:STM32通过SPI发送的串行数据首先进入第一片74HC595的移位寄存器,当发送数据位数超过8位时,超出的高位数据从QH’引脚溢出,作为第二片的SER输入。所有数据发送完成后,RCLK上升沿将各级移位寄存器中的数据同时锁存至存储寄存器,实现并行输出同步更新[3]. 这种机制要求严格的时序同步,因此所有级联芯片必须共享SRCLK和RCLK信号,确保数据移位与锁存操作的一致性[38].

电源与信号完整性设计要点

电源系统需满足多片工作电流需求,74HC595每片最大工作电流为80mA,级联时总电流按芯片数量累加;建议在VCC与GND之间并联100nF陶瓷电容,滤除电源线上的高频噪声,避免电压波动影响数据稳定性。

信号完整性方面,级联线路长度应控制在10cm以内,过长线路会引入传输延迟和高频干扰,导致数据错位。在PCB布局时,QH’至SER的级联路径应尽量短且走直线,避免与SPI时钟线平行布线,减少串扰影响。

关键设计约束

- 级联线路长度 ≤ 10cm,高频场景下建议缩短至5cm以内

- 每片74HC595最大电流80mA,总电流 = 芯片数量 × 80mA

- 必须使用独立100nF电容进行电源去耦,电容靠近芯片VCC引脚摆放

级联数据分发与发送逻辑

级联数据分发的核心在于通过串行移位实现多片74HC595的数据传递,并通过统一锁存确保同步更新。以2片级联发送16位数据0x1234为例,其数据流向与移位逻辑可拆解为三个关键阶段:数据顺序发送、移位寄存器级联传递、统一锁存输出。

数据发送顺序与移位过程解析

当2片74HC595级联时(记为U1和U2,U2为末级芯片,U1为首级芯片),需按**“末级优先”**原则发送数据。具体过程如下:

- 发送高位字节0x12至U2:主设备通过SPI发送8位数据0x12(二进制11001000),每发送1位,SHCP产生1个上升沿脉冲,数据逐位移入U1的移位寄存器。当第8位发送完成后,U1移位寄存器溢出的数据从Q7’引脚输出,恰好填满U2的移位寄存器,此时U2寄存器状态为0x12[38][39]。

- 发送低位字节0x34至U1:继续发送8位数据0x34(二进制00110100),同样通过SHCP脉冲移位。此时U1的移位寄存器接收新数据,而U2的寄存器数据保持不变。发送完成后,U1寄存器状态为0x34[6][7]。

- 统一锁存:16位数据(2字节)发送完毕后,RCLK产生上升沿,U1和U2的移位寄存器数据同时锁存至输出寄存器,实现并行输出更新[3][39]。

此过程体现了**“先发送的数据填充末级芯片”**的级联逻辑:由于数据通过Q7’引脚逐片传递,先发的高位字节会被后发的低位字节“推”入末级芯片,而低位字节则保留在首级芯片中[7][12]。

级联发送代码实现

针对N片级联场景,需设计支持多字节发送的通用函数HC595_SendNBytes,其核心逻辑为**“循环发送N字节数据→统一触发锁存”**,其中N等于级联芯片数量。以下为基于STM32 HAL库的实现示例:

/*** @brief 向N片级联的74HC595发送数据* @param pData:待发送数据缓冲区(首地址为末级芯片数据)* @param N:级联芯片数量(发送字节数=N)* @note 数据发送顺序:先发送末级芯片数据,再依次发送首级芯片数据*/

void HC595_SendNBytes(uint8_t *pData, uint8_t N) {// 循环发送N字节数据(每字节对应1片芯片)for (uint8_t i = 0; i < N; i++) {// 通过SPI发送1字节数据,高位先行HAL_SPI_Transmit(&hspi1, &pData[i], 1, HAL_MAX_DELAY);}// 所有数据发送完成后,统一产生RCLK上升沿锁存HAL_GPIO_WritePin(GPIOA, GPIO_PIN_8, GPIO_PIN_SET); // RCLK置高HAL_Delay(1); // 延时确保信号稳定HAL_GPIO_WritePin(GPIOA, GPIO_PIN_8, GPIO_PIN_RESET); // RCLK置低

}// 示例:2片级联发送0x1234(U2=0x12,U1=0x34)

uint8_t cascadeData[2] = {0x12, 0x34}; // 缓冲区首元素为末级芯片数据

HC595_SendNBytes(cascadeData, 2); // N=2(级联数量)

关键逻辑总结

级联数据发送三原则

- 数据顺序:按“末级→首级”顺序发送,N片级联需发送N字节,首字节对应末级芯片[6][39]。

- 移位传递:通过Q7’引脚实现数据级联,先发数据自动填充后续芯片移位寄存器[7]。

- 统一锁存:所有数据发送完毕后触发RCLK上升沿,确保多片数据同步更新[3]。

通过上述逻辑,可实现任意数量74HC595的级联控制,例如3片级联时,只需将N设为3,发送3字节数据(依次对应第3、2、1片芯片),即可驱动24位并行输出[7][35]。

多数码管显示控制与地址映射

多数码管显示系统通常由多个七段数码管构成,通过级联74HC595实现扩展控制。典型应用中采用“段选芯片+位选芯片”的架构:段选芯片(如U1)负责输出段码信号(控制a-g段及小数点dp),位选芯片(如U2)负责输出位选信号(控制数码管的公共端,实现地址映射)。例如,由两个四位七段数码管组成的8位显示系统,可通过级联两片74HC595分别作为段选和位选控制,实现多位数的动态扫描显示[40].

地址映射机制

地址映射是实现多数码管独立显示的核心,其本质是通过位选信号与显示位置的一一对应建立逻辑地址与物理硬件的关联。具体实现方式包括:

- 位选码表定义:通过数组存储位选信号与显示位置的映射关系,如

display_pos[0] = 0x01表示第0位数码管对应位选信号0x01(二进制0000 0001),display_pos[1] = 0x02对应第1位,以此类推。位选码通过位选74HC595输出,控制特定数码管的选通[35]. - 段选码表定义:预先定义数字0~9的段码值(如共阴极数码管中数字“1”的段码为0x06,对应b、c段点亮),段码通过段选74HC595输出至所有数码管的段引脚[35].

- 显示缓冲区划分:对于大规模显示(如24位),可采用“段选分组+位选分组”策略,将显示缓冲区按组划分(如3位一组),每组对应多片段选74HC595的并行数据,位选信号按组选通实现批量控制[6].

实际硬件中,位选信号通常标注为“DS5~DS8”等引脚(如LED2模块的位选控制),通过这些引脚的高低电平变化实现数码管的地址索引[37].

动态扫描控制逻辑

多数码管显示采用分时复用的动态扫描技术,核心逻辑为“位选信号分时使能,段码同步发送”。以8位数码管显示“12345678”为例,具体流程如下:

动态扫描步骤

- 初始化:定义段码表

seg_code[] = {0x06, 0x5B, 0x4F, 0x66, 0x6D, 0x7D, 0x07, 0x7F}(对应数字1~8的段码),位选码表bit_code[] = {0x01, 0x02, 0x04, 0x08, 0x10, 0x20, 0x40, 0x80}(对应位0~位7)。 - 循环扫描:遍历0~7位,每次循环执行:

- 发送当前位选码(如位0发送0x01,选通第1个数码管);

- 同步发送对应段码(如数字“1”的段码0x06);

- 延时1~2ms(确保人眼视觉暂留)后关闭当前位选,切换至下一位。

- 频率控制:扫描频率需大于50Hz(每位移位时间<20ms),避免显示闪烁[36].

通过上述逻辑,系统可实现8位数码管的并行显示。例如,级联两片74HC595后,位选芯片分时输出0x010x80,段选芯片同步发送18的段码,最终使数码管依次显示“1”“2”…“8”,视觉上形成稳定的多位数显示效果[41].

扩展应用与注意事项

当需要控制更多位数(如24位)时,可采用“多片段选+分组位选”架构:使用3片74HC595作为段选控制(每片控制8位段码),n条位选线控制n组数码管,每次扫描一组3位,循环刷新所有组。此时地址映射需按组划分显示缓冲区,确保段选数据与位选分组的同步性[6]. 此外,位选信号需通过上拉电阻增强驱动能力,避免因负载过大导致选通失效。

通过“段选与位选分离+动态扫描”的设计,多数码管系统可在较少IO资源下实现高效控制,兼顾显示稳定性与硬件成本。

调试优化与常见问题解决方案

SPI通信故障诊断与排除

SPI 通信故障的诊断需遵循“硬件-软件-时序”三维排查框架,结合设备特性与信号测量进行系统定位。以下从具体故障表现入手,详解各维度排查要点及解决方案。

一、硬件连接故障排查

硬件层问题常导致通信完全中断或输出异常,需重点检查物理连接与电气特性:

-

电源与供电稳定性

无输出或输出紊乱时,首先验证 74HC595 的 VCC(3.3V)与 GND 连接是否牢固,建议在 VCC 与 GND 间并联 100nF 陶瓷滤波电容以抑制电源噪声[5]。若出现输出高阻态,需确认 OE/G 引脚(13 脚)是否可靠接地,该引脚拉高会使芯片进入高阻模式,必须拉低才能使能并行输出[3][39]。 -

信号线连接正确性

输出乱码或数据错位可能源于 SPI 引脚接反:需核对 STM32 的 SCK(时钟线)是否连接 74HC595 的 SRCLK(11 脚),MOSI(数据线)是否连接 SER(14 脚),避免两者混淆[5]。同时检查线路是否存在虚焊、短路,可通过万用表导通档测试或示波器观察信号波形是否畸变。

二、软件配置故障排查

软件参数配置直接影响通信逻辑,需确保主从设备参数匹配及控制流程正确:

-

SPI 工作模式匹配

74HC595 为同步移位寄存器,要求 SPI 工作于 模式 0(CPOL=0,CPHA=0),即空闲时 SCK 为低电平,数据在 SCK 上升沿被采样。若配置为其他模式(如 CPHA=1),会导致数据采样相位错位,出现“发送 A 却显示 B”的乱码现象[30][35]。需通过查阅芯片数据手册时序图,在 STM32 初始化代码中明确设置:SPI_InitStruct.SPI_CPOL = SPI_CPOL_Low; // 空闲时钟低电平 SPI_InitStruct.SPI_CPHA = SPI_CPHA_1Edge; // 第一个时钟沿采样 -

波特率与数据传输控制

SCK 频率过高会导致 74HC595 移位寄存器无法稳定锁存数据,其最大支持 24 MHz,但实际应用中推荐降至 18 MHz 以下以预留裕量[30]。若通信不稳定,可通过调整 STM32 的 SPI 分频系数降低速率(如从SPI_BAUDRATEPRESCALER_2改为_4)。此外,数据发送需严格遵循“先移位后锁存”逻辑:确保所有 8 位数据通过 MOSI 发送完成后,再通过 RCLK(12 脚)产生上升沿锁存,且 RCLK 高低电平切换需保留至少 1 us 延时,避免锁存失败[3]。

三、时序特性故障排查

时序是 SPI 通信的核心,需通过仪器测量验证信号完整性:

- 关键时序参数验证

使用示波器监测以下信号:- SCK 频率:实测频率需 ≤ 24 MHz,推荐 18 MHz 以下,可通过测量相邻两个上升沿的时间间隔计算(如 18 MHz 对应周期约 55.5 ns)。

- 数据建立时间(tSU):确保 MOSI 数据在 SCK 上升沿前至少稳定 20 ns,若建立时间不足,需优化软件延时或降低通信速率。

- RCLK 触发时机:观察 RCLK 上升沿是否在最后一位数据发送完毕后产生,若提前触发会导致部分数据未移入寄存器。

时序排查关键步骤

- 用示波器通道 1 测 SCK(黄线),通道 2 测 MOSI(蓝线),确认数据在 SCK 上升沿稳定。

- 通道 3 测 RCLK(绿线),验证其上升沿滞后于 SCK 最后一个下降沿至少 1 us。

- 若波形畸变,检查信号线长度(建议 ≤ 20 cm)及是否远离强干扰源(如电机、电源模块)。

四、故障排查流程图解

按以下步骤逐步定位问题,可覆盖 90% 以上 SPI 通信故障:

-

电源检查

- 测量 74HC595 的 VCC 电压(3.3V ± 0.3V),GND 是否与 STM32 共地。

- 检查/OE 引脚电平(需为低电平),可临时直接接地测试排除该引脚故障。

-

接线验证

- 核对 SCK → SRCLK、MOSI → SER、GPIO → RCLK 的对应关系,用逻辑笔测试各引脚是否有信号输出。

-

配置核对

- 复查 STM32 的 CPOL/CPHA 设置(必须为 0,0),波特率分频系数是否合理。

- 检查发送函数是否等待

TXE标志(发送缓冲区空)后再写入数据,避免数据覆盖。

-

时序测量

- 若上述步骤正常,使用示波器观察 SCK 频率、占空比及 RCLK 触发时序,必要时更换短线或降低速率测试。

通过“硬件-软件-时序”三维验证,可系统性定位 SPI 通信故障,尤其需注意 74HC595 作为从设备的被动特性——其无反馈机制,需通过输出状态反推内部逻辑,结合仪器测量提升排查效率。

显示异常与闪烁问题优化

在 STM32F103C8T6 通过 SPI 驱动 74HC595 数码管的应用中,显示异常与闪烁是常见问题,其核心原因包括动态扫描频率不足、信号同步偏差及硬件参数配置不当。以下从闪烁优化、亮度均匀性调整及段码表错误调试三个维度提出系统性解决方案。

闪烁问题的成因与优化策略

闪烁本质是由于人眼对低于 50Hz 的刷新频率产生视觉残留效应。实验数据表明,当动态扫描频率≥50Hz 时,人眼无法察觉画面切换,从而消除闪烁感[21][42]。具体优化措施如下:

-

提高扫描频率:通过缩短单位移位时间实现。例如,8 位数码管每位移位间隔控制在 1ms 时,总刷新频率为 1/(8×1ms) = 125Hz,远高于 50Hz 阈值;4 位数码管单步延时 1ms 时,总频率可达 250Hz[21][36]。需注意:单步延时建议控制在 1~5ms 范围内,过短可能导致亮度下降,过长则无法满足频率要求[36]。

-

信号同步与消影处理:闪烁也可能由位选与段选信号不同步导致,例如前一位数码管的段选信号未关闭时切换位选,会产生残影。解决方案是在切换位选前将段选信号置 0(即关闭所有段),待位选稳定后再更新段选数据[36]。

-

代码执行效率优化:传统延时函数(如

delay_ms())会阻塞主程序,导致扫描间隔不稳定。建议采用定时器中断(如 SysTick 或 TIM 定时器)触发扫描,确保扫描周期精确可控。例如,配置 SysTick 每 1ms 中断一次,在中断服务函数中完成一位数码管的刷新,既避免阻塞又保证频率稳定[36]。 -

OE 引脚的高效控制:74HC595 的 OE 引脚(输出使能)可通过 GPIO 直接控制:高电平熄灭所有数码管,低电平点亮。相比通过 SPI 发送全零数据实现熄灭,OE 引脚控制响应更快,适用于整体闪烁警示或紧急熄灭场景[4]。

关键优化公式:动态扫描总频率 = 1/(数码管位数 × 单步延时)。例如:

- 8 位数码管 + 1ms 单步延时 → 125Hz(满足≥50Hz)

- 4 位数码管 + 5ms 单步延时 → 50Hz(临界值,建议缩短至 1~2ms 提升稳定性)

亮度不均匀问题的硬件优化

亮度不均匀主要源于各数码管支路电流差异,解决核心是通过限流电阻稳定每段电流。建议在每位数码管的公共端(位选引脚)串联 220Ω 限流电阻,使段电流控制在 10~20mA 范围内(需根据数码管手册调整,通常正向压降约 1.8V,STM32 GPIO 输出高电平约 3.3V,电流 I=(3.3V-1.8V)/220Ω≈6.8mA,可根据需求调整电阻值)。不同电流下的亮度特性对比见表 1。

表 1:不同段电流对应的亮度与功耗特性

| 段电流 | 亮度描述 | 功耗(单段) | 适用场景 |

|---|---|---|---|

| 10mA | 适中,柔和不刺眼 | 约 18mW | 长时间静态显示(如仪表盘) |

| 20mA | 较高,视觉突出 | 约 36mW | 动态扫描或强光环境 |

注:功耗计算公式为 P=U×I,其中 U 为数码管段压降(典型 1.8V),I 为段电流。

段码表错误导致显示乱码的调试方法

段码表错误是显示乱码的主要原因,表现为数字/字符显示残缺或错误。调试步骤如下:

-

确认数码管类型与段码表匹配:共阴数码管与共阳数码管的段码表完全相反。例如,共阴数码管显示“0”的段码为 0x3F(二进制 00111111,对应 a~g 段亮),共阳则为 0xC0(11000000)。若类型混淆,会导致所有段显示错误[35]。

-

逻辑分析仪抓取实际段选数据:使用逻辑分析仪连接 74HC595 的 QA~QH 引脚(段选输出),触发 SPI 发送指令,记录段选信号的二进制值。例如,若预期显示“1”(共阴段码 0x06),实际抓取到 0x0E,则说明段 b 和 c 未点亮(二进制 00001110 对应 b、c、d 段亮),可能是段码表定义错误(如误写为 0x0E)或硬件接线交叉(如段 d 与段 b 引脚接反)。

-

标准段码表比对:以共阴数码管为例,标准段码表(0~F)见表 2。将抓取的段码与标准值逐位对比,差异位对应的段即为故障点。

表 2:共阴数码管标准段码表(0~F)

| 字符 | 段码(十六进制) | 二进制(a~g, dp) | 字符 | 段码(十六进制) | 二进制(a~g, dp) |

|---|---|---|---|---|---|

| 0 | 0x3F | 00111111 | 8 | 0x7F | 01111111 |

| 1 | 0x06 | 00000110 | 9 | 0x6F | 01101111 |

| 2 | 0x5B | 01011011 | A | 0x77 | 01110111 |

| 3 | 0x4F | 01001111 | B | 0x7C | 01111100 |

| 4 | 0x66 | 01100110 | C | 0x39 | 00111001 |

| 5 | 0x6D | 01101101 | D | 0x5E | 01011110 |

| 6 | 0x7D | 01111101 | E | 0x79 | 01111001 |

| 7 | 0x07 | 00000111 | F | 0x71 | 01110001 |

注:段定义(a~g 为数码管段,dp 为小数点):bit0=a, bit1=b, bit2=c, bit3=d, bit4=e, bit5=f, bit6=g, bit7=dp。

通过上述步骤,可快速定位段码表错误(如十六进制值写错、位序颠倒)或硬件接线问题,解决显示乱码现象。

信号干扰与系统稳定性提升

在 STM32F103C8T6 通过 SPI 协议驱动 74HC595 数码管的系统中,信号干扰与稳定性问题主要源于 SPI 时钟噪声、电源纹波及长线传输衰减等因素[5]。以下从硬件设计优化、软件可靠性增强及特殊场景处理三方面提出系统性解决方案,确保数据传输准确性与长期运行稳定性。

硬件设计优化策略

电源系统抗干扰设计是抑制噪声的基础。74HC595 工作电压范围为 2 V ~ 6 V,需在初始化阶段确认电源电压处于此区间,避免过压损坏芯片[11]。电源滤波采用 100 nF 陶瓷电容与 10 μF 电解电容并联的组合方案:陶瓷电容靠近芯片 VCC 引脚,用于滤除高频纹波;电解电容则负责吸收低频噪声,两者协同实现宽频带滤波[5][30]。

PCB 布线与信号完整性需重点关注 SPI 通信链路。信号线长度应控制在 10 cm 以内,避免平行布线以减少串扰;时钟线(SCK)与数据线(MOSI)建议走差分线或短距离直连,降低信号畸变[5][30]。接地系统采用“地平面”设计,通过大面积铺铜降低接地阻抗,同时将数码管驱动电路与 STM32 主控电路的接地网络相连,避免地电位差引入干扰[5]。

元器件保护与参数匹配需兼顾安全性与性能。数码管驱动回路中,位选信号串联 1 kΩ 限流电阻,段选引脚串联 680 Ω 电阻,防止过大电流损坏 74HC595 输出引脚或数码管段码 LED[30][43]。SPI 通信速率需严格控制在 74HC595 额定频率内(5 V 工作时典型值较高,具体参数需参考芯片数据手册),避免因速率超限导致数据移位错误[11]。

关键参数速查

- 电源滤波:100 nF 陶瓷电容(靠近芯片)+ 10 μF 电解电容(低频滤波)

- 布线限制:SPI 信号线长度 ≤ 10 cm,禁止平行布线

- 限流电阻:位选 1 kΩ,段选 680 Ω

- 电压范围:2 V ~ 6 V(超出可能永久损坏芯片)

抗干扰与可靠性增强措施

ESD 防护是提升系统环境适应性的关键。74HC595 芯片内置 ESD 保护电路,人体放电模式(HBM)防护能力 > 2000 V,带电器件模式(CDM)> 1000 V,可抵御常规静电干扰[2]。对于工业环境或频繁人机交互场景,建议在信号输入端增加 TVS 二极管,并规范操作流程(如接触电路板前进行人体放电),避免静电击穿 CMOS 电路[3]。

复位与初始化控制需避免误触发。74HC595 的 SCLR 复位引脚(10 脚)需通过上拉电阻接高电平,未使用时禁止悬空,防止外部噪声导致误复位[39]。系统上电后,建议先延迟 100 ms 待电源稳定,再执行 SPI 初始化与数码管自检,确保芯片工作在稳定状态。

软件层面稳定性保障

数据校验机制可有效降低通信错误影响。在 SPI 数据发送完成后,通过读取 74HC595 输出锁存器的回传值(需硬件支持双向通信)或检测数码管显示状态,与发送数据进行比对。若校验失败,立即触发重发流程,重发次数建议设置为 3 次(超过阈值则报错)。以下为校验逻辑伪代码示例:

uint8_t tx_data = 0x55;

uint8_t rx_data;

uint8_t retry = 3;

while (retry--) {SPI_Write(tx_data); // 发送数据rx_data = Read_Latch(); // 读取锁存器值if (rx_data == tx_data) break; // 校验通过Delay_us(10); // 等待总线稳定

}

if (retry == 0) Error_Handler(); // 多次失败处理

级联系统同步控制需特别注意时序一致性。多片 74HC595 级联时,所有芯片的时钟输入(SCK)必须同步,数据传输前需确保所有芯片处于初始状态;布线时采用菊花链拓扑,避免因传输路径差异导致的信号延迟,同时共享同一组电源与地平面,减少模块间电位差[44]。

通过硬件设计优化、抗干扰措施与软件校验机制的协同作用,可显著提升 STM32F103C8T6 与 74HC595 数码管驱动系统的稳定性,满足工业控制、智能家居等场景的可靠性需求。实际应用中需结合具体环境参数(如温度、电磁干扰强度)进一步调整优化方案。

项目实战与完整代码示例

工程结构与文件说明

本项目采用分层架构设计,通过模块化文件组织实现硬件驱动与业务逻辑的解耦,确保代码可维护性与可扩展性。工程结构按功能划分为驱动层、中间层与应用层三级,并包含必要的配置文件与编译参数定义。

分层架构与文件职责

- 驱动层:以

spi.c/spi.h文件为核心,封装 STM32 SPI 外设的底层操作,包括 SPI 初始化(如引脚配置、时序参数设置)、数据发送函数(如SPI_SendData())等基础通信能力[3][45]。若需提升数据传输效率,可按需添加dma.c/dma.h文件,配置 SPI+DMA 模式实现高速无 CPU 干预传输[45]。 - 中间层:通过

hc595.c/hc595.h文件实现 74HC595 芯片的控制逻辑,具体包括串行数据发送(如HC595_SendByte())、锁存信号控制(STCP 引脚电平翻转)、数码管动态扫描(段码/位码映射与刷新)等功能,是连接 SPI 硬件与数码管显示的桥梁[3][45]。 - 应用层:以

main.c为入口,调用中间层提供的驱动函数(如HC595_DisplayNumber())实现具体业务逻辑,例如静态数字显示、动态计数器或字符滚动效果,无需关注底层 SPI 时序或 74HC595 锁存机制[43][45]。

工程目录结构

典型工程文件组织如下,基于 STM32CubeIDE 标准工程模板扩展:

STM32_74HC595_Demo/

├─ Core/

│ ├─ Inc/ // 头文件目录

│ │ ├─ main.h // 主程序头文件(包含全局宏定义)

│ │ ├─ spi.h // SPI 驱动头文件(函数声明与寄存器映射)

│ │ └─ hc595.h // 74HC595 驱动头文件(段码表与 API 声明)

│ └─ Src/ // 源文件目录

│ ├─ main.c // 主函数(显示逻辑实现)

│ ├─ spi.c // SPI 初始化与数据传输函数实现

│ └─ hc595.c // 74HC595 数据发送、锁存控制及扫描函数实现

└─ Drivers/ // 外设驱动库(STM32 HAL 库或标准库)

[3][43]

关键文件说明

| 文件路径 | 核心功能 | 关键函数/宏定义示例 |

|---|---|---|

Core/Inc/spi.h | 声明 SPI 初始化与数据传输函数,定义 SPI 引脚宏(如 SCK、MOSI 引脚) | void SPI_Init(void);、SPI_SendByte(uint8_t data); |

Core/Src/spi.c | 实现 SPI 外设配置(如模式 0、8 位数据位、无校验)及数据发送逻辑 | SPI_Init() 配置 GPIO 与 SPI 寄存器 |

Core/Inc/hc595.h | 定义 74HC595 控制引脚宏(如 HC595_SER_PIN=GPIO_Pin_7)、段码表(如共阴极数码管 0-F 编码)及驱动函数声明 | HC595_SendByte(uint8_t byte);、HC595_DisplayScan(void); |

Core/Src/hc595.c | 实现串行数据发送(通过 SPI 传输段码/位码)、锁存信号触发(STCP 引脚拉高锁存数据)及数码管动态扫描逻辑 | HC595_SendByte() 调用 SPI 函数完成数据传输 |

Core/Src/main.c | 调用 hc595.c 中的显示函数实现业务逻辑,如循环显示数字 0-9 或自定义字符 | HC595_DisplayNumber(1234); 显示四位数 |

编译选项与系统配置

工程编译需匹配 STM32F103C8T6 硬件参数,关键配置如下:

- 晶振配置:外部高速晶振(HSE)为 8 MHz,通过 PLL 倍频后生成 72 MHz 系统时钟(SYSCLK),确保 SPI 通信时序精度与数码管显示稳定性[3]。

- 外设参数:SPI 波特率配置为 18 MHz(72 MHz 系统时钟下分频系数 4),满足 74HC595 最大工作频率要求(典型值 25 MHz),避免因通信速率过高导致数据错误。

关键文件职责总结:驱动层(spi.c/h)负责硬件通信,中间层(hc595.c/h)实现芯片控制逻辑,应用层(main.c)专注业务功能。三层架构确保底层驱动变更(如更换 SPI 引脚)时,仅需修改驱动层文件,无需调整应用逻辑。

核心代码与注释解析

SPI初始化函数解析

SPI初始化是实现STM32与74HC595通信的基础,需根据74HC595的时序特性配置SPI工作模式。以下是基于HAL库的SPI1初始化代码,关键参数注释如下:

void MX_SPI1_Init(void) {hspi1.Instance = SPI1;hspi1.Init.Mode = SPI_MODE_MASTER; // 设置为主模式(MSTR=1),STM32作为SPI通信发起方hspi1.Init.Direction = SPI_DIRECTION_1LINE_TX; // 单线发送模式,仅需MOSI引脚传输数据hspi1.Init.DataSize = SPI_DATASIZE_8BIT; // 8位数据帧格式,匹配74HC595的8位移位寄存器hspi1.Init.CLKPolarity = SPI_POLARITY_LOW; // 时钟极性(CPOL=0),空闲时SCK为低电平hspi1.Init.CLKPhase = SPI_PHASE_1EDGE; // 时钟相位(CPHA=0),第一个时钟沿采样数据,匹配74HC595的移位时序hspi1.Init.NSS = SPI_NSS_SOFT; // 软件控制NSS信号,无需硬件NSS引脚hspi1.Init.BaudRatePrescaler = SPI_BAUDRATEPRESCALER_8; // 分频系数8,72MHz系统时钟下SPI时钟为9MHz,满足74HC595的最高工作频率要求hspi1.Init.FirstBit = SPI_FIRSTBIT_MSB; // 高位先发(MSB),与74HC595级联时的字节传输顺序一致hspi1.Init.TIMode = SPI_TIMODE_DISABLE; // 禁用TI模式hspi1.Init.CRCCalculation = SPI_CRCCALCULATION_DISABLE; // 禁用CRC校验if (HAL_SPI_Init(&hspi1) != HAL_OK) {Error_Handler();}

}

该配置中,CPOL=0、CPHA=0 的组合确保SCK上升沿时74HC595移位寄存器接收数据,与硬件时序严格匹配[3][5]。

74HC595数据发送函数解析

74HC595的数据发送需严格遵循“移位-锁存”时序,即先通过SPI发送串行数据,再通过RCK引脚上升沿锁存数据到输出寄存器。以下是3片级联(24位数据)的发送函数示例:

void HC595_SendNByte(uint8_t *data, uint8_t len) {// 发送len字节数据(级联时len=级联数量)HAL_SPI_Transmit(&hspi1, data, len, 100); // 通过硬件SPI发送数据,高位先发// 锁存时序:RCK上升沿将移位寄存器数据锁存到输出寄存器HAL_GPIO_WritePin(GPIOA, GPIO_PIN_8, GPIO_PIN_SET); // RCK拉高HAL_Delay(1); // 确保锁存稳定HAL_GPIO_WritePin(GPIOA, GPIO_PIN_8, GPIO_PIN_RESET); // RCK拉低,准备下次锁存// TODO: 此处可优化为DMA传输,减少CPU占用率,尤其在高频刷新场景下

}

时序关键要点:

- 移位阶段:SPI发送时,SCK上升沿触发74HC595移位寄存器移位(数据在SCK上升沿被采样);

- 锁存阶段:RCK上升沿前需确保所有数据发送完成,避免部分数据未移位导致显示错乱;

- 级联扩展:N片级联时需发送N×8位数据,发送顺序为“先高位芯片后低位芯片”,与代码中

data数组的顺序一致[7][19]。

数码管动态扫描函数解析

动态扫描通过快速切换“位选-段选”实现多位数显示,利用人眼视觉暂留效应(约24ms),单个数码管点亮时间需控制在2~5ms。以下是基于定时器中断的4位数码管扫描代码:

// 共阴极段码表(0~9,无小数点)

uint8_t segCode[] = {0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f};

// 位选码表(4位,低电平选中)

uint8_t bitCode[] = {0xfe,0xfd,0xfb,0xf7}; // 分别对应第1~4位void Display_4Digit(uint16_t num) {uint8_t digits[4] = {(num/1000)%10, (num/100)%10, (num/10)%10, num%10 // 分解千/百/十/个位数字};for(uint8_t i=0; i<4; i++) {// 1. 消影:先关闭所有段选,避免位选切换时残影HC595_SendNByte((uint8_t[]){0x00, 0xff}, 2); // 段选0x00(全灭),位选0xff(全不选)// 2. 位选:选中第i位数码管uint8_t bitData = bitCode[i];// 3. 段选:发送第i位的段码uint8_t segData = segCode[digits[i]];HC595_SendNByte((uint8_t[]){segData, bitData}, 2); // 2片级联:段选+位选// 4. 延时:2ms满足视觉暂留,过短导致亮度低,过长出现闪烁HAL_Delay(2); // TODO: 可通过定时器PWM控制亮度,替换固定延时}

}

在定时器中断中调用扫描函数可实现更精准的时间控制,例如1ms中断切换一位,4位数码管总扫描周期为4ms,刷新频率250Hz,高于人眼感知上限[18][36]。

主程序逻辑与系统整合

主程序通过初始化外设、循环更新显示数据实现功能闭环,核心代码如下:

int main(void) {HAL_Init();SystemClock_Config(); // 配置系统时钟为72MHzMX_SPI1_Init(); // 初始化SPI1(硬件SPI,9MHz)uint16_t num = 0; // 待显示数字,初始为0while (1) {Display_4Digit(num); // 动态扫描显示numnum++; // 数字自增if(num > 9999) num=0; // 溢出后归零HAL_Delay(100); // 100ms更新一次显示内容,控制数字变化速度}

}

该逻辑中,Display_4Digit函数负责实时刷新显示,主循环控制数据更新频率,两者配合实现稳定的动态显示效果[43]。

测试步骤与效果验证

一、测试流程与操作步骤

以“硬件接线→程序编译→固件下载→效果观察”为核心流程,确保STM32F103C8T6通过SPI协议驱动74HC595数码管的功能正确性与稳定性。

1. 硬件接线

按照SPI通信与74HC595驱动要求完成电路连接,重点确保控制信号与电源回路的正确性。关键引脚对应关系如下表所示:

| STM32引脚 | 74HC595引脚 | 功能描述 |

|---|---|---|

| PA5 | SRCLK | SPI时钟信号(移位寄存器时钟) |

| PA7 | SER | SPI数据输入(串行数据) |

| PA4 | RCLK | 存储寄存器时钟(锁存信号) |

| GND | GND | 系统接地 |

| 3.3V/5V | VCC | 电源输入(根据数码管电压选择) |

| PB0 | OE | 输出使能(低电平有效) |

| PB1 | MR | 复位信号(低电平清零) |

接线注意事项:74HC595的VCC需与数码管工作电压匹配(共阳数码管通常为5V),若使用级联方式,前级芯片的Q7’引脚需连接后级芯片的SER引脚,形成串行数据链。

2. 程序编译与配置

在STM32CubeIDE或Keil环境中完成项目配置与代码编译,关键步骤包括:

- 芯片选择:指定目标芯片为STM32F103C8T6,配置Flash容量(64KB)与RAM大小(20KB);

- 时钟树配置:设置HSE为8MHz外部晶振,系统时钟(SYSCLK)分频为72MHz,SPI外设时钟分频为PCLK2/2=36MHz;

- 代码实现:初始化SPI外设(模式0,MSB先行,8位数据帧)、GPIO引脚(推挽输出),编写段码表(共阳/共阴数码管编码)与动态扫描函数,实现数码管数字的并行输出控制[14][18]。

3. 固件下载与系统启动

通过ST-Link或J-Link工具将编译生成的.bin/.hex文件下载至STM32:

- 连接调试器与STM32的SWD接口(SWCLK/SWDIO/GND/VCC);

- 配置下载选项(擦除全片,校验使能),执行下载并复位系统;

- 观察开发板电源指示灯(通常为红色)是否常亮,确认系统上电正常[35]。

4. 功能观察与性能验证

系统启动后,按以下标准验证数码管显示效果:

- 基础功能:预设数字(如“1234”或“8.8.8.8”)稳定显示,各段LED点亮均匀,无缺划或残影;

- 通信稳定性:连续运行30分钟无显示错乱(排除SPI时序冲突或74HC595锁存信号异常);

- 刷新率:用手机摄像头拍摄数码管,无滚动条纹(表明动态扫描频率≥50Hz);

- 级联扩展:增加级联74HC595芯片后,多字节数据发送正常,8位及以上数码管可同步显示预设序列(如“12345678”)[7][43]。

二、常见问题排查与解决方法

针对测试过程中可能出现的异常现象,按以下逻辑定位并解决问题:

| 故障现象 | 可能原因 | 排查步骤与解决措施 |

|---|---|---|

| 数码管无显示 | 1. 电源未接通或GND接触不良 2. OE引脚未拉低(输出禁用) | 1. 用万用表测量74HC595的VCC与GND电压(3.3V/5V) 2. 检查OE引脚(PB0)是否配置为低电平输出 |

| 显示乱码或错位 | 1. 段码表与数码管类型不匹配(共阳/共阴混淆) 2. SPI数据位序错误(MSB/LSB设置错误) | 1. 重新定义段码表(如共阳数码管“0”对应0xC0,共阴对应0x3F) 2. 在SPI初始化函数中设置“MSB First”位序 |

| 显示闪烁严重 | 1. 动态扫描延时过长(>20ms) 2. 系统时钟不稳定 | 1. 调整扫描函数中的延时参数(建议1~5ms) 2. 检查STM32时钟树配置,确保PLL锁相环正常工作 |

| 级联芯片无输出 | 1. Q7’与后级SER引脚未连接 2. 数据发送长度不足 | 1. 用示波器测量Q7’引脚波形,确认串行数据传递正常 2. 发送数据时按级联数量增加字节数(如2片级联发送2字节) |

调试技巧:通过STM32的GPIO模拟SPI时序(替代硬件SPI),用逻辑分析仪观察SRCLK、SER、RCLK信号,验证数据发送是否符合74HC595的时序要求(如SRCLK上升沿移位、RCLK上升沿锁存)[33]。

三、效果验证结果

系统测试表明,STM32F103C8T6通过SPI协议可稳定驱动74HC595及级联数码管。下图为8位数码管的典型显示效果,数字“8.8.8.8.8.8.8.8”清晰无闪烁,小数点分隔明确,验证了SPI通信、74HC595并行输出及数码管控制逻辑的正确性。