【芯片设计-信号完整性 SI 学习 1.1 -- 眼图、抖动、反射、串扰】

文章目录

- 1. 眼图(Eye Diagram)

- 2. 抖动(Jitter)

- 3. 反射(Reflection)

- 3.1 信号反射机理

- 3.2 消除反射的措施

- 4 . 串扰(Crosstalk)

- 4.1 叠加原则

- 4.2 近端串扰和远端串扰

- 5. 四者之间的联系

- 6. 总结对比表

本篇文章 会对 眼图、抖动、反射、串扰 四个在 信号完整性(SI, Signal Integrity)测试中最核心的概念进行介绍。

1. 眼图(Eye Diagram)

定义

- 眼图是把高速信号在一个 UI(Unit Interval,比特周期)上叠加显示的结果,看起来像 “眼睛” 形状。

由于眼图是用一张图形就完整地表征了串行信号的比特位信息,所以成为了衡量信号质量的最重要工具,眼图测量有时侯就叫“信号质量测试(Signal Quality Test,SQ Test)”。 此外 ,眼图测量的结果是合格还是不合格,其判断依据通常是相对于“模板(Mask) ”而言的。模板规定了串行信号“1”电平的容限,“0”电平的容限,上升时间、下降时间的容限。

由于眼图是用一张图形就完整地表征了串行信号的比特位信息,所以成为了衡量信号质量的最重要工具,眼图测量有时侯就叫“信号质量测试(Signal Quality Test,SQ Test)”。 此外 ,眼图测量的结果是合格还是不合格,其判断依据通常是相对于“模板(Mask) ”而言的。模板规定了串行信号“1”电平的容限,“0”电平的容限,上升时间、下降时间的容限。

如图所示, 示波器测量的一般的信号是一些位或某一段时间的波形, 更更多的反 映的是细节信息。 而眼图则反映的是链路上传输的所有数字信号的整体特征。

作用

- 提供一个直观评估信号是否可正确采样的“窗口”:

- 竖直开口高度 → 电压裕量(抗噪声能力)

- 水平开口宽度 → 时间裕量(时序抖动余量)

- 闭合程度 → 信号失真严重

举例

- DDR4、PCIe、USB、SerDes bringup 时会用示波器采集眼图,判断链路是否满足标准规范。

- 如果眼图闭合 → 说明噪声、抖动、串扰过大,数据错误概率上升。

2. 抖动(Jitter)

定义

- 抖动是信号时序上的不稳定,指理想采样点与实际采样点的偏差 。抖动(Jitter) 反映的是数字信号偏离其理想位置的时间偏差,是一个时域上的概念。

高频数字信号的bit周期都非常短,—般在几百ps甚至几十ps, 很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。包括确定性抖动和随机抖动。实际信号的很复杂,可能既有随机抖动成分(RJ), 也有不同频率的确定性抖动成分(DJ)。

-

随机抖动 (RJ):由热噪声、相位噪声引起,随机抖动是指由较难预测的因素导致的时序变化。随机抖动最基本的一个特性就是随机性,因此我们可以用高斯统计分布来描述其特性。

-

确定性抖动 (DJ):确定性抖动的来源主要有4种:

- 1 相邻信号走线之间的串扰

- 2 敏感信号通路上的EMI辐射

- 3 多层基底中电源层的噪声

- 4 多个门电路同时转换为同一种逻辑状态

作用

-

抖动会直接导致眼图的 水平闭合,减小时序裕量。

-

在 高速串行接口 (PCIe, SATA, SerDes) 中,抖动测试是关键指标之一。

举例

- PCIe Gen4 以上标准会要求测试 TJ@BER=10⁻¹² (总抖动在误码率 1E-12 时的统计值)。

- DDR Margining 测试时,会量化数据与时钟之间的 Setup/Hold 裕量,等价于抖动测试。

3. 反射(Reflection)

传输时,每一时刻都会遇到一个传输线的瞬时阻抗,当该瞬时阻抗发生变化时,一部分信号将会反射,另一部分将会继续向前传输。或者说反射就是回波,信号功率的一部分传输到线上并达到负载端,但是有一部分反射会回源端。

定义

- 当传输线阻抗不连续(过孔、连接器、飞线、端接不匹配)时,信号会发生部分能量反射。

- 反射系数 Γ = (Z_load - Z0) / (Z_load + Z0),Z0 为传输线特性阻抗。

阻抗:将传输线始端的输入阻抗称为阻抗。

瞬时阻抗:将信号在互连传输过程中随时遇到的阻抗称为瞬时阻抗。

特征阻抗:如果传输线有恒定不变的瞬时阻抗,就称为传输线的特征阻抗。

一般都是用特征阻抗来描述传输线阻抗(单端50ohm、差分100ohm),其是影响传输线在电路中信号完整性的一个主要因素。

3.1 信号反射机理

信号沿传输线向前传播时,每时每刻都会遇到一个瞬时阻抗,这个阻抗可能是传输线本身的,有可能是中途的过孔、线宽的变化或者末端的其他元件等。对于信号来说,它不会区分到底是什么,信号所能感受到的就是阻抗的变化,如果阻抗不变就会继续向前传播,阻抗变化就会发生反射。。

3.2 消除反射的措施

消除反射可以通过更改传输线的不连续结构、端接匹配、走线拓扑来进行调整。

- 更改走线不连续结构:减少走线的现款的突变、减少过孔的使用或者减少STUB等措施。

- 端接匹配包括:

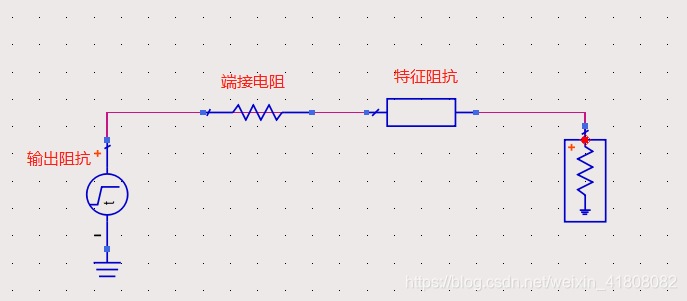

- 串联端接:在源端串一个电阻,电阻阻值加上驱动端的输出阻抗应该等于传输线的特征阻抗,以此来消除负载端的反射。在这种情况下会发生一次反射,每条线上只用加上一个电阻,消耗功率小,但是会增加信号的传输时间,减缓信号的上升和下降时间。

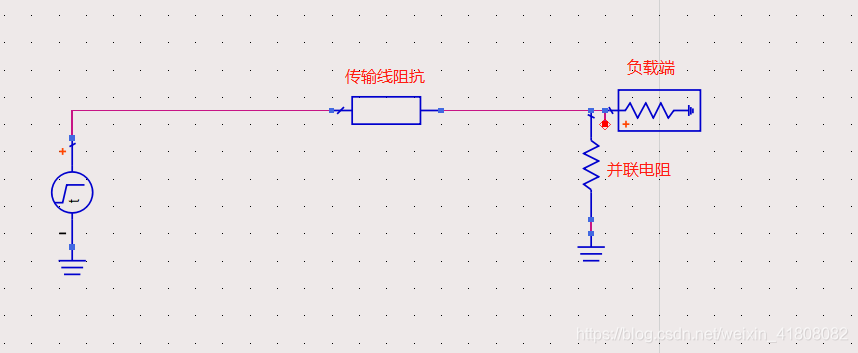

- 并联端接:在负载端并联电阻,电阻的阻值需要和传输线的特征阻抗相等,以此来消除终端的一次反射。并联电阻可以上拉到电源或下拉到地,适用于多负载的情况。

举例

-

DDR 总线如果终端电阻没有按标准 50Ω 匹配,写入波形会出现振铃 → 影响 Setup/Hold。

-

PCIe 链路中,过孔未优化会导致反射,引起 S参数测试失败。

4 . 串扰(Crosstalk)

定义

串扰(Crosstalk)是指临近信号线之间相互耦合,产生预期以外的噪声的现象,即使它们并没有直接的电气连接。例如下图中,A、B为临近的信号线,即使B是空闲状态的低电位,当A的电压变化时,B上的电压也会受到影响,出现一定的变化。

电气电子系统中,这种由于电磁感应的基本原理,产生的线间耦合现象无处不在。我们熟悉的变压器,就是利用这种电磁耦合现象制成的设备;但在信号系统中,我们通常希望这种耦合尽可能的减少,因为这会使信号线上产生额外的噪声,对系统的信号完整性带来挑战。

4.1 叠加原则

基于以上多对多的基本事实,我们在评估某一条信号线接受的串扰时,采取的基本方法是,单独研究所有干扰源对他的影响,再将所有干扰源的影响叠加,这个基本方法遵从的就是叠加原则。

4.2 近端串扰和远端串扰

下图展示的有2条相邻信号线的系统,在干扰线的源端输入一个阶跃信号,以受害线的源端(A)和终端(B)作为测试点,可以分别测出这2点的噪声波形。

A点和干扰信号输入都在源端,观察到的噪声即为近端串扰(Next);B点和干扰信号输入不在同一端,观察到的噪声即为远端串扰(Fext)。这两种噪声的表现是不一样的,下面分别做简单介绍。

举例

-

DDR3/DDR4 数据总线如果布线密集 → 相邻 DQ 串扰 → 导致读写眼图闭合。

-

SerDes 通道中,FEXT 可能在高频下造成误码率(BER)显著上升。

5. 四者之间的联系

-

眼图 是整体结果,反映了 抖动、反射、串扰 等失真的综合效果。

-

抖动 → 眼图水平收窄

-

反射 → 信号畸变、过冲/下冲 → 眼图竖直收窄

-

串扰 → 叠加噪声 & 时序偏移 → 眼图竖直+水平同时收窄

可以理解为:

抖动、反射、串扰 = 根因

眼图 = 体检报告

6. 总结对比表

| 项目 | 定义 | 在眼图中的表现 | 测试方法 | 举例 |

|---|---|---|---|---|

| 眼图 | 综合波形叠加,直观表征信号质量 | 开口高度=电压裕量;开口宽度=时间裕量 | 示波器采集眼图 | PCIe、DDR bringup 验证 |

| 抖动 | 采样时间偏移 | 水平闭合 | TIE/Jitter 分析,BER 仿真 | PCIe Gen4 TJ@BER 测试 |

| 反射 | 阻抗不连续导致回波 | 噪声叠加,竖直闭合 | TDR/TDT,示波器波形 | DDR 终端不匹配导致振铃 |

| 串扰 | 相邻走线耦合干扰 | 噪声/时序漂移,眼图收窄 | Crosstalk 仿真,示波器/误码仪 | DDR DQ 串扰导致 BER 增加 |

推荐阅读:

https://jz.docin.com/p-257887208.html

https://blog.csdn.net/huxyc/article/details/135706281

https://zhuanlan.zhihu.com/p/713786133