Linux学习-ARM 架构与处理器相关知识

一、CPU 内核类型

RISC(Reduced Instruction Set Computer,精简指令集计算机):采用精简的指令集,指令长度固定,大多数指令可在一个时钟周期内完成,注重硬件执行效率,通过大量通用寄存器减少内存访问。

CISC(Complex Instruction Set Computer,复杂指令集计算机):拥有丰富多样的指令集,指令长度不固定,部分复杂指令需要多个时钟周期完成,更注重软件编程的便捷性。

ARM 归属:ARM 属于 RISC 架构,遵循精简指令集的设计原则。

二、ARM 核心组件与寄存器

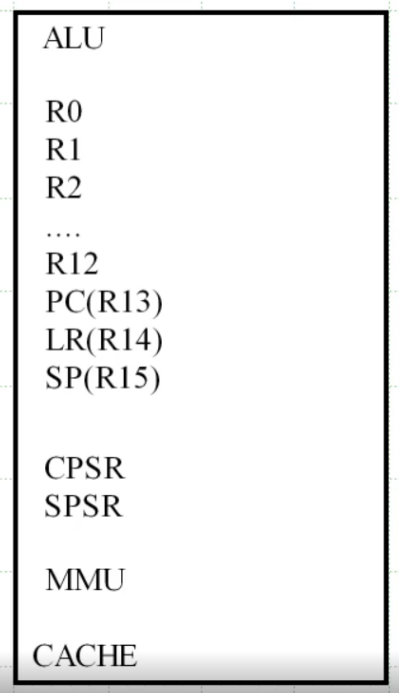

ARM 内核主要由运算器、控制器、寄存器组和总线接口等部分组成。运算器包含算术逻辑单元(ALU),负责执行各种算术和逻辑运算;控制器用于取指令、译码并控制指令的执行流程;寄存器组提供快速的数据存储和访问,支持指令的高效执行;总线接口则实现内核与外部存储器和外设之间的数据传输。

(一)通用寄存器(内核)

- 无固定地址,包括 R0 - R12 等。

- 特殊功能寄存器:

- PC(Program Counter):程序计数器,用于指向即将执行的指令地址。

- LR(Linked Register):链接寄存器,用于保存返回地址等。

- SP(Stack Pointer):栈指针,指向栈顶位置。

- CPSR(Current Program Status Register):当前程序状态寄存器,记录当前程序运行状态。

- SPSR(Saved Program Status Register):备份程序状态寄存器,用于备份程序状态。

(二)Cortex - A7 内核组件

包含 ALU(算数逻辑单元)、MMU(内存管理单元,操作系统工作时启用)、CACHE(高速缓存,分为指令缓存 Instruction Cache 和数据缓存 Data Cache)。

三、ARM 工作模式

| 模式 | 说明 |

|---|---|

| User | 非特权模式,大部分任务执行在该模式,权限最低。 |

| FIQ | 当有高优先级中断产生时进入,用于快速处理高优先级中断。 |

| IRQ | 当有普通优先级中断产生时进入,处理普通中断。 |

| Supervisor | 当复位或中断指令执行时进入,属于特权模式。 |

| Abort | 当存取异常时进入,用于处理存储访问异常。 |

| Undef | 当执行未定义指令时进入。 |

| System | 权限与 User 不同,是拥有和 User 模式相同寄存器集的特权模式。 |

| Monitor(Cortex - A 特有) | 为安全扩展的模式,用于执行安全监控代码,是特权模式。 |

ARM9 和 Cortex A 的寄存器数量

• **ARM9:**有 37 个 32 位寄存器,包括 31 个通用寄存器和 6 个状态寄存器。这些寄存器根据工作模式的不同而被分组使用,不同模式下可见的寄存器有所差异。

• Cortex A 系列(ARMv7 - A 架构):有 37 个通用寄存器(包括 30 个通用 - purpose 寄存器和 7 个与状态寄存器相关的寄存器),具体数量和分组会根据工作模式有所变化,以适应不同的操作需求。

四、异常产生时 ARM 内核的工作

当异常产生时,ARM 内核会依次执行以下操作:

保存当前程序状态寄存器(CPSR)的值到将要进入的异常模式对应的 SPSR(保存程序状态寄存器)中。

修改 CPSR 中的相应位,以切换到对应的异常模式,并禁止相应的中断(如 IRQ),防止嵌套异常干扰。

将异常返回地址保存到异常模式下的 LR(链接寄存器)中。

强制程序计数器(PC)指向异常向量表中对应的异常处理入口地址,开始执行异常处理程序。

五、硬件架构与总线

- 冯·诺依曼架构:指令和数据共享同一存储空间和总线。

- 哈佛架构:指令和数据有各自独立的存储空间和总线,ARM 采用此架构。

- 总线层级:

- AHB:高速总线,用于连接高性能模块。

- APB:低速总线,用于连接外设(Peripherals)等低速模块。

六、存储相关

- RAM(随机存取存储器):易失性存储器,断电后数据丢失。

- ROM(只读存储器):非易失性存储器,断电后数据不丢失。

七、芯片架构(SoC)

SoC(系统级芯片)集成了 ARM 内核、GPU、Timer(定时器)、RAM 等模块,还可外接 ROM 等存储设备。

八、补充概念

- ALU:算数逻辑单元,执行算数和逻辑运算。

- MMU:内存管理单元,负责内存的分配、映射等管理工作。

- CACHE:高速缓存,用于缓解 CPU 和内存之间的速度差异,提高数据访问效率。

- 异常向量表:异常向量表是 ARM 处理器中一个特定的存储区域,其中存放着各种异常处理程序的入口地址。当某种异常发生时,处理器会根据异常的类型,自动跳转到异常向量表中对应的入口地址,从而执行相应的异常处理程序。异常向量表中的每个入口通常对应一种特定的异常类型,如复位、未定义指令、中断等,其地址是固定的,以便处理器快速定位和响应异常。