【期末复习】嵌入式——S5PV210开发板

本文为嵌入式课程期末复习,仅供参考,所用课本:嵌入式Linux操作系统(李建祥著)。

第一章

1.1 简述嵌入式微处理器数据存储格式的大,小端模式。

大端模式是指数据的高字节保存在内存的低地址中,而数据的低字节保存在内存的高地址中。

小端模式则是指数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中。

1.2 Cortex-A8 处理器主要由哪 5 部分组成?

(1)处理器核心:负责执行指令和数据处理,支持多种指令集,能够高效地执行各种计算任务。

(2)内存管理单元(MMU):处理器中负责内存管理的部分,提供了虚拟内存到物理内存的映射功能。通过 MMU,Cortex-A8 可以实现内存保护、地址转换以及多任务之间的内存隔离。

(3)高速缓存:Cortex-A8 通常配备了一级(L1)和二级(L2)高速缓存,用于存储处理器经常访问的数据和指令。可以提高处理器的性能,减少访问主存的延迟。

(4)浮点单元(FPU):专门用于执行浮点运算的硬件部分,使得处理器在处理复杂数学运算和图形处理等方面具有出色的性能。

(5)外设接口:用于连接各种外部设备。

1.3 写出 R 寄存器组中 r13、r14、r15 的名称和作用。

(1) r13(堆栈指针寄存器SP),用于指向当前堆栈的顶部。

(2) r14(链接寄存器LR),用于存储子程序返回主程序的链接地址。当处理器执行调用指令(如BL)时,r14 用于存储了程序计数器 PC的备份,供子程序的返回主程序。

(3) r15(程序计数器PC),指向当前的程序地址。PC 的值决定了 CPU接下来要执行的指令的地址。在ARM 体系结构中,由于采用了多级流水线技术,PC总是指向当前指令的下两条指令的地址。

1.4 简述 Cortex-A8 处理器的 8 种工作模式。

(1) 用户模式:正常程序执行的模式,大多数应用程序代码都在此模式下运行。该模式为非特权模式,限制内存的直接访问和通过物理地址对硬件设备进行读写操作。

(2) 系统模式:使用与用户模式相同的寄存器组,但拥有特权级操作系统任务

的执行能力,允许访问硬件资源和执行特权操作。

(3) 管理模式:操作系统使用的保护模式,通常系统复位或软件中断时进入此模式。

(4) 中断模式:当低优先级中断发生时进入此模式,常用于处理普通的外部中断。

(5) 快速中断模式:当高优先级中断发生时进入此模式,用于高速数据传输和通道处理。

(6) 数据访问中止模式:当存取异常(如无效的内存访问)发生时进入此模式。

(7) 未定义指令中止模式:当执行未定义指令时进入此模式,用于支持硬件协处理器的软件仿真。

(8) 监控模式:可在安全模式与非安全模式之间进行转换。

除用户模式外,其余模式都属于特权模式,该模式下可以访问所有的系统资源。

1.5 如何确定系统出于哪种操作模式?

使用mrs命令将cpsr寄存器中的值读取出来,比较其模式位M[4:0]的值判断当前所处模式。

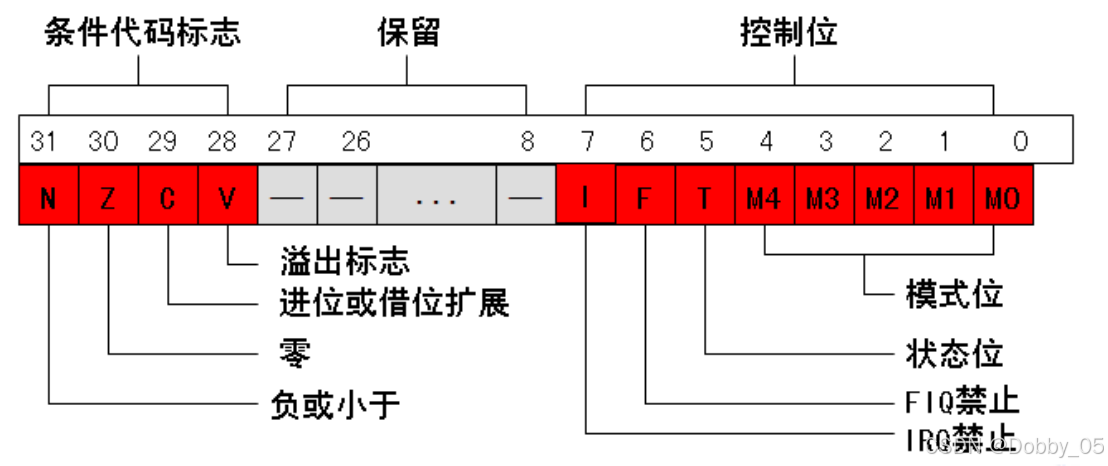

1.6 简述 Cortex-A8 处理器的 CPSR 寄存器各功能位名称和功能定义

(1) 条件标志位:

N负数或小于标志位:N=1表示运行结果为负数。

Z零标志位:Z=1表示运算结果为零。

C进位/借位标志位:加法运算中,若结果产生了进位,C=1,减法运算中,若发生借位,C=0。

V溢出标志位:V=1,表示两个有符号数相加结果溢出。

Q 标识位:若执行乘法和分数算术运算指令时,发生溢出,则Q被置为1。

(2) 状态控制位:

IT:条件语句执行控制位。

J:T=1时,依据J位决定处理器的工作状态。

E:决定数据的端模式(大端/小端)。

(3) 控制位:

I:IRQ 中断禁止位。I=1 时,禁止 IRQ 中断,反之允许。

F:FIQ 中断禁止位。F=1 时,禁止 FIQ 中断,反之允许。

T:Thumb 状态位。决定处理器的工作状态。

M[4:0]:工作模式位。用于决定当前处理器的工作模式。

第二章

2.1 举例说明 ARM 汇编指令所支持的寻址方式。

(1) 立即数寻址:立即数作为操作数在指令中给出SUB R0, R1, #1

(2) 寄存器寻址:操作数存放在寄存器中,指令执行时直接取出寄存器值来操作。MOV R1, R2

(3) 寄存器间接寻址:操作数保存在寄存器指定地址的存储单元中。LDR R1, [R2]

(4) 寄存器移位寻址:寄存器寻址得到的操作数再进行移位得到最终的操作数。MOV R0, R2, LSL #3

(5) 基址寻址:基址寄存器中的值与指令中的偏移地址量相加,形成操作数的有效地址。LDR R2, [R3, #0x5]

(6) 相对寻址:将程序计数器作为基址寄存器,指令中的标号作为地址偏移量,两者相加得到操作数存放地址。B process

(7) 多寄存器寻址:一条指令可以完成多个寄存器值的传送。LDMIA R1, {R2-R4, R5}

补充:IA每次传送后地址加4,DA减4(I increment A after D decrement)

IB每次传送前地址加4,DB减4(B before)

FA满递增堆栈,FB满递减堆栈(F full)

EA空递增堆栈,EB空递减堆栈(E empty)

(8) 块拷贝寻址:可实现数据块的复制。LDMIA R0 {R1-R5}

(9) 堆栈寻址:用于数据栈与寄存器组之间的批量数据传输。LDMFD R13!,{R0,R1,R2,R3,R4}

R13为堆栈指针,此指令将R0-R4依次压入堆栈中

2.2 ARM GNU汇编

2.2.1 相对跳转指令 b 和 bl

bl 指令除了跳转之外,还将返回地址(bl 指令下面一条指令的地址)保存在lr寄存器中。 b 和 bl 指令只能实现±32MB 空间的跳转,并且是位置无关指令。

2.2.2 数据传送指令 mov 和伪指令 ldr

mov 指令可以把一个立即数或寄存器的值(这里不能是内存地址)赋给另一个寄存器, mov 指令限制了立即数的长度为 8 位。

mov r1, r2 /* r2 中的内容赋给 r1 */mov r1,#0xFF /* r1=0xFF */ldr 指令即是加载指令(内存访问指令),也是伪指令,作为加载指令时,可以把一个寄存器内的数据加载到另一个寄存器,或内存地址里的数据加载到寄存器中。作为伪指令时,可以在立即数前面加一个等号“=”,以表示把一个地址写到寄存器中去。

对于 ldr 伪指令的第二个参数没有范围的限制,如果立即数的长度不超过 8 位时,编译器会自动转换为 mov 指令。

ldr r1, =100 /* r1=100,系统会自动用 mov 指令代替 */ldr r1, =0x12345678 /* r1=0x12345678 */ldr r1, 0x12345678 /* 将 0x12345678 地址处的值赋给 r1 寄存器*/2.2.3 内存访问指令 ldr、str、ldm、stm

str 是内存访问指令,它的功能与 ldr 相反,它是把数据存到内存中去。

ldr r1, [r2 + 4] /* 将地址为 r2+4 的内存单元数据读取到 r1 寄存器 */str r1, [r2 + 4] /* 将 r1 寄存器的内容保存到地址为 r2+4 的内存单元中 */ldm 和 stm 属于批量内存加载和存储指令,可以实现在一组寄存器和一块连续的内存单元之间传输数据。语法格式如下:

ldm{cond}< mode> {!} {^} stm{cond}< mode> {!} {^}2.2.4 加减指令 add、sub

1)add 寄存器,数据 add r1, 8 /* r1=r1+8 */

2)add 寄存器,寄存器 add r1, r2 /* r1=r1+r2 */

3)add 寄存器,内存单元 add r1, [0x12345678] /* r1 等于 r1 寄存器的值加内存 0x12345678 中的值 */

4)add 内存单元,寄存器 add [0x12345678], r1 /* 内存 0x12345678 中的值加 r1 再写回到 0x12345678 中*/

sub类似

2.2.5 位操作指令 bic、orr

bic 为位清除指令,bic {cond}{S} 目的寄存器,操作数 1,操作数 2

用途:清除操作数 1 的某些位(操作数 2 指定),并把结果写到目的寄存器中。

例如: bic r0, r0, 0x1f //将 r0 的 bit[4:0]

位清零 orr 指令用法与 bic 类似,它是把操作数 1 指定的位(操作数 2)置1。

2.2.6 程序状态寄存器访问指令 msr、mrs

msr 和 mrs 用来对程序状态寄存器 cpsr 和 spsr 进行读写操作。

msr cpsr, r1 /* 将 r1 中的内容写回到 cpsr */

mrs r1, cpsr /* 读取 cpsr 到 r1 */

补充记忆:s-status状态寄存器 r-通用寄存器,所以msr是将通用寄存器的值写入状态寄存器,mrs是将状态寄存器的值读取到通用寄存器中。

第三章

3.1 简述 S5PV210 芯片功能。

(1) 核心架构:采用了 ARM Cortex-A8 内核,基于 ARM V7 指令集,主频可达 1GHZ,具有 64/32 位内部总线结构,以及 32/32KB 的数据/指令一级缓存和 512KB 的二级缓存。

(2) 图形处理能力:内建高性能3D 图形引擎和 2D 图形引擎,支持 2D/3D图形加速。

(3) 视频编解码能力:内建 MFC,支持多种格式视频的编解码,以及模拟/数字 TV 输出。

(4) 图像处理:JPEG 硬件编解码,最大支持 8000x8000 分辨率的图像处理。

(5) 存储和接口:存储控制器支持多种类型的 RAM。Flash 支持 Nandflash、Norflash、OneNand 等。接口丰富。

(6) 高清输出:内建的 HDMI v1.3 接口,可以将高清视频输出到外部显示器上。

(7) 功耗和性能优化:提供了多种电源管理和功耗优化技术,确保高性能低功耗。

3.2 简述 S5PV210 上电复位后的启动过程。

(1)处理器上电后,首先进入复位状态并开始初始化。

(2)执行iROM中的固化代码,即 BL0。

(3)执行 BL0,加载bootloader到片内SRAM中, 即BL1,并跳转到BL1中执行。

(4)执行BL1,加载bootloader剩余部分到SRAM中,即BL2并跳转到BL2中执行。

(5)执行BL2初始化DRAM控制器,并加载操作系统到SRAM中。

(6)处理器跳转到操作系统的起始地址,开始运行操作系统。

3.3 BL0启动序列

(1)禁止看门狗

(2)初始化指令缓存

(3)初始化栈、堆

(4)初始化块设备复制函数

(5)初始化PLL(锁相环)及设置系统时钟

(6)根据OM引脚设置,从相应设置中复制BL1前16KB字节到片内SRAM的0xD0020000地址,并检查BL1的checknum信息,若检查失败,将自动尝试第二次启动

(7)检查是否安全模式启动,是则验证BL1的完整性

(8)跳转到BL1起始地址处

第四章

4.1 常用u_boot命令

Help:查看当前u_boot的所有可用命令

Bdinfo:显示开发板配置信息

Cmp:比较两块存储单元的值

Tftp:通过tftp协议从网络下载文件到指定内存地址

Ping:测试网络连通性

Printenv:打印当前环境变量及其值

Setenv:设置环境变量

Saveenv:保存环境变量

Version:查看当前u_boot版本信息

Reboot:重启

4.2 写出 U-Boot 两种工作模式的作用。

(1) 启动加载模式是应用系统的正常工作模式,该模式自动将嵌入式操作系统从FLASH 中加载到 SDRAM 中运行,无需用户介入。

(2) 下载模式允许 Bootloader 通过某些通信手段将内核映像或根文件系统映像等从 PC 机中下载到目标板的 FLASH 中。通常用于开发阶段,目标机中的u_boot会向终端提供一个简单的命令行接口。

第五章

嵌入式系统开发环境主要由哪两部分构成?

(1) 宿主机指PC或笔记本电脑,用于搭建交叉编译环境,编译用于目标机的系统内核和应用程序。

(2) 目标机指量身定制的一个嵌入式专用平台,用于系统内核和应用程序的测试与运行。

六、其余补充内容

6.1 Flash闪存

Flash闪存是一种非易失性存储器,即供电电源关闭后仍能保存片内信息不丢失。常用的闪存主要有Nor和Nand两类。

(1)接口方面,Nor Flash带有通用的SRAM接口,支持随机访问。而Nand Flash的接口是相对复杂的I/O接口串行的存取数据,需要先发出命令,然后发出相应的地址,最后读/写数据。

(2)容量与成本方面,Nor Flash的容量相比Nand Flash小很多,价格高很多。

(3)可靠性方面,Nor Flash上不存在坏块,而Nand Flash在使用前要进行坏块扫描,且flash的位翻转现象的出现频率较高,在文件存储时容易导致信息出错。

(4)使用寿命方面,Nand Flash一个块最大擦写次数可达百万次,而Nor Flash只有十万次左右。

(5)读写速度方面Nand Flash擦除简单,而Nor Flash擦除前需要先将目标块内的值先写为1,且Nor Flash的块较大,擦除时间较长。

U盘常用的存储器是Nand Flash

U盘常用的存储器是非易失性存储器Nand Flash,然后回答它相比与Nor Flash的优点。

6.2 如何理解嵌入式系统?结合应用谈谈自己的理解

嵌入式系统是以应用为中心,以计算机技术为基础,软硬件可裁剪,适用于应用系统,对功能、可靠性、成本、体积、功耗等有着严格要求的专用计算机系统。

6.3 嵌入式系统的特点

(1)软硬件可裁剪

(2)体积小、低功耗、低成本,高可靠性、高稳定性

(3)实时性和交互性强

(4)对开发环境和人员有一定要求

6.4 S5PV210提供几个32位的定时器,哪几个具备PWM功能?

S5PV210提供5个32位定时器,其中定时器0、1、2、3具备PWM功能,定时器4没有输出引脚,定时器还具有死区寄存器。

6.5 以定时器0为例,说说PWM定时器工作过程

(1)设置预分频器和时钟分频器值

(2)设置TCNTBn定时器初值和TCMPBn比较值,配置TCON寄存器开启定时器,在使能手动更新后,TCNTNBn和TCMPBn的值自动装入定时器内部的TCNTn和TCMPn寄存器

(3)TCNTn开始减一计数,直到和TCMPn的值相等时,在使能自动反转功能后,TOUTn的输出引脚信号反转

(4)TCNTn继续进行减一操作,直到减到0。如果使能中断功能,则触发相应的中断,跳转到相应的中断服务子程序中执行

(5)如果使能自动加载,则TCNTn的值减到0后,会进行自动重装并开始下一次定时操作。若为手动加载,则定时器停止定时。直到装入初值和比较值,会在执行完当前周期后,在下一次时钟周期开始定时操作

6.6 嵌入式设备文件分为哪三类?

(1)字符设备,能够像字节流一样访问的设备,比如文件、串口

(2)块设备,数据以块的形式存放,比如Nand Flash

(3)网络接口,同时具有字符设备和块设备的部分特点

七、实验部分

7.1 Linux交叉编译环境的制作过程

(1)下载交叉编译工具链arm-linux-gcc,并进行解压

(2)启用32位架构,安装32位依赖库

(3)配置环境变量,并确保其生效

(4)输入arm-linux-gcc -v命令,若正确输出版本号,则安装配置成功

7.2 U_Boot移植过程

根据开发板需求从 U-Boot 的官网下载对应的源码,并准备一个容量足够且无重要数据的sd卡,将其格式化为 FAT32 文件系统。

在boards.cfg中添加单板硬件信息,创建板级目录和配置文件,配置相关的硬件相关驱动

执行make <board>_config命令,自动生成配置文件和架构符号链接

通过make命令编译生成spl/u-boot-spl.bin和u-boot.bin,按芯片要求烧录sd卡中(实验中为扇区1和扇区32)

将sd卡插入到开发板上,选择从sd卡启动观察现象是否正常

7.3 U_Boot启动过程

(1)BL0(iROM 阶段):iROM初始化硬件并从SD卡扇区1加载SPL到内部RAM执行;

(2)BL1(SPL 阶段):SPL初始化时钟和DDRAM后,从SD卡扇区32加载完整U-Boot到DDRAM起始地址(0x20000000)执行;

(3)BL2(U-Boot 阶段):U-Boot完成硬件初始化后,执行重定位计算目标地址,将自身代码从加载地址复制到目标地址,根据重定位表修正符号地址,最后跳转到重定位后的 U-Boot 继续执行,准备加载内核。

7.4 驱动设计实验具体过程

在Ubuntu环境下搭建交叉编译环境,禁用系统自带的蜂鸣器驱动以避免冲突(make menuconfig)并编译内核源码。

编写驱动程序buzzer.c、驱动测试代码test.c和对应的Makefile文件。

执行make命令编译生成内核模块buzzer.ko和test可执行文件,并将buzzer.ko与test可执行文件通过tftp命令、sd卡、u盘或其它方式导入开发板。

在开发板上加载好buzzer.ko文件(insmod buzzer.ko),创建字符设备(mknod /dev/buzzer),为test程序添加可执行权限(chmod +x test)并运行test(./test),观察蜂鸣器现象(响起)。

7.5 加载设备驱动程序有几种方法,分别如何实现?

两种加载方式:

(1)静态编译加载,把驱动程序直接编译进内核,开机自动生效,缺点是调试麻烦

(2)动态模块加载:将驱动程序编译为.ko模块文件,通过insmod命令手动添加模块(insert),不需要时使用rmmod命令删除(remove),便于调试,可根据需求进行内核裁剪

如有问题或建议,欢迎在评论区中留言~