四大金刚之计算机组成原理

1. 冯·诺依曼结构有哪些特点?冯·诺依曼结构与哈佛结构的区别?

冯·诺依曼结构总线共用,指令和数据访问不能并行,存在瓶颈;哈佛结构指令总线和数据总线独立,可并行访问,提高效率,但硬件复杂。

特性 | 冯·诺依曼结构 | 哈佛结构 |

内存空间 | 数据和指令 共享内存 | 数据和指令 独立内存 |

总线 | 一条总线访问内存 | 数据总线和指令总线 独立 |

优点 | 节省内存,结构简单 | 数据和指令可并行访问,速度快 |

缺点 | 存在“冯·诺依曼瓶颈” | 设计复杂,占用空间多 |

应用 | 大多数通用计算机 | DSP、嵌入式处理器、信号处理系统 |

2. 计算机的五大组成部分?

计算机的五大组成部分包括:运算器、控制器、存储器、输入设备和输出设备。运算器和控制器统称为 CPU,负责计算与指挥;存储器用于存放程序和数据;输入/输出设备完成与外部环境的信息交互。

3. 原码、反码、补码的定义与转换?为什么用补码?

以 有符号整数 为例(最高位为符号位,0 表示正,1 表示负):

原码(Sign-Magnitude)

直接按照数值的正负写出二进制

正数:与无符号数相同

负数:符号位为 1,数值部分为该数的绝对值二进制

例:+5 → 00000101;-5 → 10000101

反码(One’s Complement)

正数:与原码相同

负数:在原码基础上,符号位不变,数值位逐位取反

例:-5 → 原码 10000101 → 反码 11111010

补码(Two’s Complement)

正数:与原码相同

负数:在反码基础上 +1

例:-5 → 反码 11111010 → 补码 11111011

转换规则总结

原码 → 反码:正数不变,负数符号位不变,数值位按位取反

反码 → 补码:在反码基础上 +1

补码 → 原码:若为正数不变;若为负数,补码先 -1 得到反码,再按位取反

为什么使用补码?

统一加减运算

在补码表示下,减法可以转化为加法:

A - B = A + (-B)硬件只需实现加法器,不需要单独的减法器。

唯一表示零

原码、反码会出现 +0 和 -0 两种表示,补码只有一种 0000...0000。

范围更大

在 n 位二进制中:

原码能表示的范围是 [-(2^(n-1)-1), +(2^(n-1)-1)]

补码能表示的范围是 [-2^(n-1), +(2^(n-1)-1)]

多表示一个负数,1000 0000 被规定为 -128,这是补码设计的一部分,用来保证:

- 编码空间被充分利用

- 只有一个零

- 加减运算统一处理

4. 有符号数 vs 无符号数,定点数 vs 浮点数,浮点数格式 IEEE 754?

类型 | 位数 n | 范围 |

无符号数 (unsigned) | n 位 | 0 ~ 2ⁿ - 1 无符号数:0 ~ 255 |

有符号数 (signed, 补码) | n 位 | -2ⁿ⁻¹ ~ 2ⁿ⁻¹ - 1 有符号数:-128 ~ +127 |

- 定点数(Fixed-point)

- 小数点位置固定

- 数值直接用整数表示,通过约定小数位数来理解

- 适合硬件简单、运算速度快的场景

数值 = 整数部分 × 2^小数位数

例如:2.75 定点表示(保留 2 位小数)→ 275- 浮点数(Floating-point)

- 小数点位置可浮动,由 尾数 + 指数 表示

- 可表示很大或很小的数,精度可控

数值 = (-1)^符号 × 尾数 × 2^指数

32 位:1 位符号 + 8 位指数 + 23 位尾数5. 指令的组成?

指令由 操作码 + 操作数 + 寻址方式 组成,操作码指定操作类型,操作数指明操作对象,寻址方式告诉 CPU 如何访问操作数;部分指令还有额外控制字段。

寻址方式 | 举例 | 说明 |

立即数 |

| 操作数就是值本身 |

直接 |

| 操作数是内存地址,CPU去该地址读/写 |

间接 |

| 操作数的地址存储在寄存器里 |

寄存器 |

| 操作数存储在寄存器里 |

基址+变址 |

| 操作数地址 = R2 + R3 |

- 立即数 → 值直接放在指令里,速度快,灵活性低

- 寄存器 → 值存在寄存器里,速度快,灵活性高

- 内存 → 值存内存里,空间大,访问慢

- 寄存器间接寻址 → 寄存器里存地址,CPU访问内存,兼顾灵活性和空间

6. CISC vs RISC?

CISC → 指令复杂,每条指令可能完成多步操作,所程序指令数以减少,但 CPU 硬件复杂。

RISC → 指令简单,每条指令只做一件事,所以程序指令数增加,但 CPU 可以高速流水线执行,设计简单。

7. 控制器分类?

- 中央处理器控制器(CPU Control Unit)

- 控制 CPU 内部各部分协同工作

- 生成指令控制信号(如取指、译码、执行)

- 可分为:

- 硬连线控制器:用逻辑电路实现固定控制,速度快,但不灵活

- 微程序控制器:用微指令实现控制,灵活,可修改指令集

- I/O 控制器(Peripheral Controller)

- 控制外设与 CPU 或内存的数据传输

- 类型:

- 通用接口控制器:如 USB 控制器

- 专用接口控制器:如硬盘控制器、显示控制器

- 存储器控制器(Memory Controller)

- 控制内存读写操作

- 处理访问冲突、刷新 DRAM 等

8. 指令周期分哪几步?

- 取指(Fetch)

- 从内存取出下一条指令到指令寄存器(IR)

- 程序计数器(PC)+1 或指向下一条指令

- 译码(Decode)

- 将指令寄存器中的指令解析

- 确定操作类型、操作数位置和寻址方式

- 取操作数(Operand Fetch / Read Operands)

- 按寻址方式,从寄存器或内存取出操作数

- 执行(Execute)

- ALU 或控制单元执行指令操作

- 可能是加减乘除、逻辑运算、跳转等

- 写回(Write Back / Store Result)

- 将执行结果写回寄存器或内存

9. 主存与辅存的区别?

特性 | 主存(内存) | 辅存(外存) |

存储介质 | DRAM/SRAM | 磁盘、SSD、光盘等 |

速度 | 高速 | 相对慢,访问延迟大 |

容量 | 较小 | 较大,可存海量数据 |

可直接访问性 | CPU 可直接读写 | CPU 不能直接读写,需要 I/O 控制器 |

易失性 | 易失(断电丢失) | 非易失(断电数据保存) |

用途 | 存储正在执行的程序和数据 | 长期存储程序、数据、文件 |

价格 | 贵 | 相对便宜 |

10. 局部性原理?

时间局部性(Temporal Locality)

最近访问过的数据或指令,很可能在短时间内再次访问

例子:循环变量、频繁调用的函数

空间局部性(Spatial Locality)

当前访问的数据附近的数据,很可能随后也会被访问

例子:数组顺序访问、顺序读取文件

应用

高速缓存(Cache)设计:

利用时间局部性,将最近访问的数据保存在 CPU Cache 中

利用空间局部性,把连续内存块一起加载到 Cache

虚拟内存分页:

页调度策略(如 LRU)利用时间局部性,提高缺页命中率

11. Cache 与主存的映射方式?Cache 命中/不命中后处理?Cache 与主存一致性问题?

Cache 是 CPU 与主存之间的高速缓冲存储器,用于存放近期访问的数据和指令,利用局部性原理提高访问速度,缓解 CPU 与主存速度差距。

a. Cache 与主存的映射方式

映射方式 | 思路 | 优缺点 | 示例 |

直接映射 | 每个主存块只能映射到一个固定的 Cache 行 | 硬件简单,速度快,但冲突多 |

|

全相联 | 主存块可放入 Cache 的任意行 | 冲突少,利用率高,但硬件复杂,需要比较 Tag | 访问时比对 Tag 找行 |

组相联 | 折中方案:Cache 分组,每组多行,主存块映射到组内任意行 | 冲突适中,硬件复杂度中等 |

|

b. Cache 命中/不命中后的处理

- 命中(Hit)

- CPU 直接从 Cache 获取数据

- 访问时间短,性能高

- 未命中(Miss)

- CPU 需要从主存读取数据到 Cache,再访问

- 根据替换策略(FIFO / LRU / LFU 等)选择 Cache 行替换

c. Cache 与主存一致性问题

问题:Cache 中的数据可能更新,但主存未更新,或者多个 Cache 拥有同一主存块,数据可能不同步

- 写策略

- 写直达(Write Through):CPU 写数据时,Cache 和主存同时更新

- 写回(Write Back):CPU 写只更新 Cache,主存延迟更新,减少主存写次数

12. IO的控制方式?

I/O 控制方式主要有三种:

- 程序查询:CPU 轮询设备,效率低

- 中断驱动:设备完成触发中断,CPU 不忙等

- DMA:设备直接访问主存,CPU 只需发起请求和处理完成中断,高效传输大数据

13. DMA VS DRAM VS SRAM?

DMA 是直接内存访问机制,DRAM 是大容量主存,SRAM 是高速缓存。

名称 | 全称 | 类型 | 作用 / 功能 | 特点 |

DMA | Direct Memory Access | 控制方式/机制 | I/O 数据直接在内存和设备之间传输,无需 CPU 参与 | 提高大块数据传输效率,CPU 可并行执行其他任务 |

DRAM | Dynamic RAM | 存储器 | 主存(内存)常用,存储程序和数据 | 容量大、价格低、速度相对慢,需要周期性刷新(易失性) |

SRAM | Static RAM | 存储器 | CPU Cache 常用 | 速度快、不需要刷新(易失性)、容量小、价格高 |

14. 总线分类?总线仲裁方式?总线通信过程?

a. 1️⃣ 总线分类

按用途和功能,总线可以分为:

分类 | 特点 / 作用 |

数据总线(Data Bus) | 传输数据位,双向 |

地址总线(Address Bus) | 传输内存或 I/O 地址,单向 |

控制总线(Control Bus) | 传输控制信号,如读/写、中断请求等 |

系统总线(System Bus) | CPU、内存、I/O 共用,三者复合总线 |

专用总线 | 内部 CPU 总线、DMA 总线、外设总线等 |

b. 2️⃣ 总线仲裁方式(Bus Arbitration)

总线是共享资源,需要仲裁:

- 集中式仲裁(Centralized Arbitration)

- 集中仲裁器控制总线访问

- CPU 或 I/O 设备向仲裁器申请总线

- 分两种:

- 硬件固定优先级:高优先级设备先使用总线

- 旋转优先级(轮询):保证公平性

- 分布式仲裁(Distributed Arbitration)

- 各设备自己协商,总线无单独仲裁器

- 优点:无单点故障

- 缺点:硬件复杂,实现困难

c. 3️⃣ 总线通信过程

以 CPU 读内存/写内存 为例:

- 发出请求

- CPU 将地址放到地址总线

- 控制总线置为读/写信号

- 总线仲裁

- CPU 或设备请求总线

- 仲裁器判断是否允许访问

- 数据传输

- 写操作:CPU → 数据总线 → 内存

- 读操作:内存 → 数据总线 → CPU

- 结束传输

- 释放总线,其他设备可使用

15. CPI、MIPS、MFLOPS 是什么?

- CPI:每条指令平均周期,越小越快

- MIPS:每秒百万条指令数,越大越快

- MFLOPS:每秒百万浮点运算次数,衡量浮点计算能力

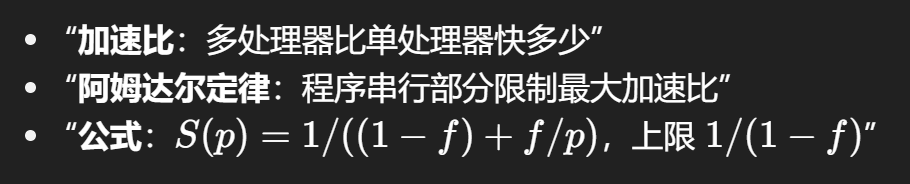

16. 加速比和阿姆达尔定律?

17. 指令流水线

把指令执行分解为多个阶段(如取指、译码、执行、访存、写回),不同指令可以 重叠执行,提高 CPU 吞吐率

18. 计算机的执行速度瓶颈?

- 原因:

- 存储器访问速度慢:CPU 执行速度远快于主存(DRAM)

- 流水线冒险:结构、数据、控制冒险导致停顿

- 缓存未命中:Cache 与主存速度差距大

- 数据搬运:成为限制性能的主要因素

- 外设速度远低于 CPU

- 解决手段:

- 增加 Cache 层次(L1/L2/L3)

- 优化流水线设计与分支预测

- 使用高速寄存器和流水线并行

- 中断驱动:CPU 不忙等

- DMA:直接内存访问

- 异步 I/O:CPU 与 I/O 并行

19. 页表优化手段

- 快表(TLB,Translation Lookaside Buffer):存储最近使用的页表项,加快地址转换

- 多级页表:节省内存空间,如二级/三级页表

- 反向页表:按物理页框索引查找对应进程和逻辑页,节省页表空间

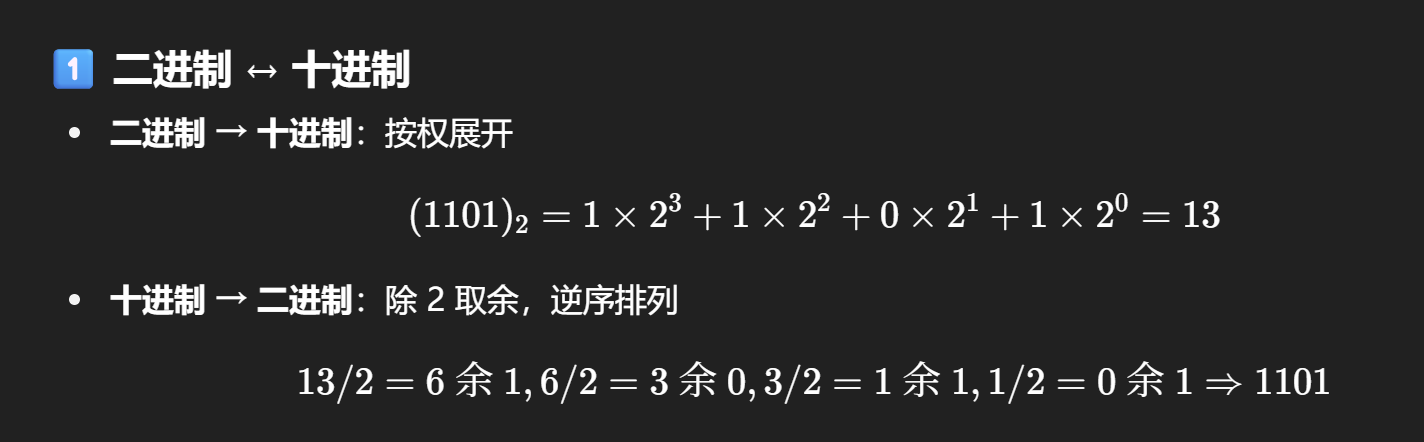

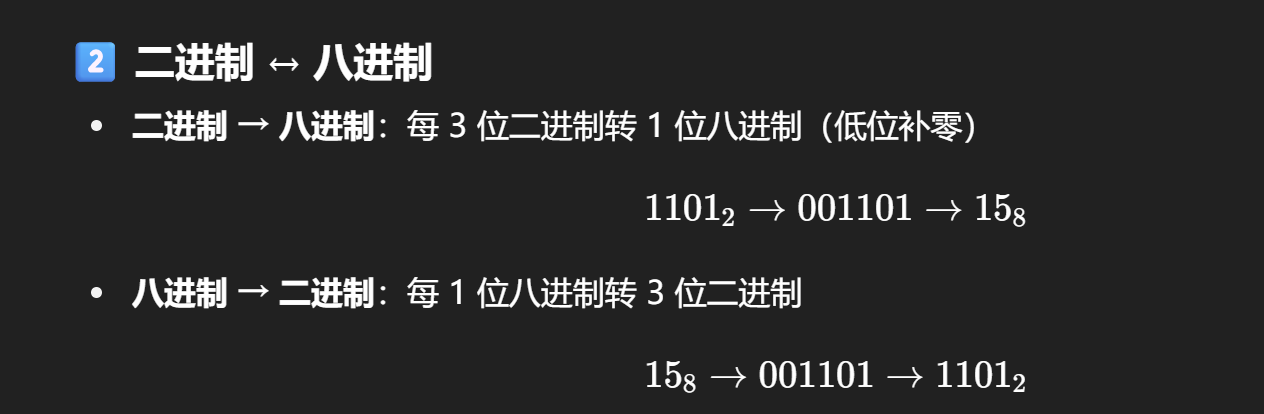

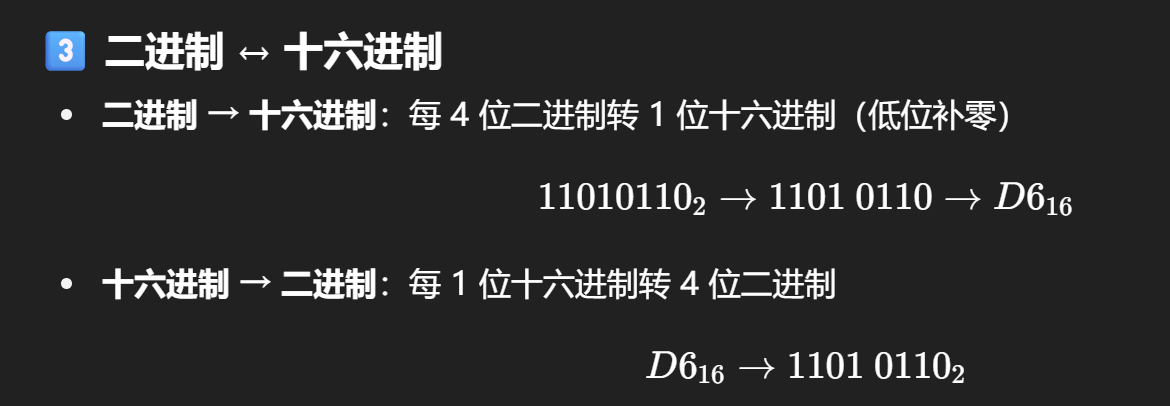

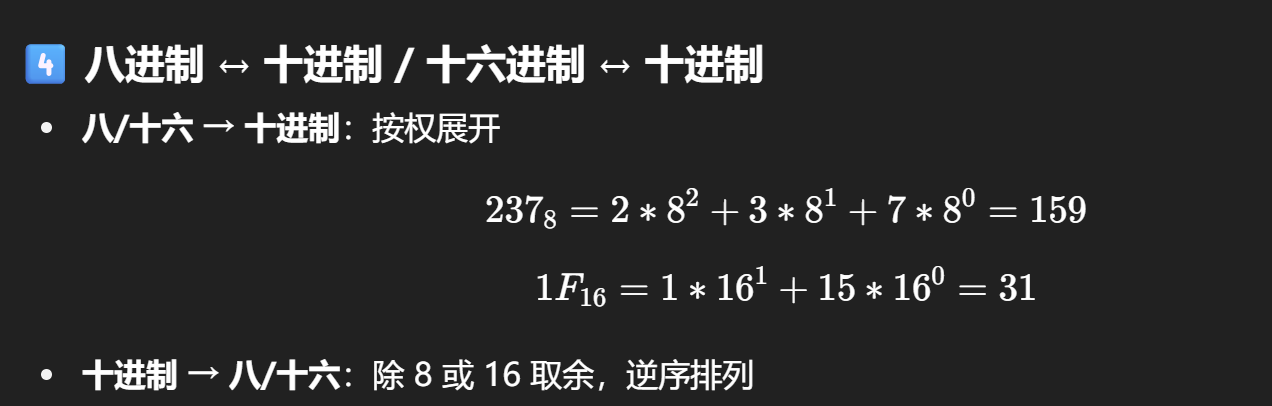

20. 进制转换

- 二进制是核心,八/十六进制转二进制最方便

- 权展开法:二/八/十/十六 → 十进制

- 除基取余法:十进制 → 二/八/十六

- 牢记 二↔八 每 3 位一组,二↔十六 每 4 位一组