ARM 体系结构

一、计算机系统基础

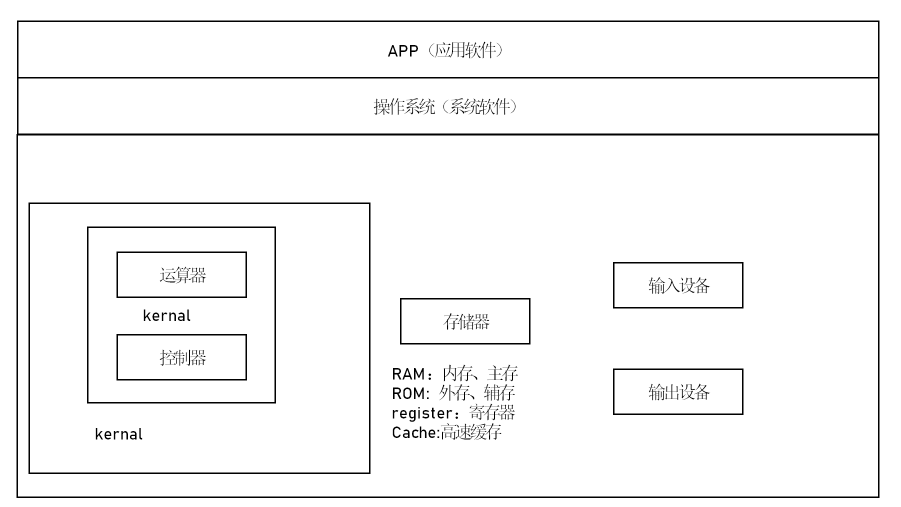

(一)软件组成

- 系统软件:为计算机提供基础运行环境,如操作系统(Windows、Linux 等)。

- 应用软件:满足特定应用需求,如办公软件(Word、Excel)、游戏等。

(二)硬件组成

硬件是计算机系统的物理载体,遵循 “冯・诺依曼体系” 核心框架,由五大核心部件组成:

运算器(Arithmetic Logic Unit, ALU)

- 功能:执行算术运算(加、减、乘、除、模运算)和逻辑运算(与、或、非、异或、比较运算)。

- 特点:是 CPU 的核心运算单元,运算速度直接决定计算机的计算性能。

控制器(Control Unit, CU)

- 功能:协调计算机各部件同步工作,控制指令执行流程(如指令预取、译码、执行的时序控制)。

- 特点:相当于计算机的 “大脑中枢”,通过产生控制信号(如时钟信号、读写信号)指挥硬件操作。

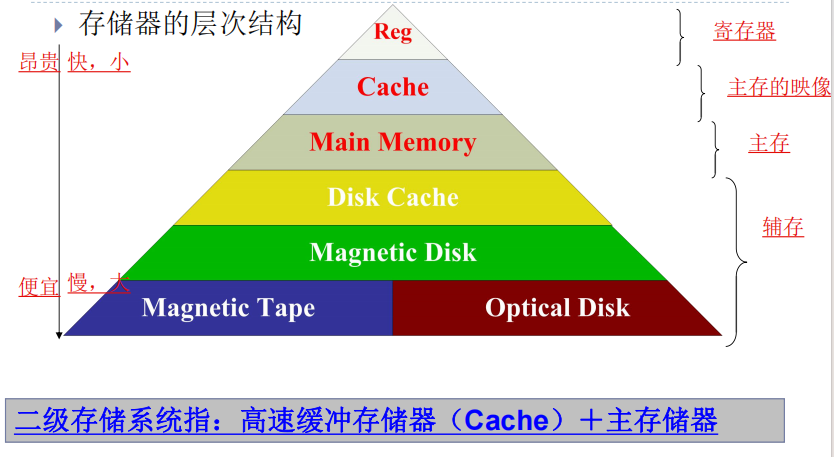

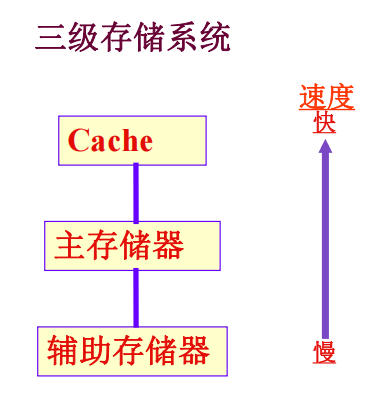

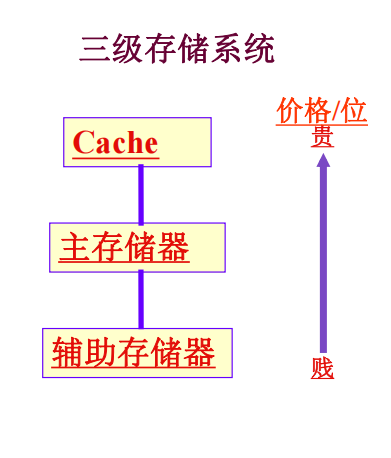

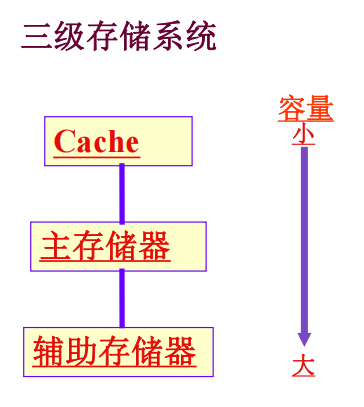

存储器(Memory)

- 功能:存储程序代码和数据,按速度、容量、用途分为多级存储(详见 “第二章 存储器分类”)。

输入设备(Input Device)

- 功能:将外部信息(如用户操作、物理信号)转换为计算机可识别的电信号。

- 常见类型:键盘(Keyboard)、鼠标(Mouse)、扫描仪(Scanner)、传感器(Sensor,如温度传感器 DS18B20)、触摸屏(Touch Screen)。

输出设备(Output Device)

- 功能:将计算机处理后的电信号转换为人类可感知的信息(如视觉、听觉)或物理动作。

- 常见类型:显示器(Monitor)、打印机(Printer)、音箱(Speaker)、电机(Motor)、LED 指示灯(LED Indicator)。

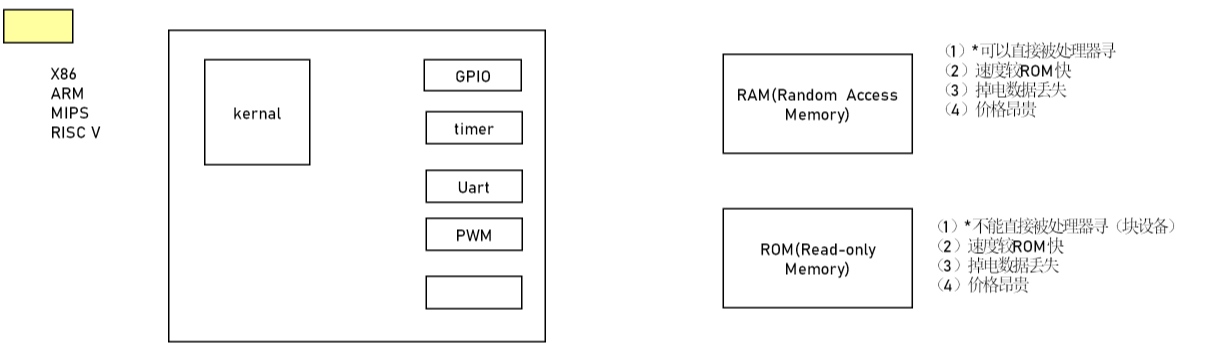

二、存储器分类

| 类型 | 英文全称 | 核心特性 | 应用场景 |

|---|---|---|---|

| 寄存器(Register) | CPU Internal Register | 1. 位于 CPU 内部,速度最快(纳秒级,ns); 2. 容量极小(通常几十到几百字节); 3. 临时存储指令执行过程中的数据 / 地址; 4. 按功能分通用寄存器、特殊功能寄存器。 | CPU 内部数据临时缓存,如 PC(程序计数器)、SP(栈指针)。 |

| 高速缓存(Cache) | High-Speed Cache Memory | 1. 位于 CPU 与主存之间,速度次之(纳秒级,~10ns); 2. 容量较小(KB 到 MB 级,如 256KB、4MB); 3. 缓存 CPU 频繁访问的指令 / 数据,减少主存访问延迟; 4. 分 I-Cache(指令缓存)、D-Cache(数据缓存)。 | CPU 与主存之间的 “缓冲”,提升指令执行效率。 |

| 随机存取存储器(RAM) | Random Access Memory | 1. 即主存 / 内存,速度中等(纳秒级,~100ns); 2. 容量较大(MB 到 GB 级,如 4GB、16GB); 3. 可读写,掉电后数据丢失; 4. 可直接被 CPU 寻址(按字节寻址); 5. 分为 DRAM(动态 RAM,如 DDR4)、SRAM(静态 RAM,速度快但成本高)。 | 运行中的程序代码、临时数据存储,如操作系统加载、应用程序运行。 |

| 只读存储器(ROM) | Read-Only Memory | 1. 即外存 / 辅存,速度较慢(微秒级,μs); 2. 容量大(GB 到 TB 级,如 512GB SSD、2TB HDD); 3. 非易失性(掉电数据不丢失); 4. 早期仅可读,现多为可擦写(如 Flash ROM、EEPROM); 5. 不能直接被 CPU 寻址(需通过块设备驱动访问)。 | 长期存储操作系统镜像、应用程序安装包、用户文件,如 SSD、U 盘、嵌入式设备的 Flash。 |

三、处理器体系

处理器是计算机的 “运算核心”,按应用领域分为通用计算机处理器和嵌入式处理器两大类。

(一)通用计算机处理器

面向 PC、服务器等场景,强调通用计算能力:

中央处理器(CPU)

- 英文全称:Center Processing Unit

- 定位:通用计算核心,类比 “公司 CEO”(脑力劳动者),负责指令执行、数据运算、系统资源调度。

- 代表产品:Intel Core i7/i9、AMD Ryzen 7/9、服务器级 Intel Xeon、AMD EPYC。

图形处理器(GPU)

- 英文全称:Graphics Processing Unit

- 定位:专用于图形渲染和并行计算,类比 “公司体力劳动者”,擅长大规模并行数据处理。

- 核心功能:3D 图形渲染、视频编码 / 解码、AI 模型训练(如深度学习)。

- 代表产品:NVIDIA GeForce RTX 4090、AMD Radeon RX 7900 XT、NVIDIA A100(数据中心级)。

浮点运算单元(FPU)

- 英文全称:Floating-Point Unit

- 定位:CPU 或 GPU 内部的专用模块,负责浮点型数据(带小数点的数,如 3.14、0.618)的运算。

- 重要性:提升科学计算、工程模拟、图形渲染等场景的效率,早期 CPU 无 FPU,需通过软件模拟(效率低),现主流 CPU 均集成 FPU。

(二)嵌入式领域处理器

面向嵌入式系统(如家电、工业控制器、智能设备),强调低功耗、高集成度、特定场景性能:

| 类型 | 英文全称 | 核心特性 | 应用场景 | 代表产品 |

|---|---|---|---|---|

| 微处理器(MPU) | Micro Processing Unit | 1. 偏向 “数据处理”,强调通用计算能力; 2. 需外接内存(RAM)、存储(ROM)、外设; 3. 性能较强,支持复杂操作系统(如 Linux)。 | 智能设备、工业控制主机,如智能家居网关、车载信息娱乐系统。 | NXP I.MX6ULL、Samsung S5PV210 |

| 微控制器(MCU) | Micro Control Unit | 1. 偏向 “控制”,强调高集成度; 2. 片上集成 RAM、ROM、GPIO、UART 等外设,“单芯片即可工作”; 3. 低功耗、低成本,支持 RTOS 或裸机编程。 | 小型嵌入式控制,如家电控制板(空调、洗衣机)、传感器节点、智能门锁。 | STM32F103、Atmel ATmega328P(Arduino 核心) |

| 数字信号处理器(DSP) | Digital Signal Processing Unit | 1. 专为 “高强度数字信号运算” 设计,支持快速乘法 - 累加(MAC)操作; 2. 适合处理时序信号(如音频、视频、雷达信号); 3. 指令集优化并行运算,实时性强。 | 音频处理(如降噪、均衡器)、视频编码、工业检测(如振动分析)、医疗设备(如心电图处理)。 | Texas Instruments TMS320C6000、ADI ADSP - SHARC |

| 片上系统(SoC) | System on Chip | 1. 集成 “处理器核心 + 外设 + 存储 + 专用模块” 的完整系统,类比 “城市蓝图”; 2. 可集成 MPU/MCU/DSP/GPU/Modem(调制解调器)等,减少外部元件; 3. 高集成度、小体积,适合便携设备。 | 智能手机、平板电脑、智能手表、物联网网关,如手机 SoC(高通骁龙 8 Gen3、华为麒麟 9000S)。 | Qualcomm Snapdragon 8 Gen3、Apple A17 Pro、NXP i.MX8M Plus |

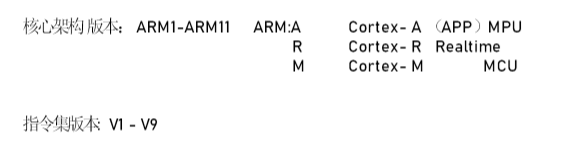

四、ARM 架构与内核

ARM(Advanced RISC Machines)架构是嵌入式领域主流架构,基于 RISC 设计,具有低功耗、高性能的特点。

(一)ARM 开发板与芯片

典型 ARM 架构型号

- Cortex - A 系列:面向高性能应用(如智能手机、平板),如 Cortex - A7、Cortex - A53、Cortex - A78。

- Cortex - R 系列:面向实时性场景(如工业控制、汽车电子),如 Cortex - R5、Cortex - R8。

- Cortex - M 系列:面向低成本、低功耗 MCU(如传感器、小型控制器),如 Cortex - M0、Cortex - M4、Cortex - M7。

主流 SoC 芯片

- NXP(恩智浦):I.MX6ULL(Cortex - A7,工业控制)、I.MX8M Plus(Cortex - A53,多媒体)。

- Samsung(三星):S5PV210(Cortex - A8,早期嵌入式开发)。

- STMicroelectronics(意法半导体):STM32MP157(Cortex - A7 + Cortex - M4,异构多核)。

常用开发板

- 正点原子(ALIENTEK):I.MX6ULL - Mini 开发板(基于 NXP I.MX6ULL,适合 Linux 嵌入式开发)、STM32F4 探索者开发板(Cortex - M4,MCU 开发)。

- 友善之臂(FriendlyARM):Tiny4412 开发板(三星 S5PV210,ARM 9 架构学习)。

- Arduino:Uno 开发板(Atmel ATmega328P,Cortex - M0 内核,入门级 MCU 开发)。

(二)处理器架构分类(Processor Architecture Types)

处理器架构分为 RISC 和 CISC 两大类,另有开源架构 RISC - V 崛起:

| 架构类型 | 英文全称 | 指令集特点 | 优势 | 劣势 | 典型代表 |

|---|---|---|---|---|---|

| 复杂指令集架构(CISC) | Complex Instruction Set Computer | 1. 指令数量多(数百条),功能复杂(一条指令可完成多步操作,如 “复制内存块”); 2. 指令长度不固定(1 - 15 字节); 3. 寻址方式多样(如寄存器间接寻址、基址变址寻址)。 | 1. 程序代码短(少指令完成复杂操作); 2. 编译器设计简单(无需拆分复杂操作); 3. 早期内存容量小时优势明显。 | 1. 硬件控制电路复杂(难流水线化); 2. 指令执行效率低(部分指令需多个时钟周期); 3. 功耗高、芯片面积大。 | Intel x86 系列(Core i3/i5/i7)、AMD x86 系列(Ryzen) |

| 精简指令集架构(RISC) | Reduced Instruction Set Computer | 1. 指令数量少(几十到上百条),功能精简(一条指令仅完成一个基本操作,如 “加法”“取数”); 2. 指令长度固定(如 32 位); 3. 寻址方式简单(多为寄存器寻址、立即数寻址); 4. 大部分指令单时钟周期完成。 | 1. 硬件控制电路简单(易实现流水线); 2. 指令执行效率高(并行性强); 3. 低功耗、芯片面积小(适合嵌入式)。 | 1. 程序代码长(复杂操作需多条指令组合); 2. 编译器设计复杂(需优化指令组合)。 | ARM 系列(Cortex - A/R/M)、MIPS 系列(路由器) |

| 开源精简指令集架构(RISC - V) | RISC - V Instruction Set Architecture | 1. 基于 RISC 设计,指令集开源(无专利费); 2. 模块化设计(可按需扩展指令集,如浮点、向量运算模块); 3. 支持 32 位 / 64 位 / 128 位地址空间。 | 1. 开源免费(降低芯片设计成本); 2. 灵活可扩展(适配不同场景,从 MCU 到服务器); 3. 社区活跃(生态快速发展)。 | 1. 生态成熟度低于 ARM/x86(部分外设驱动缺失); 2. 高端芯片产品较少。 | 平头哥玄铁 910、SiFive U74、兆易创新 GD32V 系列 |

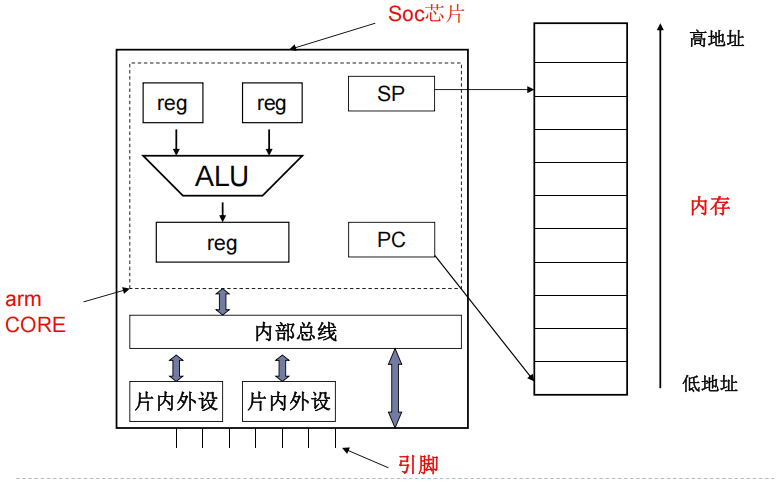

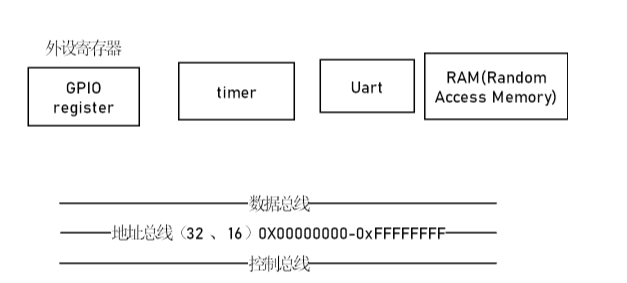

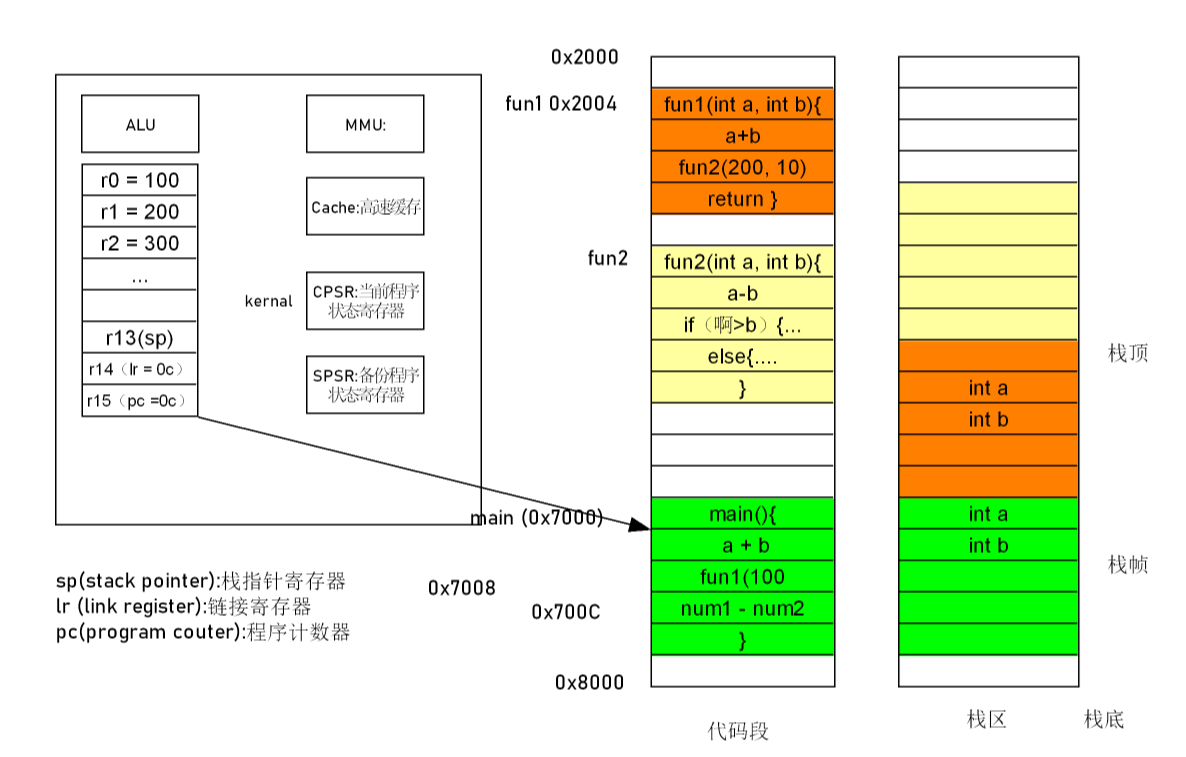

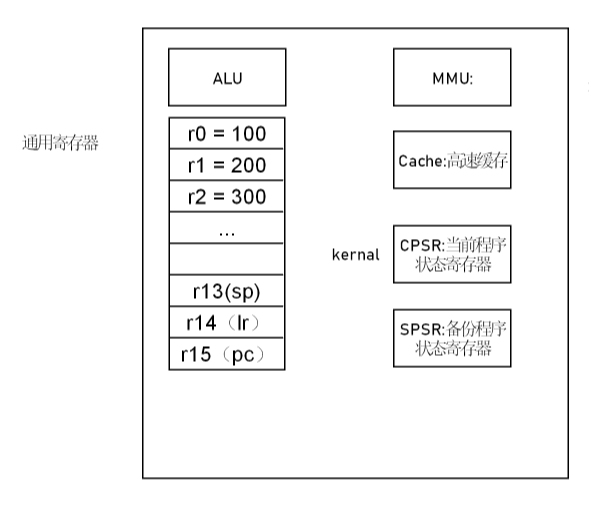

(三)ARM 内核核心组件(ARM Kernel Core Components)

ARM 内核是 ARM 处理器的 “核心运算单元”,包含以下关键模块:

算术逻辑单元(ALU)

功能:执行算术运算(加、减、乘、除、移位)和逻辑运算(与、或、非、异或、比较),是内核的 “运算引擎”。

寄存器组(Register Bank)

分类:

1.特殊功能寄存器(Special Function Registers,SFRs):

- PC(Program Counter,程序计数器):指向当前要执行的指令地址,决定程序执行流程。

- SP(Stack Pointer,栈指针):指向栈顶地址,管理函数调用时的栈空间(如局部变量、返回地址存储)。

- LR(Link Register,链接寄存器):保存函数调用后的返回地址,避免返回地址丢失。

- CPSR(Current Program Status Register,当前程序状态寄存器):记录当前程序运行状态,如进位标志(C)、溢出标志(V)、中断屏蔽位(I/F)、处理器模式位(M [4:0])。

- SPSR(Saved Program Status Register,备份程序状态寄存器):异常发生时(如中断、复位),备份 CPSR 的值,异常处理完成后恢复 CPSR。

2.通用寄存器(General-Purpose Registers,GPRs):如 R0 - R12,用于临时存储数据和地址。

指令译码器(Instruction Decoder)

功能:将从内存或 I-Cache 中取出的指令(机器码)翻译成内核可执行的控制信号(如 “加法操作”“取数操作”)。

控制器(Control Unit)

功能:根据指令译码器的控制信号,协调 ALU、寄存器、总线等部件同步工作,控制指令执行时序(如 “取指→译码→执行” 的节奏)。

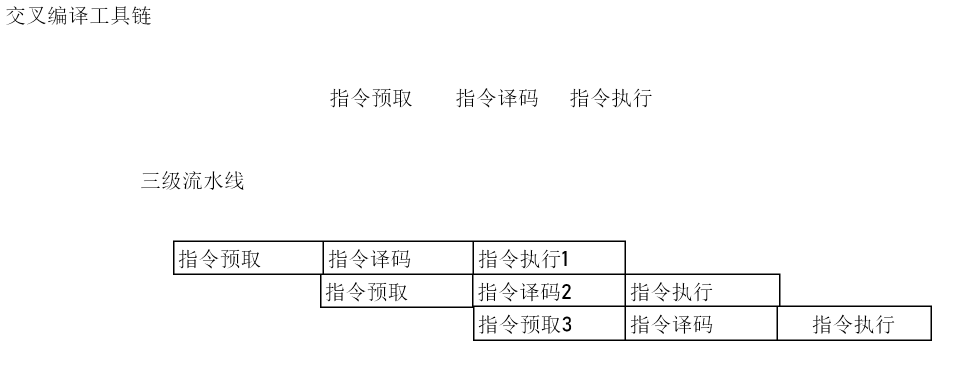

流水线(Pipeline)

ARM 内核典型流水线结构:

- 三级流水线(早期 ARM 内核,如 ARM7TDMI):分为 “指令预取(Fetch)→ 指令译码(Decode)→ 指令执行(Execute)” 三个阶段:

指令预取(Fetch):从 I-Cache 或内存中读取下一条要执行的指令,存入流水线寄存器,为后续译码做准备;

指令译码(Decode):指令译码器将预取的机器码指令,翻译成 ALU、寄存器等部件能识别的控制信号(如 “将 R1 与 R2 相加”“从内存地址 0x1234 取数据”);

指令执行(Execute):控制器根据译码后的控制信号,驱动 ALU 完成运算、寄存器读写或内存访问,输出指令执行结果。

- 五级流水线(中高端 ARM 内核,如 ARM926EJ-S):在三级基础上拆分 “执行” 阶段,增加 “内存访问(Memory)” 和 “写回(Writeback)”,形成 “取指→译码→执行→访存→写回”:

执行(Execute):仅完成 ALU 运算或地址计算(如计算内存访问地址);

内存访问(Memory):若指令需要读写内存(如加载 / 存储指令),此阶段完成数据与内存的交互(从内存取数据到寄存器,或把寄存器数据写入内存);

写回(Writeback):将 ALU 运算结果或内存读取的数据,写回目标通用寄存器(如把加法结果存入 R3)。

五、扩展问题

1.冯.诺伊曼架构和哈佛架构有何区别?ARM内核属于哪一种?

- 冯诺依曼架构

存储结构:程序指令和数据共享同一条总线、同一个存储空间。

工作特点:在执行指令时,需要先从存储器中取出指令,再取出数据进行操作,指令和数据的访问存在时序上的冲突,总线带宽成为性能瓶颈。

- 哈佛架构

存储结构:程序指令和数据分别存储在不同的存储空间,有各自独立的总线。

工作特点:可以同时获取指令和数据,大大提高了数据吞吐率,适合对实时性要求高的场景。

ARM 内核既可以采用冯・诺伊曼架构,也可以采用哈佛架构。例如,早期的 ARM7TDMI 采用冯・诺伊曼架构;而 ARM9 及以后的很多内核(如 ARM926EJ - S)采用哈佛架构,通过独立的指令总线和数据总线,提高了指令执行和数据访问的并行性。

2.ARM有几种工作模式?

ARM有7个基本工作模式:

User:非特权模式,大部分任务执行在这种模式

FIQ:当一个高优先级(fast)中断产生时将会进入这种模式

IRQ:当一个低优先级(normal)中断产生时将会进入这种模式

Supervisor当复位或软中断指令执行时将会进入这种模式

Abort:当存取异常时将会进入这种模式

Undef:当执行未定义指令时会进入这种模式

System:使用和User模式相同寄存器集的特权模式

Cortex-A特有模式:Monitor:是为了安全而扩展出的用于执行安全监控代码的模式;也是一种特权模式

3.什么是异常向量表?

异常向量表是内存中一块固定的地址区域,其中存放着各种异常处理程序的入口地址(或跳转到处理程序的指令)

工作原理:当CPU发生异常(如中断、复位、执行未定义指令等)时,它会自动切换到对应的工作模式,并将程序计数器(PC)指向向量表中一个固定的、与异常类型对应的地址,从这个地址取出指令开始执行,从而跳转到真正的异常处理程序。

在ARM中的位置:传统上,向量表位于内存地址0x00000000(或在高地址0xFFFF0000,可通过协处理器配置)。表中的每个条目占用4字节(32位ARM),正好存放一条跳转指令。

ARM的异常向量表通常包含以下条目(按固定顺序排列):

地址(通常) | 异常类型 | 进入的工作模式 |

|---|---|---|

0x00000000 | 复位(Reset) | 管理模式(SVC) |

0x00000004 | 未定义指令(Undefined Instruction) | 未定义模式(Undef) |

0x00000008 | 软件中断(SWI/SVC) | 管理模式(SVC) |

0x0000000C | 指令预取中止(Prefetch Abort) | 中止模式(Abort) |

0x00000010 | 数据访问中止(Data Abort) | 中止模式(Abort) |

0x00000014 | 保留(Reserved) | 保留 |

0x00000018 | IRQ(外部中断请求) | IRQ模式 |

0x0000001C | FIQ(快速中断请求) |