UCIE Specification详解(十一)

文章目录

- 5 Electrical Layer (2D and 2.5D)

- 5.1 Interoperability

- 5.1.1 Data rates

- 5.1.2 Reference Clock (REFCLK)

- 5.2 Overview(概述)

- 5.2.1 Interface Overview(接口概述)

- 5.2.2 Electrical summary

- 5.3 Transmitter Specification

- 5.3.1 Driver Topology

- 5.3.2 Transmitter Electrical parameters

- 5.3.3 24 GT/s and 32 GT/s Transmitter Equalization

- 5.4 Receiver Specification

- 5.4.1 Receiver Electrical Parameters

- 5.4.2 Rx Termination

- 5.4.3 24 and 32 GT/s Receiver Equalization

- 5.5 Clocking

- 5.5.1 Track

- 5.6 Supply noise and clock skew

- 5.7 Ball-out and Channel Specification

- 5.7.1 Voltage Transfer Function(电压传输函数)

- 5.7.2 Advanced Package

- 5.7.2.1 Loss and Crosstalk Mask

- 5.7.2.2 x64 Advanced Package Module Bump Map

- 5.7.2.3 x32 Advanced Package Module Bump Map

- 5.7.2.4 x64 and x32 Advanced Package Module Interoperability

- 5.7.2.5 Module Naming of Advanced Package Modules

- 5.7.3 Standard Package

- 5.7.3.1 x16 Standard Package Module Bump Map

- 5.7.3.2 x8 Standard Package Module Bump Map

- 5.7.3.3 x16 and x8 Standard Package Module Interoperability

- 5.7.3.4 Module Naming of Standard Package Modules

- 5.7.3.4.1 Module Degrade Rules

- 5.7.4 UCIe-S Sideband-only Port

- 5.8 Tightly Coupled Mode

- 5.9 Interconnect redundancy Remapping

- 5.9.1 Advanced Package Lane Remapping

- 5.9.2 Standard Package Lane remapping

- 5.10 BER requirements, CRC and retry

- 5.11 Valid and Clock Gating

- 5.12 Electrical Idle

- 5.13 Sideband signaling

- 5.13.1 Sideband Electrical Parameters

- 5.13.2 Auxiliary Clock (AUXCLK)

- 6 UCIe-3D

- 6.1 Introduction(介绍)

- 6.2 UCIe-3D Features and Summary

- 6.3 UCIe-3D Tx, Rx, and Clocking

- 6.4 Electrical Specification

- 6.4.1 Timing Budget

- 6.4.2 ESD and Energy Efficiency

- 6.4.3 UCIe-3D Module and Bump Map

- 6.4.4 Repair Strategy

- 6.4.5 Channel and Data Rate Extension

5 Electrical Layer (2D and 2.5D)

5.1 Interoperability

电气规格的关键属性包括:

支持4、8、12、16、24 和32 GT/s 的数据速率

支持高级和标准封装互连

支持时钟和电源门控机制

单端单向数据信号

直流耦合的点对点互连

用于发送抖动Track 的转发时钟

模块内匹配长度的互连设计

先进封装的Tx 驱动强度控制和未端接的Rx

标准封装的Tx 端接以及取决于数据速率和通道范围的Rx 端接5.1 Interoperability(互操作性)

5.1.1 Data rates

设备必须支持4 GT/s 以及4 GT/s 到最高支持数据速率之间的所有数据速率。例如,支持16 GT/s 的设备也必须支持4、8 和12 GT/s 的数据速率。

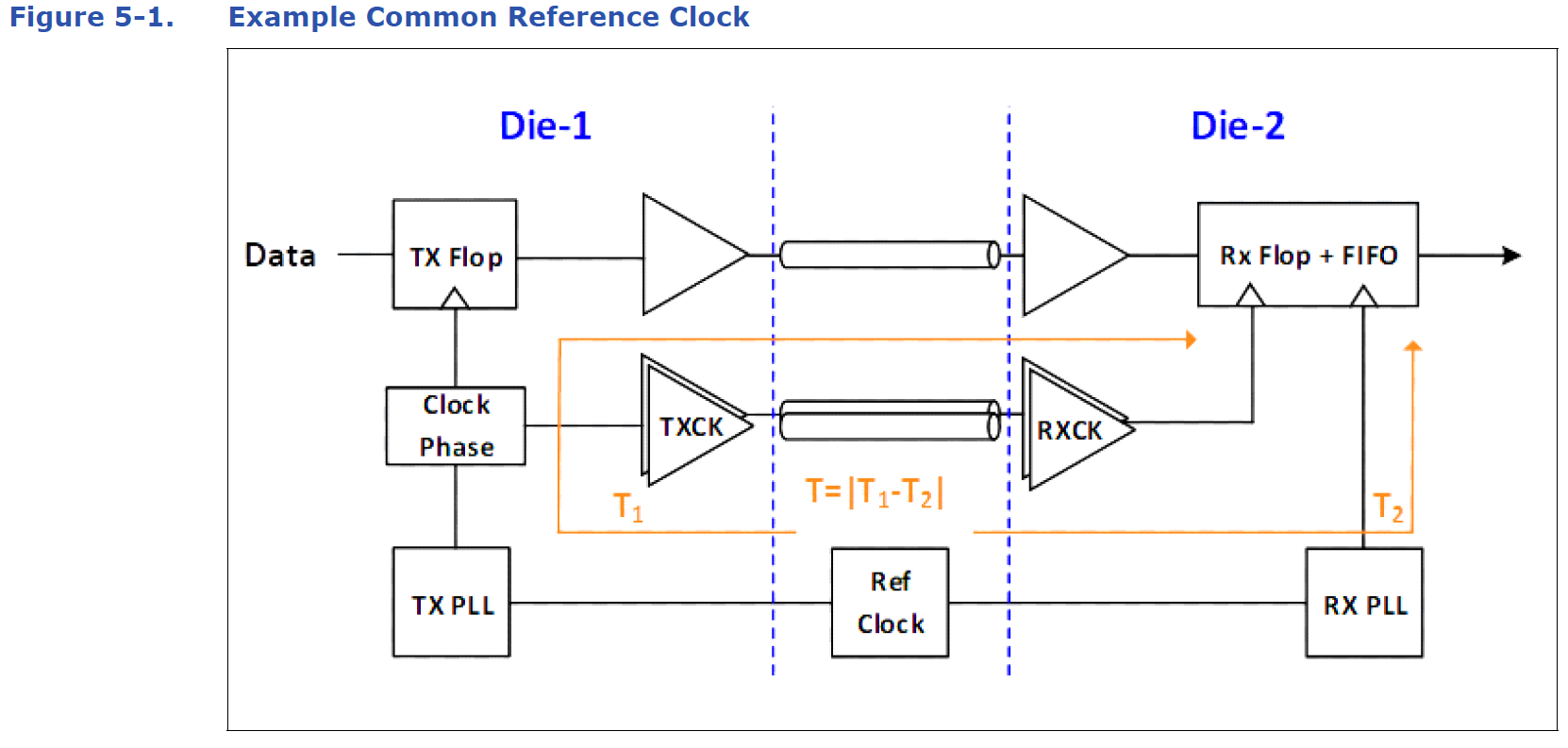

允许扩频时钟(Spread-Spectrum Clocking,SSC)。UCIe 链路发送器和相应的UCIe 链路伙伴的接收器之间需要公共参考时钟(REFCLK),传输延迟差小于5ns,以限制FIFO 深度并将延迟影响降至最低。对于重定时器用例,“Local UCIe Link connection”应使用公共REFCLK,而“Off-Package Link connection”不需要使用或共享公共REFCLK。图5-1 显示了传输延迟差,并且对于Die 的UCIe 链路连接的两个方向是对称的。传输延迟表示发送器数据到接收器数据锁存器与在接收器的FIFO 输出数据锁存器处看到的时钟之间的延迟差。有关REFCLK 的详细信息,请参见第5.1.2 节。

实现说明

在典型的实现中,UCIe 链路发送器的LCLK 和相应链路伙伴接收器的LCLK 均由公共参考时钟生成。在图5-1 的示例实现中,Die-1 中发送器的LCLK 可以由TX PLL 生成,Die-2 中接收器的LCLK 可以由RX PLL 生成。

5.1.2 Reference Clock (REFCLK)

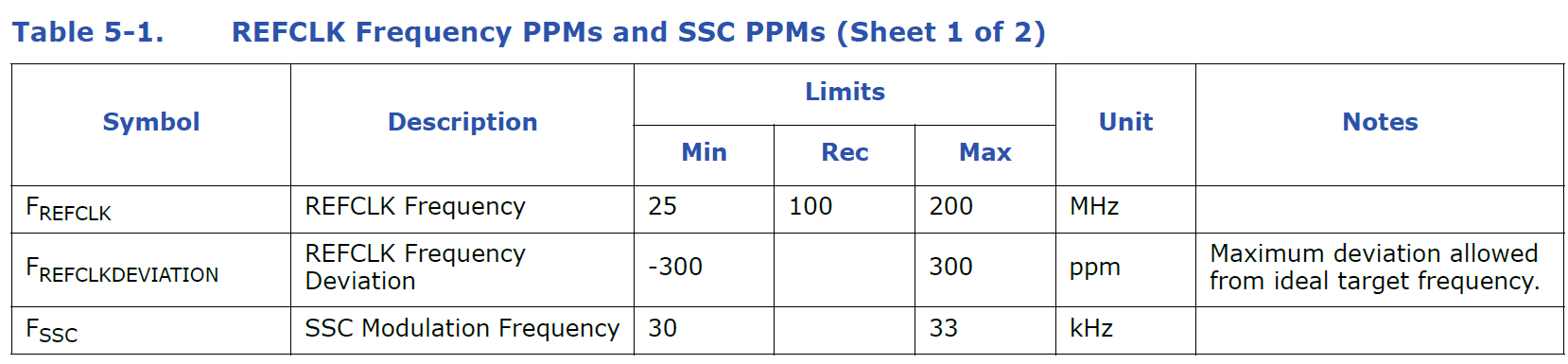

公共参考时钟(REFCLK)使用单个源,该源分配给发送器和接收器。时钟可以从封装引脚提供,也可以由封装上的另一个Die 转发。在任何一种情况下,同一条链路上两个Die 所使用的参考时钟必须来自同一个时钟源。尽管其他参考时钟也是可能的,但建议每个芯粒都使用100 MHz 的参考时钟,包括来自同一时钟源但具有不同参考时钟值的两个Die。表5-1 列出了允许的参考时钟频率范围。表中列出的最小和最大频率表示限制,并不表示需要支持整个频率范围。实现时需要为使用参考时钟的支持数据速率生成精确的I/O 时钟频率。请注意,如果I/O 时钟频率是参考时钟频率的精确整数倍(如果不同于100 MHz),这是可能的。参考时钟在低功率状态下可能被禁用(如在其他标准和规范中所做的那样)。

5.2 Overview(概述)

5.2.1 Interface Overview(接口概述)

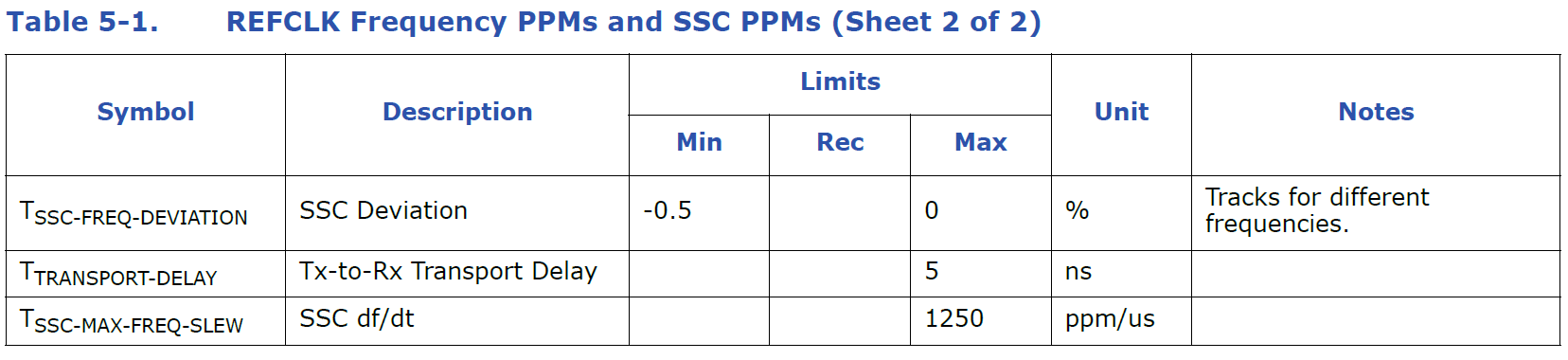

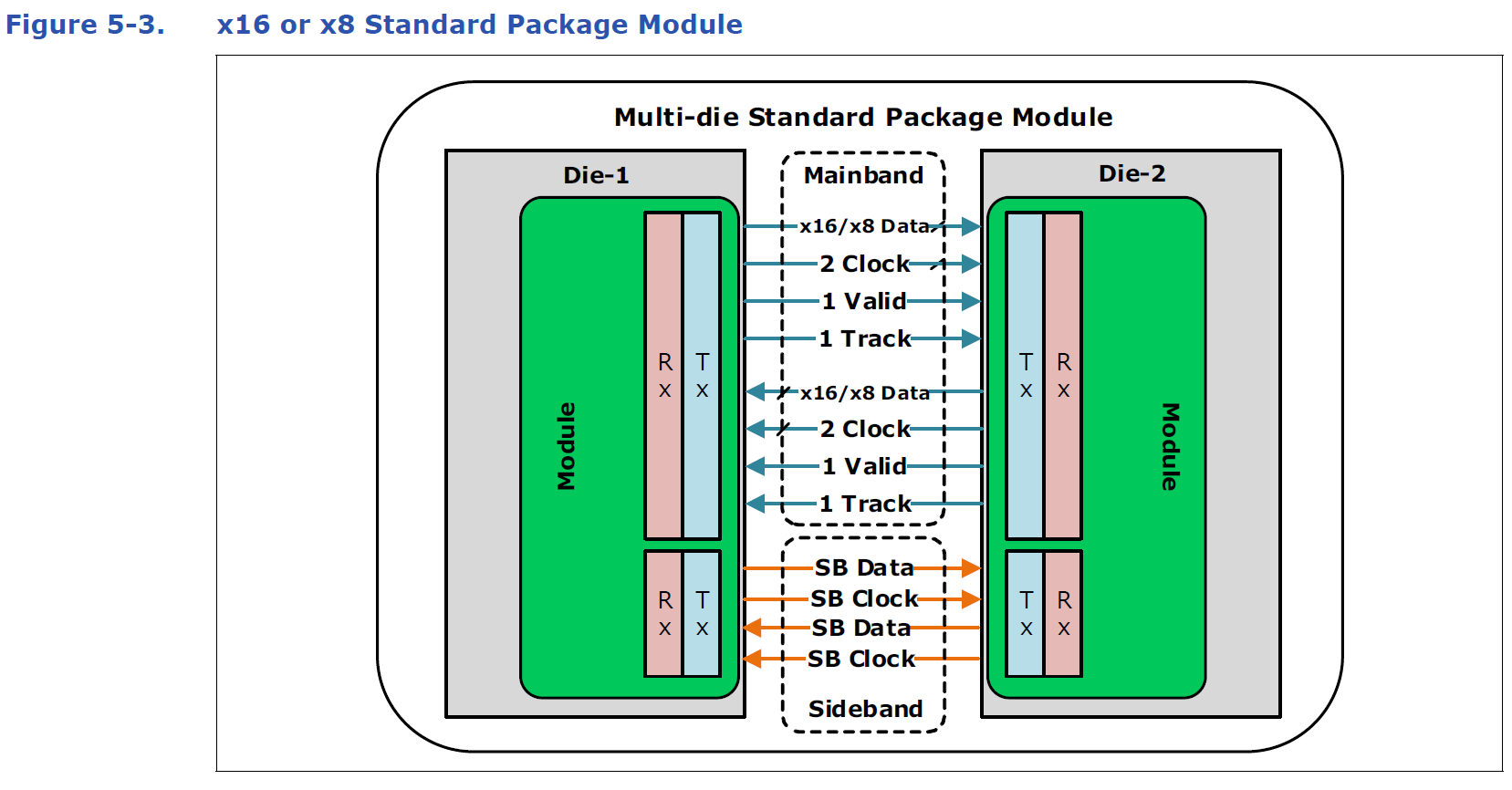

UCIe PHY 的高层框图如图5-2 和图5-3 所示。UCIe 物理接口由称为模块的构建块组成。使用先进封装技术(例如,EMIB、CoWoS)的模块称为“先进封装模块”(Advanced Package Module),分别由一对时钟、用于x64 或x32 先进封装模块的64 或32 个单端数据通道、每个方向(发送和接收)的数据有效通道和Track 通道组成。有一个用于初始化、链路训练和配置读/写的低速边带总线。边带在两个方向(发送和接收)都由单端边带数据线和单端边带时钟线组成。

x16 或x8“标准封装模块”(Standard Package Module)使用间距较大的传统标准封装。标准封装模块由一对时钟、16 或8 个单端数据线、每个方向(发送和接收)的数据有效通道和Track 通道组成。有一个低速边带总线用于初始化、链路训练和配置读/写。边带在两个方向(发送和接收)均由一个单端边带数据线和单端边带时钟线组成。

对于某些应用,多个模块(2 个或4 个)可以聚合以提供额外的带宽。

为避免可靠性问题,建议将发送器输出高电平(VOH)限制在接收Die 的接收器前端电路电源轨以上最大100 mV。当VOH 高于接收器电源轨100 mV 以上时,可在接收器中实现过压保护电路。

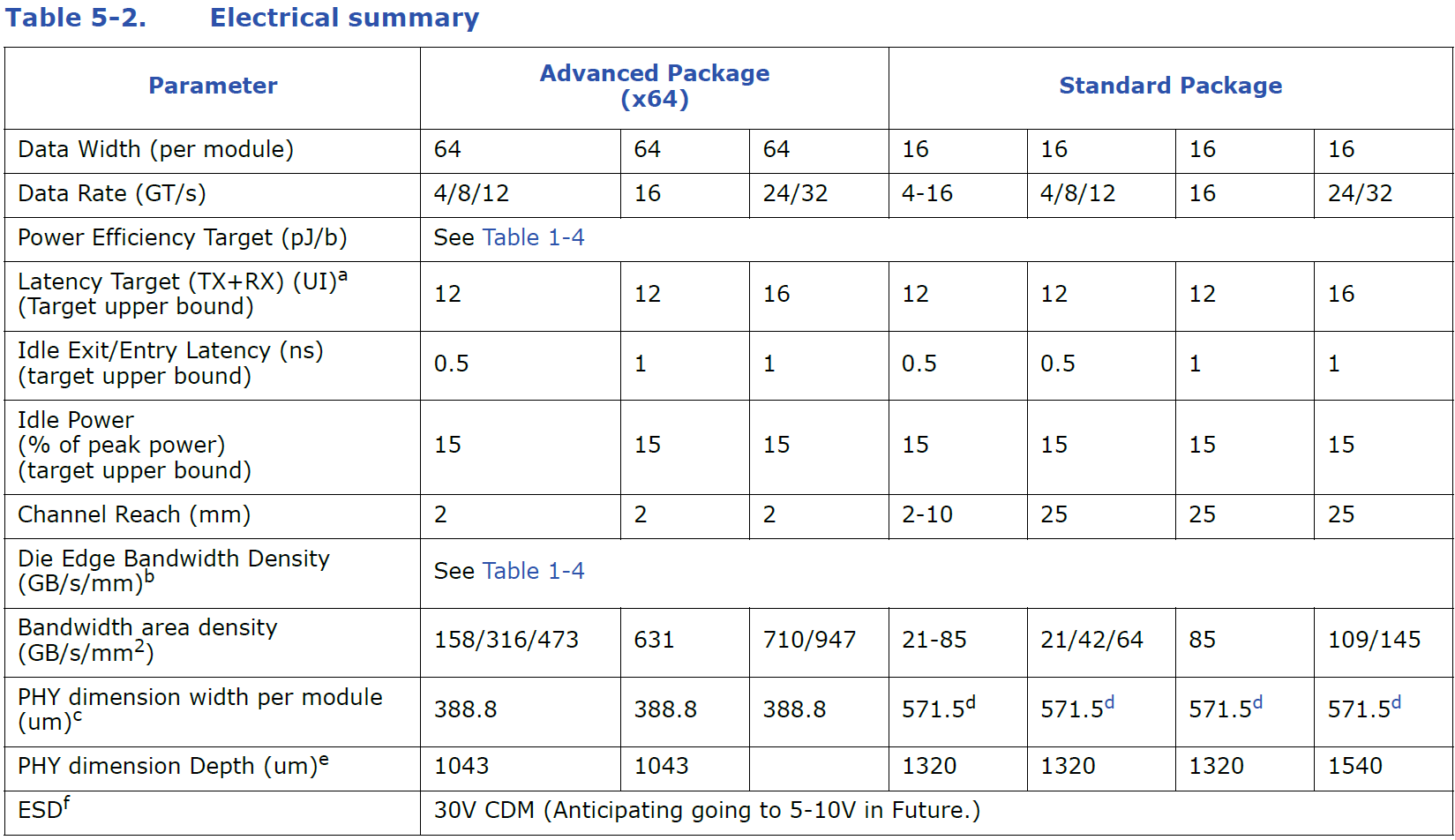

5.2.2 Electrical summary

表5-2 定义了UCIe 设备的PHY 电气特性。

a. 电PHY 延迟目标。有关总体延迟目标,请参见表1-4。

b. 见表1-4。

c. 为了兼容,PHY 大小宽度必须符合先进封装的规格。标准封装的PHY 大小宽度的容差可以更高,因为布线灵活性更大。为了获得最佳通道性能,建议宽度接近规格。

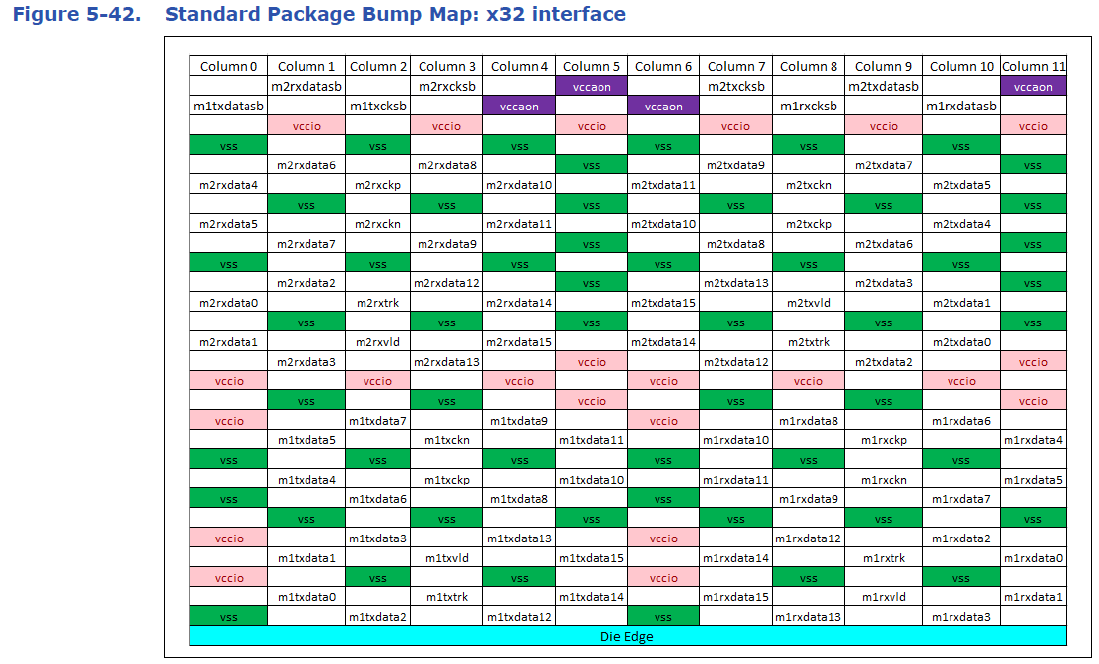

d. 标准封装PHY 大小宽度是基于x32 接口的一个(x16)模块的有效宽度(见图5-42 和图5-43)。

e. PHY 大小深度是一个信息性参数,取决于凸块间距。表中的数字基于10 列x64 Advanced封装的45 um 凸块间距和标准封装的100 um 凸块间距。有关10 列、16 列和8 列凸块矩阵结构中x64 和x32 Advanced Package 模块组合的PHY 大小深度的信息值,请参见第5.7.2 节。

f. 参考(Industry Council on ESD Target Levels):White Paper 2: A Case for Lowering Component-level CDM ESD Specifications and Requirements。

5.3 Transmitter Specification

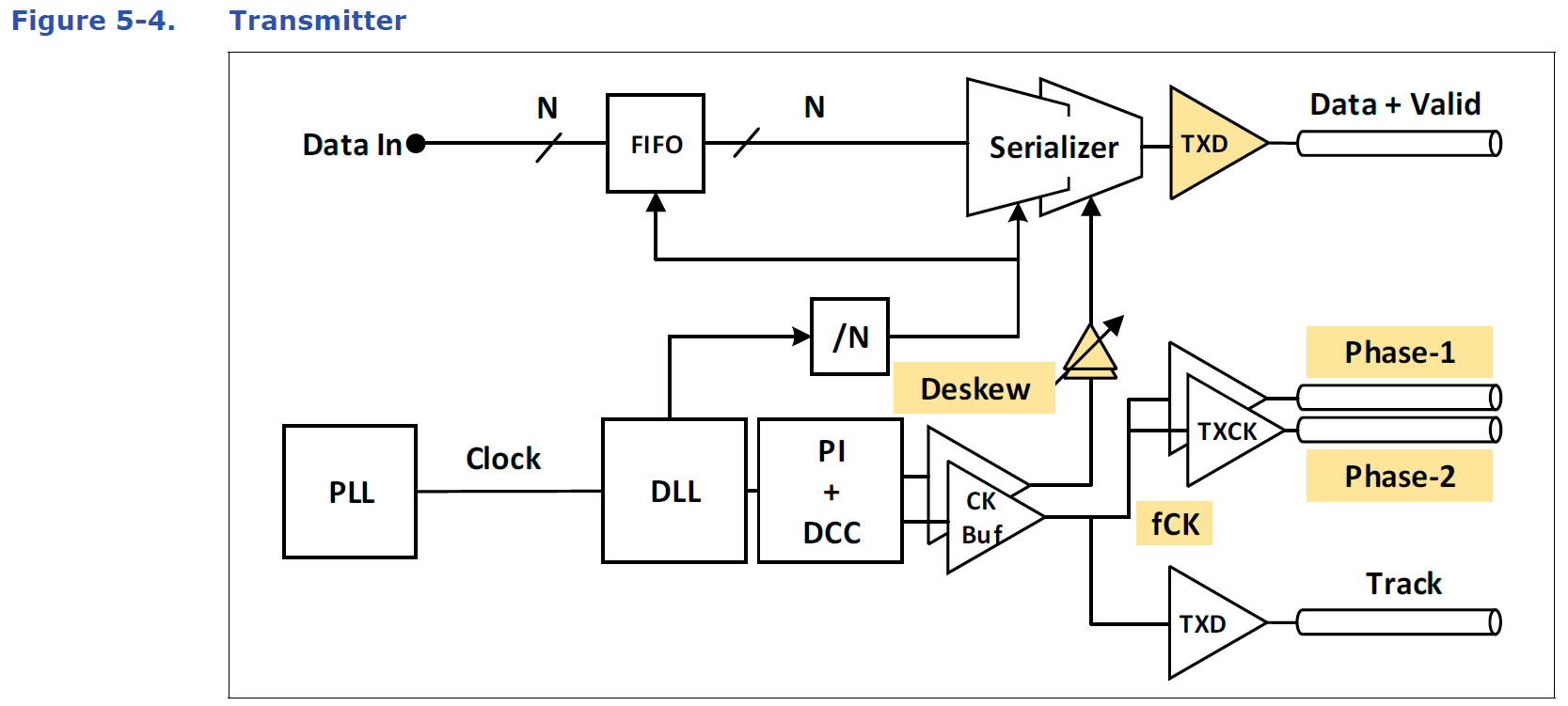

发送器拓扑如图5-4 所示。每个数据模块由N 个单端数据发送器加一个Valid 信号组成。对于x64 先进封装模块,N 为68(64 个数据+ 4 个冗余数据)。对于x32 先进封装模块,N为34(32 个数据+ 2 个冗余数据)。对于x16 标准封装模块,N 为16。对于x8 标准封装模块,N 为8。每个模块中有一对用于时钟的发送器和一个Track 信号。时钟速率和相位在5.5 节中详细讨论。

Valid 信号用于选通到所有数据线的时钟分配,以实现快速空闲退出和进入。该信号还用于有效成帧,详情见第4.1.2 节。有效信号的发送器实现预计与常规数据相同。

Track 信号可用于PHY 以补偿诸如电压或温度之类的缓慢变化变量。Track 是类似于数据位的单向信号。当通过边带被UCIe 模块伙伴为其Track 接收器请求时,UCIe 模块在其Track发送器上发送与转发时钟信号的相位1 对齐的时钟模式(1010…)。有关运行时重新校准步骤的更多详细信息,请参见第4.6 节;有关Track 使用的信息,请参见第5.5.1 节。

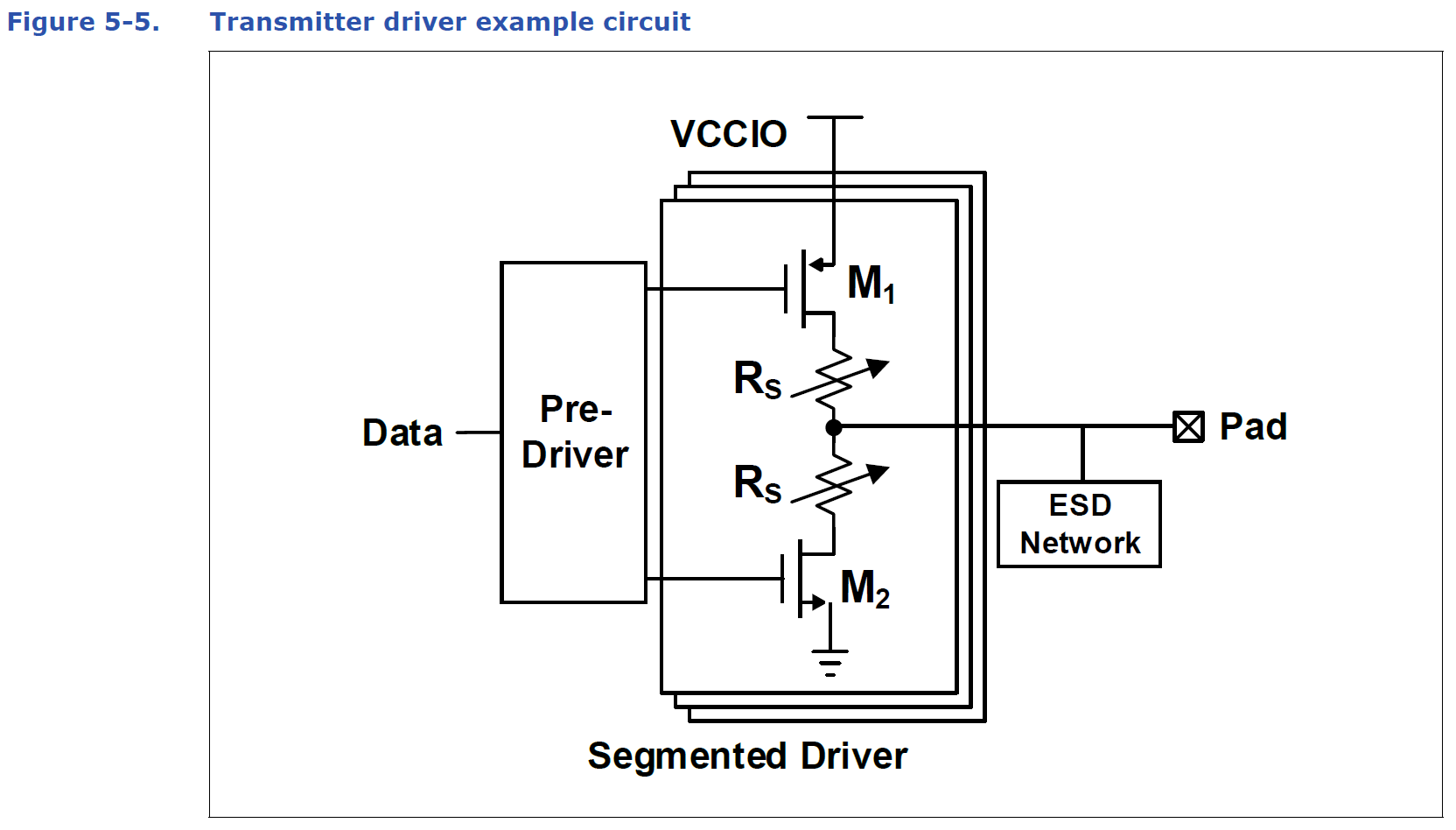

5.3.1 Driver Topology

发送器针对简单性和低功耗运行进行了优化。低功耗发送器驱动器的示例如图5-5 所示。允许有单独的上拉和下拉网络强度,以在不同的通道配置中实现最佳性能。

建议使用控制环路或训练来调整输出阻抗,以补偿工艺、电压和温度的变化。控制环路和训练是特定于实现的,超出了本规范的范围。在低功率状态下,实现必须能够将输出设置为三态。

建议优化ESD 网络以最小化焊盘电容。在更高的数据速率下可能需要诸如T 型线圈之类的电感峰值技术。

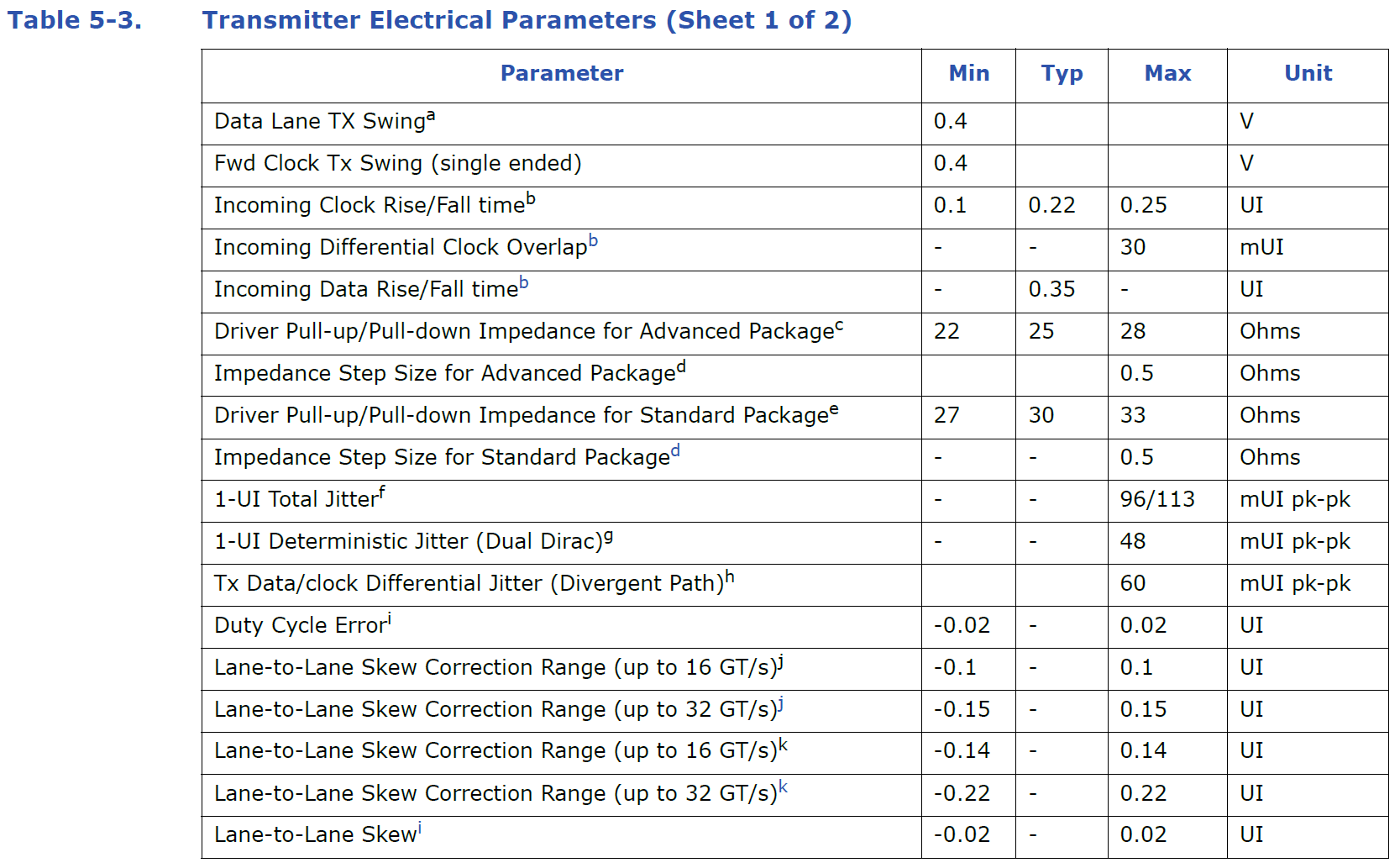

5.3.2 Transmitter Electrical parameters

表5-3 定义了发送器电气参数。

a. 有关推荐的最大发送器电压,请参阅第1.5 节。

b. 预期输入(参考信息)。测量20% 至80% 。差分时钟重叠是与理想差分相位(相隔180度)的偏差。

c. 驱动器上拉/下拉阻抗在发送器信号摆幅的中点进行校准。

d. 阻抗步长是一个参考参数,并且可以根据具体实现来满足驱动器上拉/下拉阻抗。e. 驱动器上拉/下拉阻抗在发送器信号摆幅的中点进行校准(在适用时带有标称的Rx 端接)。f. 在误码率1E-15/1E-27 时。

g. 不包括占空比误差的数据相关抖动。

h. 包括绝对随机抖动和由于延迟失配(在匹配架构中)导致的发散路径的未Track 确定性抖动。

i. 后校正。

j. 先进封装。

k. 标准封装。

l. 包括静态和跟踪误差。

m. 参考参数。相位调整步长必须选择以满足其他定时参数,包括时钟到平均数据训练精度、通道间偏斜和占空比误差(如适用)。

n. 有效焊盘电容先进封装。

o. 有效焊盘电容标准封装。

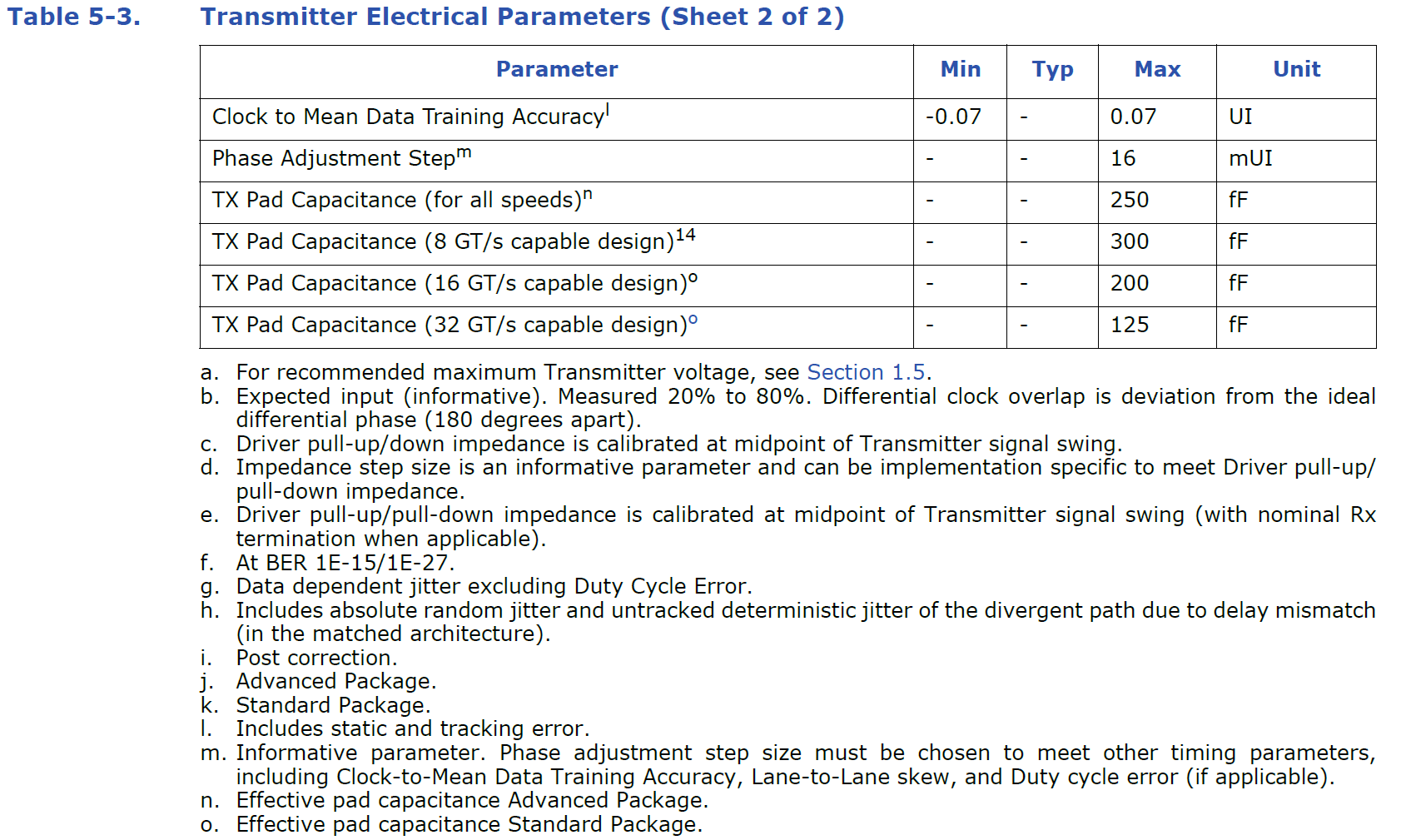

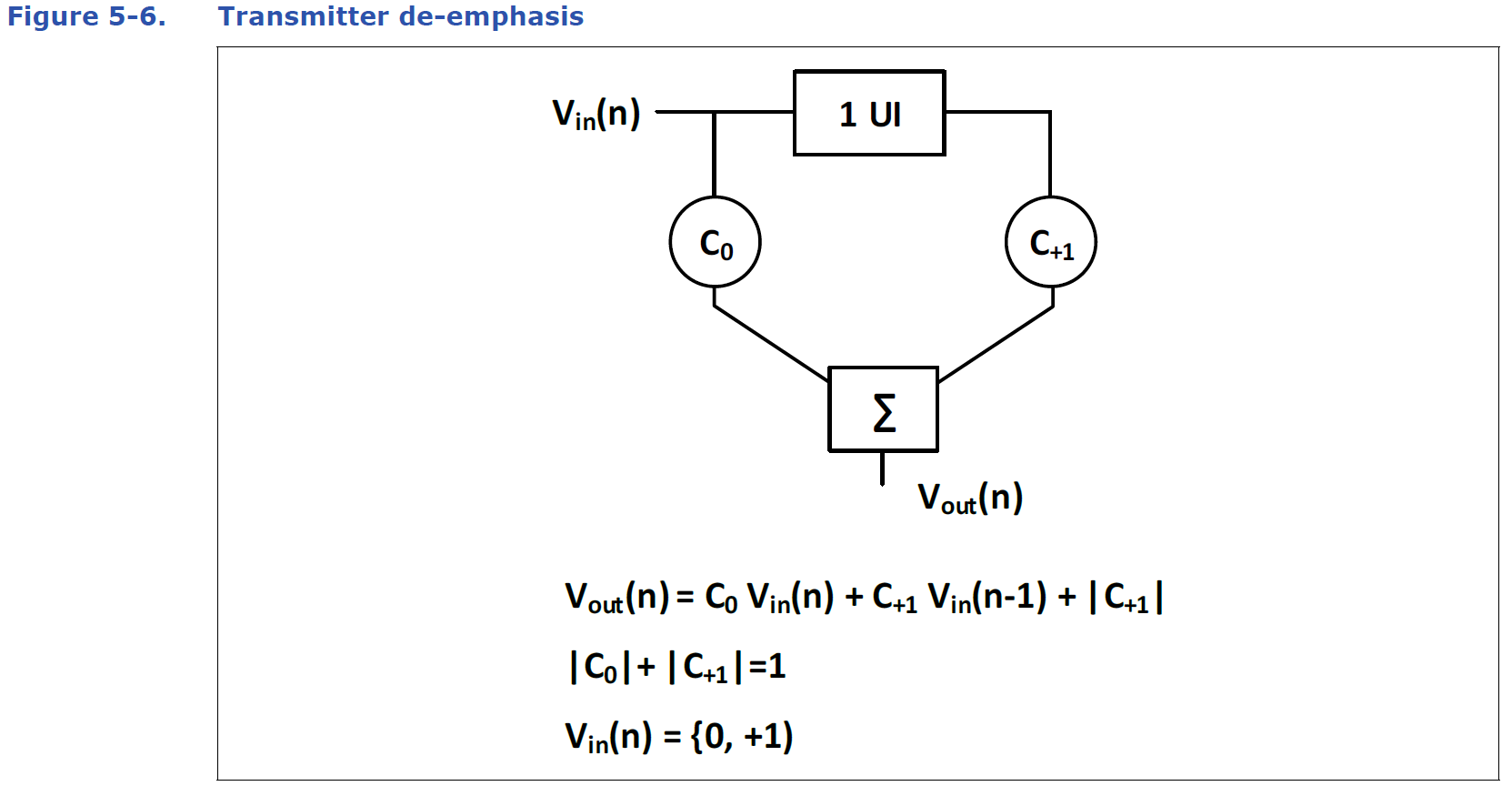

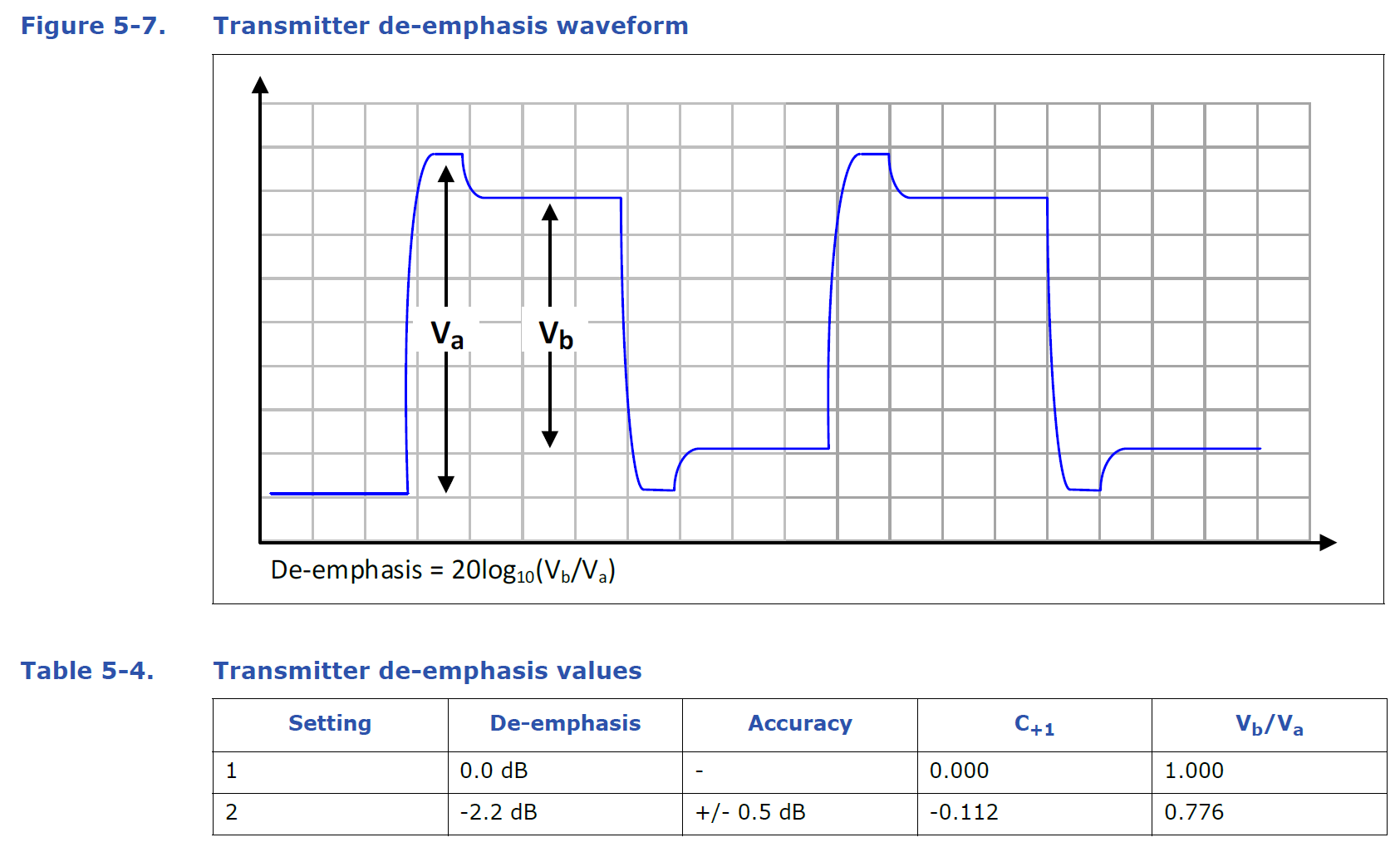

5.3.3 24 GT/s and 32 GT/s Transmitter Equalization

对于16 GT/s,建议使用发送器均衡,并且在24 GT/s 和32 GT/s 数据速率下必须支持,以减轻通道的ISI 影响。对于所有适用的数据速率,Tx 均衡仅为去加重。

24 GT/s 和32 GT/s 的Tx 均衡系数基于图5-6 所示的FIR 滤波器。均衡系数受最大单位摆幅约束。

发送器必须支持表5-4 所示的均衡设置。去加重设置的确定基于初始配置或训练序列,将选择眼开度较大的值。

5.4 Receiver Specification

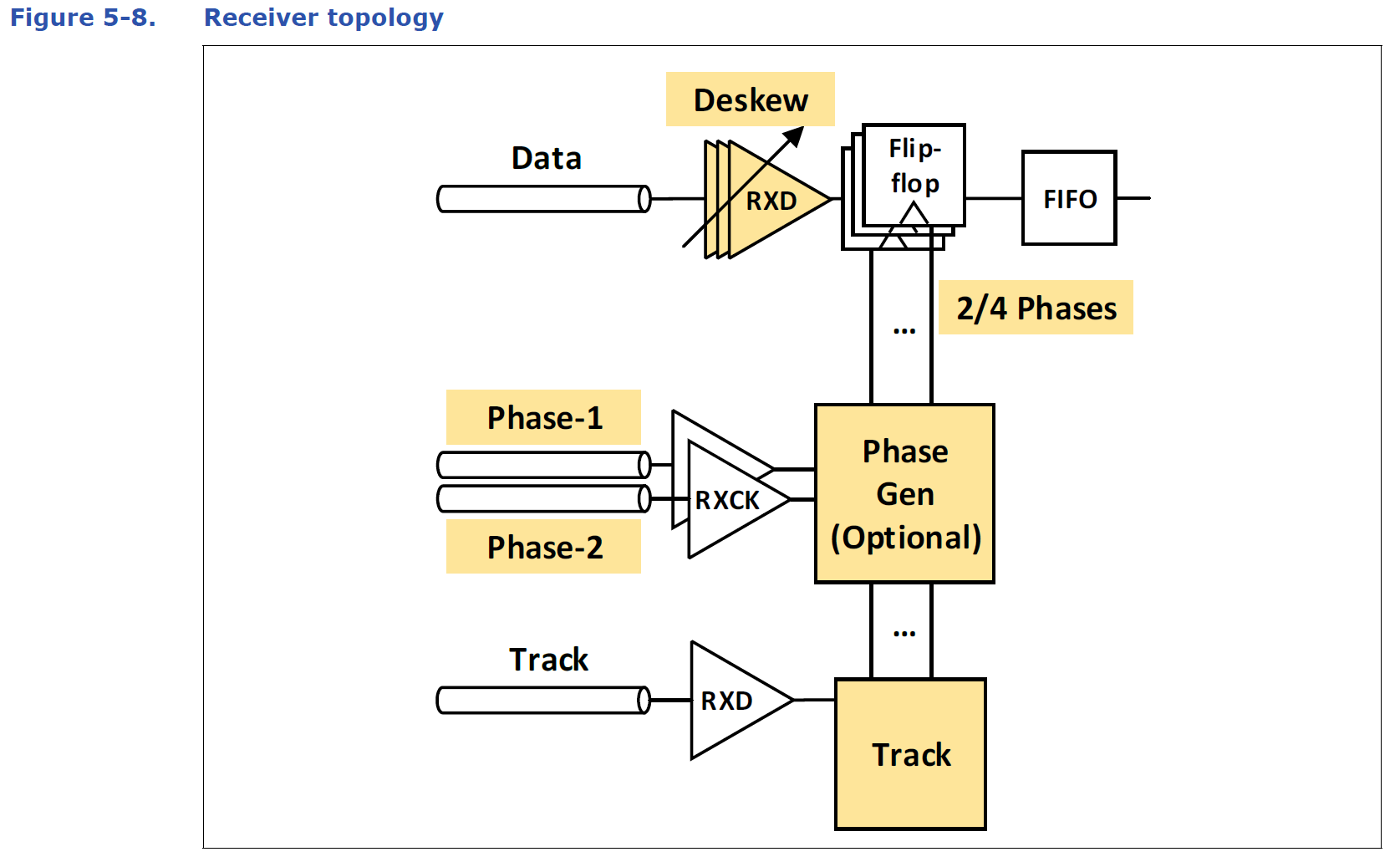

接收器拓扑如图5-8 所示。每个模块(先进封装和标准封装)由Clock 接收器、Data 接收器和Track 接收器组成。

接收时钟用于对输入数据进行采样。接收器必须使时钟路径与Data/Valid 路径到采样器之间的延迟相匹配。这是为了将电源噪声引起的抖动影响降至最低。Data 接收器可以实现为2路或4 路交错。对于4 路交错实现,接收器需要从转发时钟的两个相位在内部生成所需的相位。这可能需要接收器具有占空比校正能力。支持的转发时钟频率和相位在第5.5 节中描述。

在更高的数据速率下,接收器中可能需要去偏斜能力以实现数据通道之间的匹配要求。适用时,接收器去偏斜可在主带训练期间执行。更多细节在第4.5 节中提供。

UCIe 模块在请求Track 信号时,在其Track 接收器上从UCIe 模块伙伴的Track 发送器接收与转发时钟信号的相位1 对齐的时钟模式(1010…),并且可以使用Track 信号来跟踪缓慢变化的电压和温度变化对采样相位的影响。

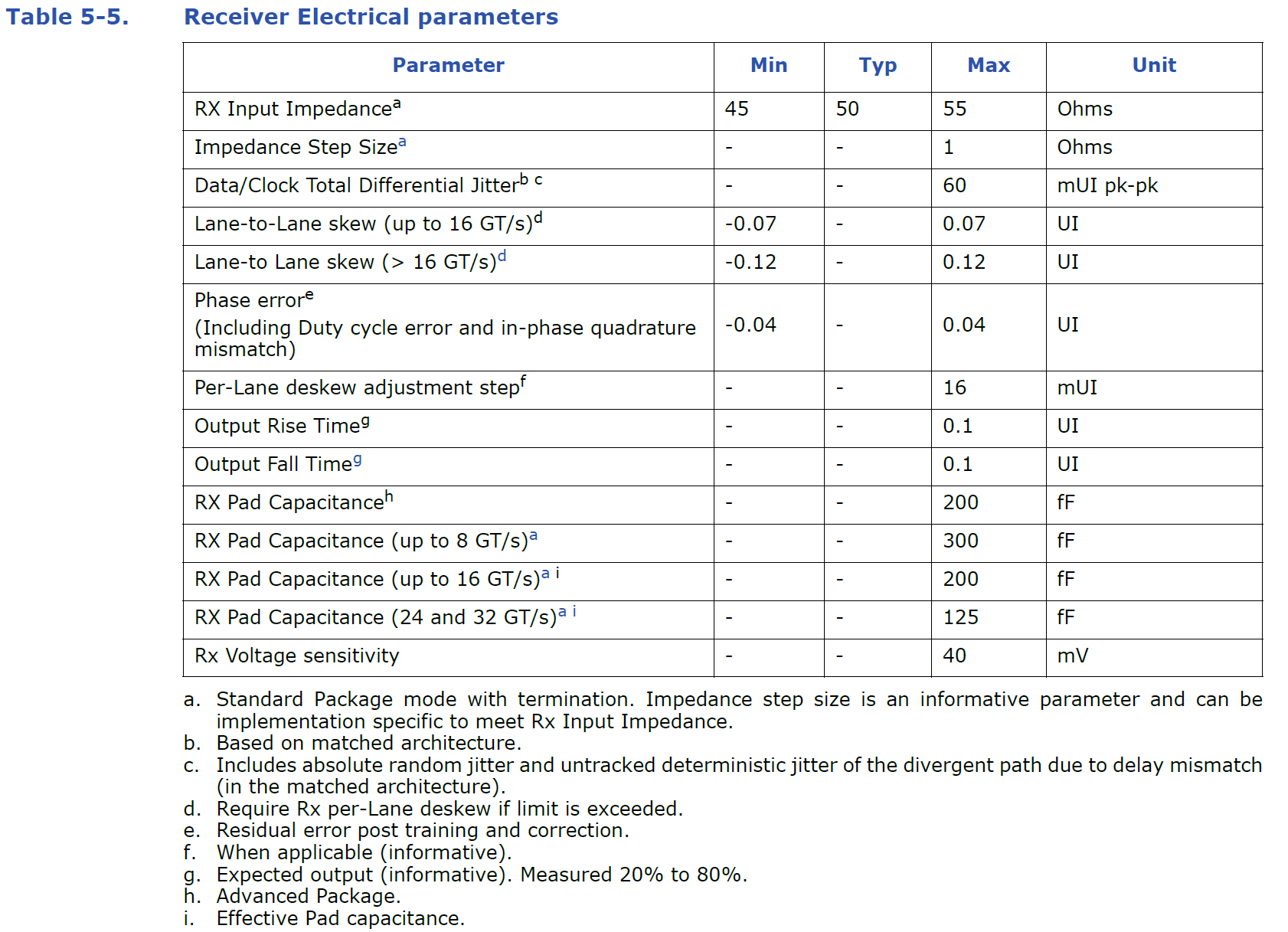

5.4.1 Receiver Electrical Parameters

指定的接收器电气参数如表5-5 所示。

a. 带端接的标准封装模式。阻抗步长是参考参数,并且可以根据具体实现来满足Rx 输入阻抗。

b. 基于匹配架构。

c. 包括由于延迟失配(在匹配架构中)导致的发散路径的绝对随机抖动和未跟踪的确定性抖动。

d. 如果超过限制,需要Rx 逐通道去偏斜。

e. 训练和校正后的残余误差。

f. 当适用时(参考)。

g. 预期输出(参考)。测量20% 至80%。

h. 先进封装。

i. 有效焊盘电容。

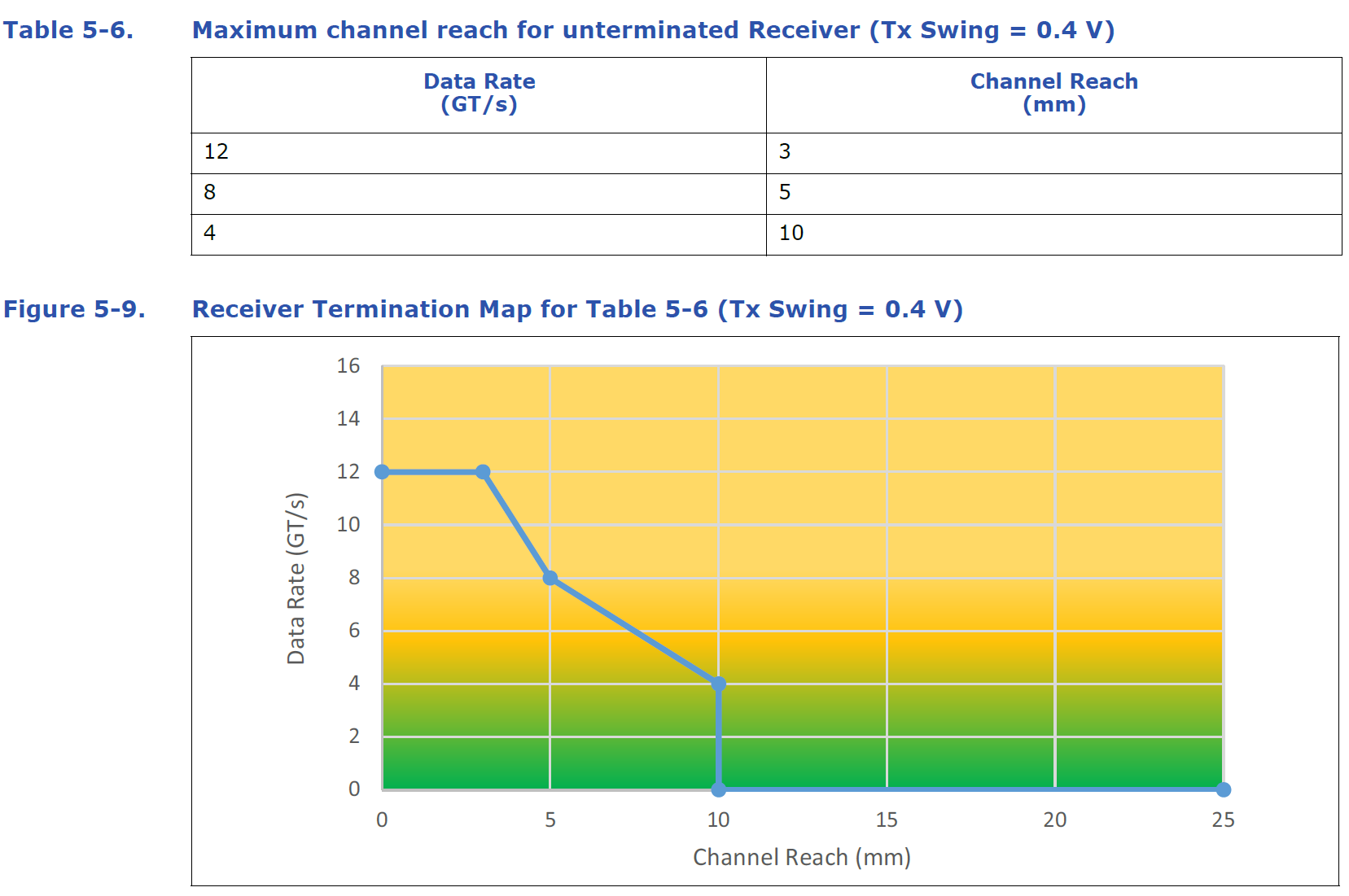

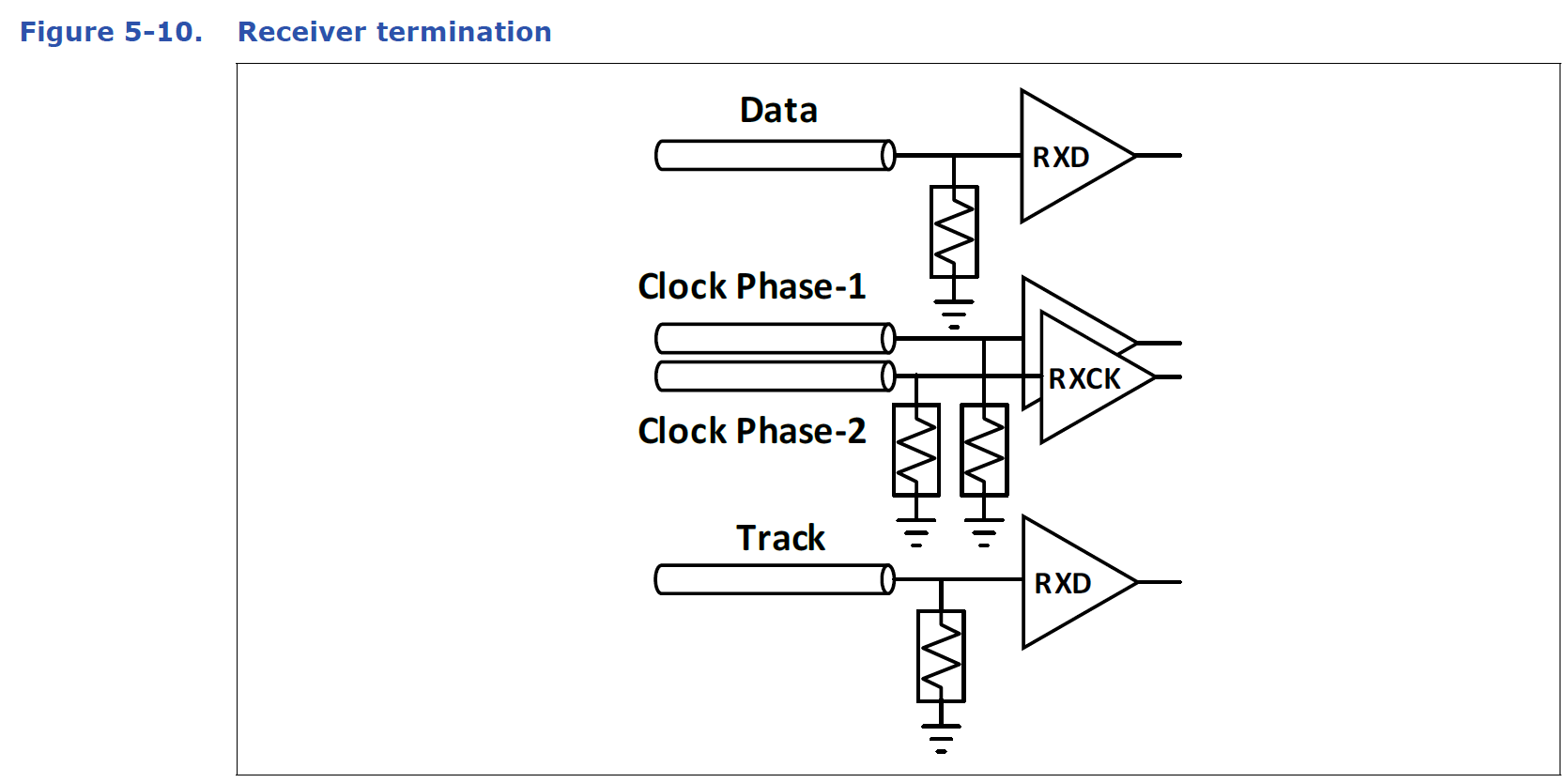

5.4.2 Rx Termination

Rx 端接仅适用于标准封装模块。先进封装模块上的所有接收器必须是未端接的。

标准封装上的接收器端接取决于数据速率和通道。表5-6 显示了最大数据速率和通道到达组合,对于这些组合,建议标准封装模块中的接收器保持未端接,以实现最低合规的发送器。

图5-9 显示了端接要求的另一种表示。图5-9 中曲线下方的区域显示了标准封装模块中的接收器建议保持未端接的速度和通道到达组合。对于所有其他组合,都需要端接。在适用时,接收器必须端接到地,如图5-10 所示。

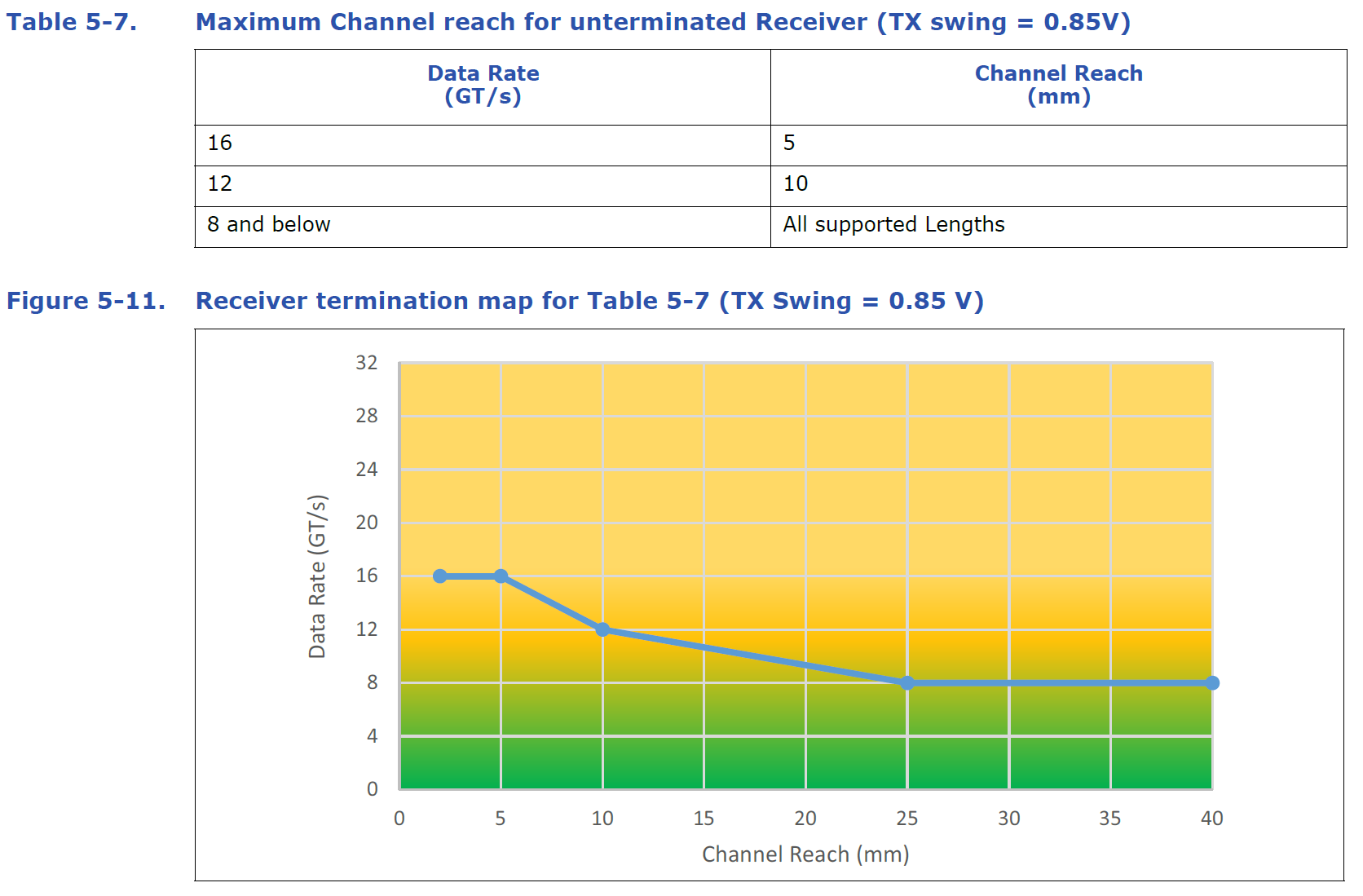

对于更高的发送器摆幅,未端接的接收器可以扩展到更长的通道和更高的数据速率。表5-7显示了发送器摆幅和0.85 V(最大推荐摆幅)的最大数据速率和通道到达组合。图5-11 显示了端接要求的另一种表示。图5-11 中曲线下方的区域显示了标准封装模块中的接收器建议保持未端接的速度和通道到达组合。

5.4.3 24 and 32 GT/s Receiver Equalization

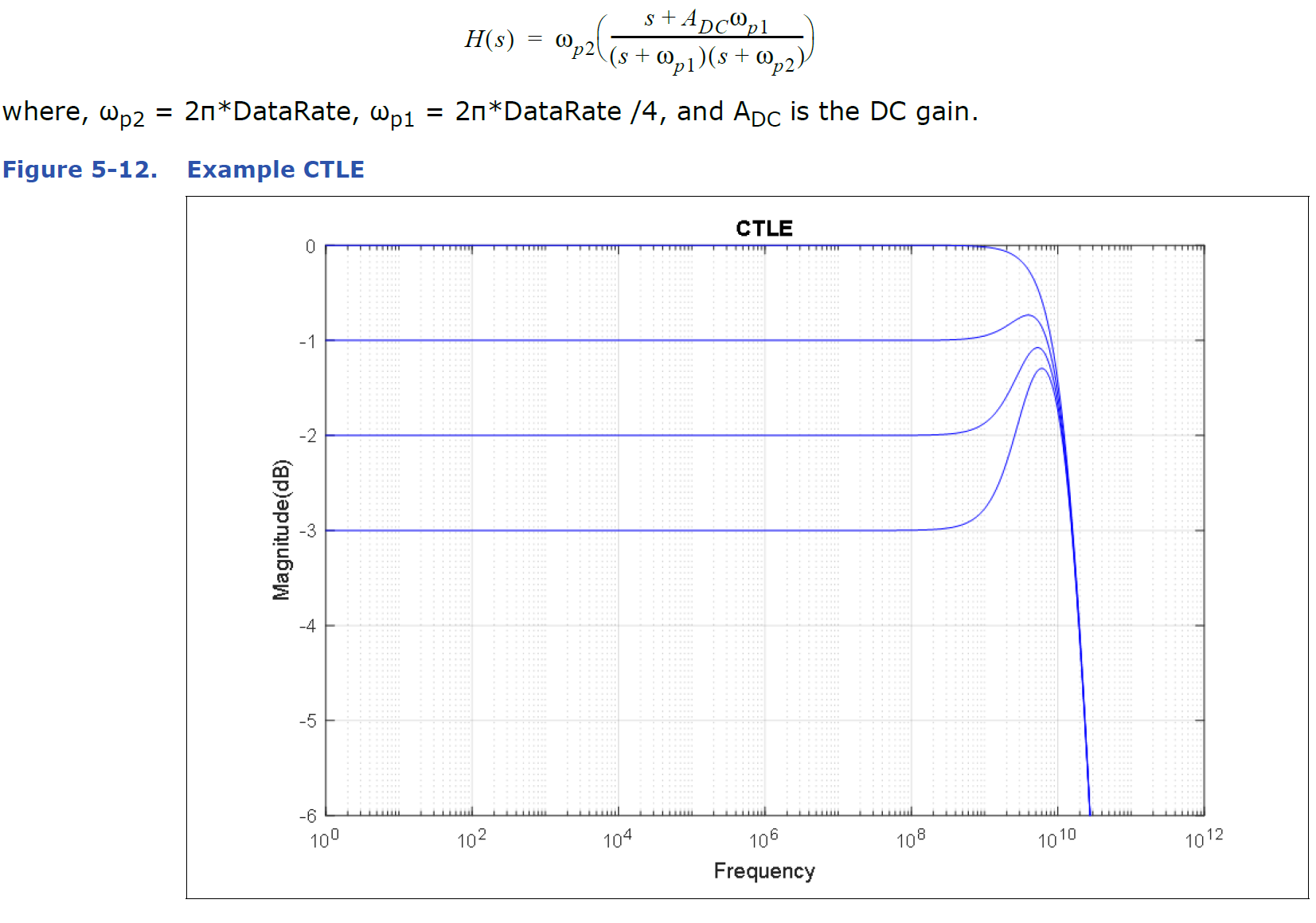

接收器均衡可以在24 GT/s 和32 GT/s 数据速率下实现。这使得即使在TX 均衡不可用的情况下也能进行链路操作。实现方式可以是CTLE、电感峰值、1 抽头DFE 或其他。预期的RX 均衡能力相当于一阶CTLE。一阶CTLE 的示例传递函数曲线如图5-12 所示,相应的方程如下所示:

5.5 Clocking

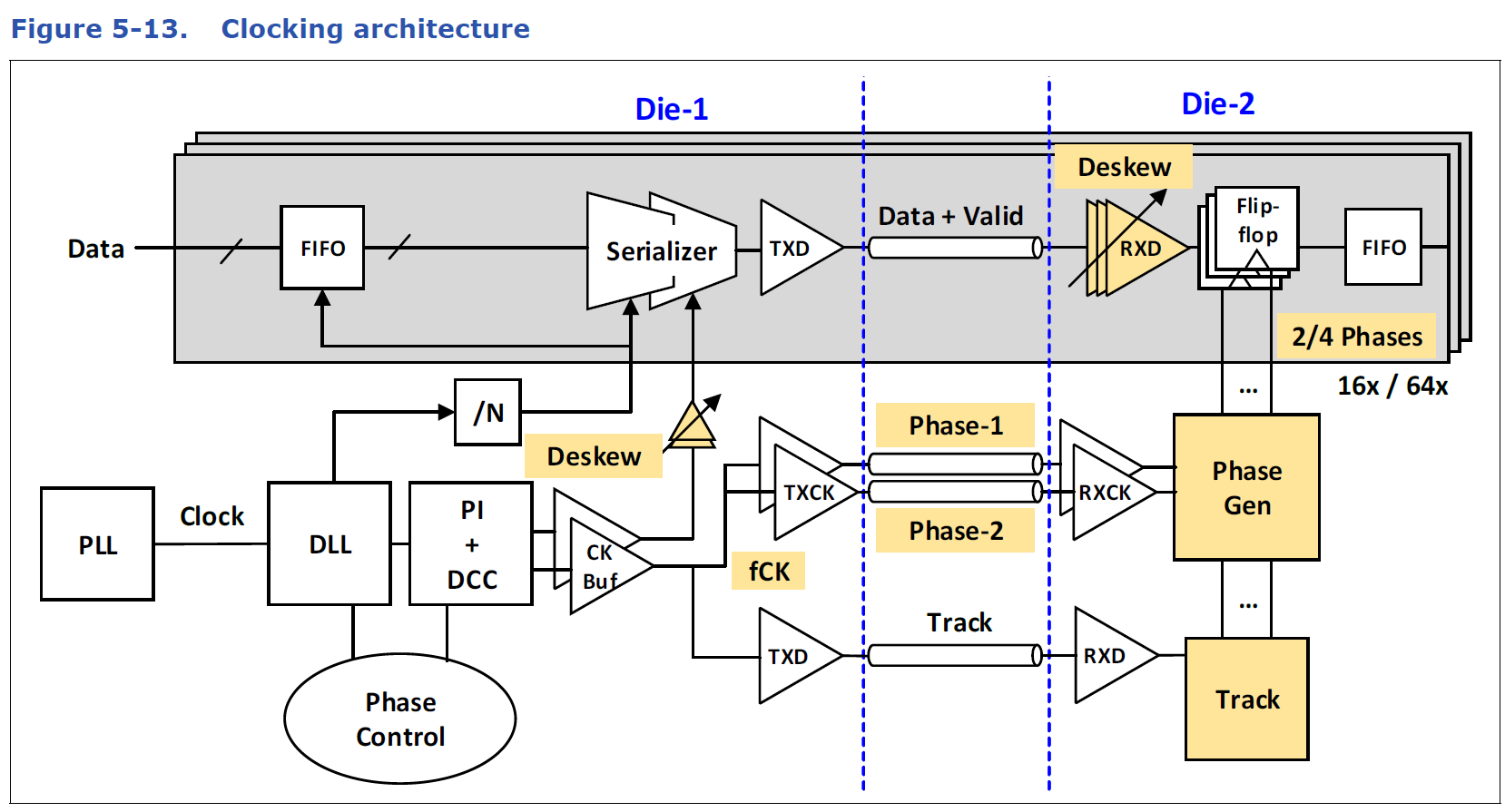

图5-13 展示了转发时钟架构。每个模块支持双相转发时钟。保持模块内所有数据通道和有效信号之间的匹配至关重要。接收器必须在接收器时钟分配和Data/Valid 接收器路径之间提供匹配的延迟。这是为了将电源噪声引起的抖动对链路性能的影响降至最低。如图5-13 所示,在发送器上进行相位调整。需要进行链路训练以设置相位调整的位置,以最大化链路余量。

在较高的数据速率下,接收器眼图余量可能较小,数据通道(包括有效通道)之间的任何偏斜可能会进一步降低链路性能。在高数据速率下,发送器必须支持逐通道的去偏斜。

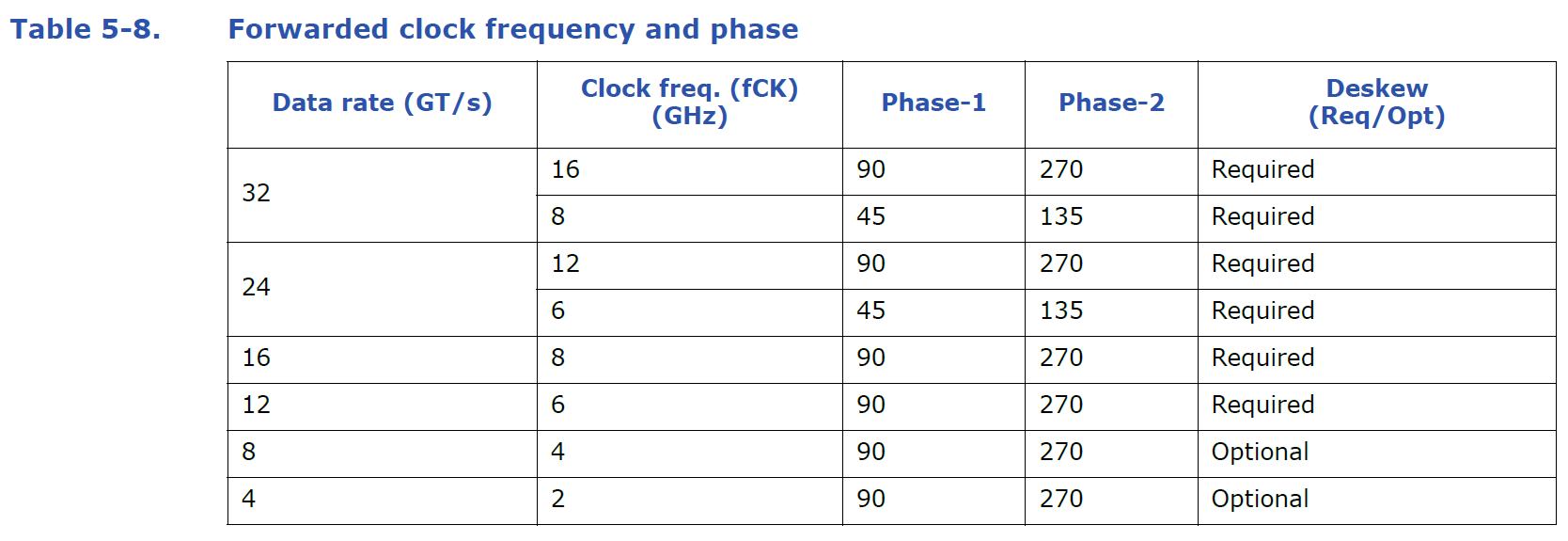

本规范在数据速率(24 GT/s 和32 GT/s)下支持四分之一速率的时钟频率。在这些数据速率下,转发Clock 发送器除了差分时钟外,还必须支持正交相位(以实现四分之一速率或二分之一速率的接收器实现)。表5-8 显示了在不同数据速率下必须支持的时钟频率和相位。转发时钟相位在链路初始化和训练期间协商(见第4.5.3.3.1 节)。在24 GT/s 和32 GT/s 时,接收器可以选择支持差分时钟或正交时钟。功能寄存器在表9-47 中定义,并在链路协商开始时通告。请注意,为了与最大数据速率较低的设计实现互操作性,在16 GT/s 及以下,无论在24 GT/s 和32 GT/s 时的选择如何,都必须始终使用差分时钟。

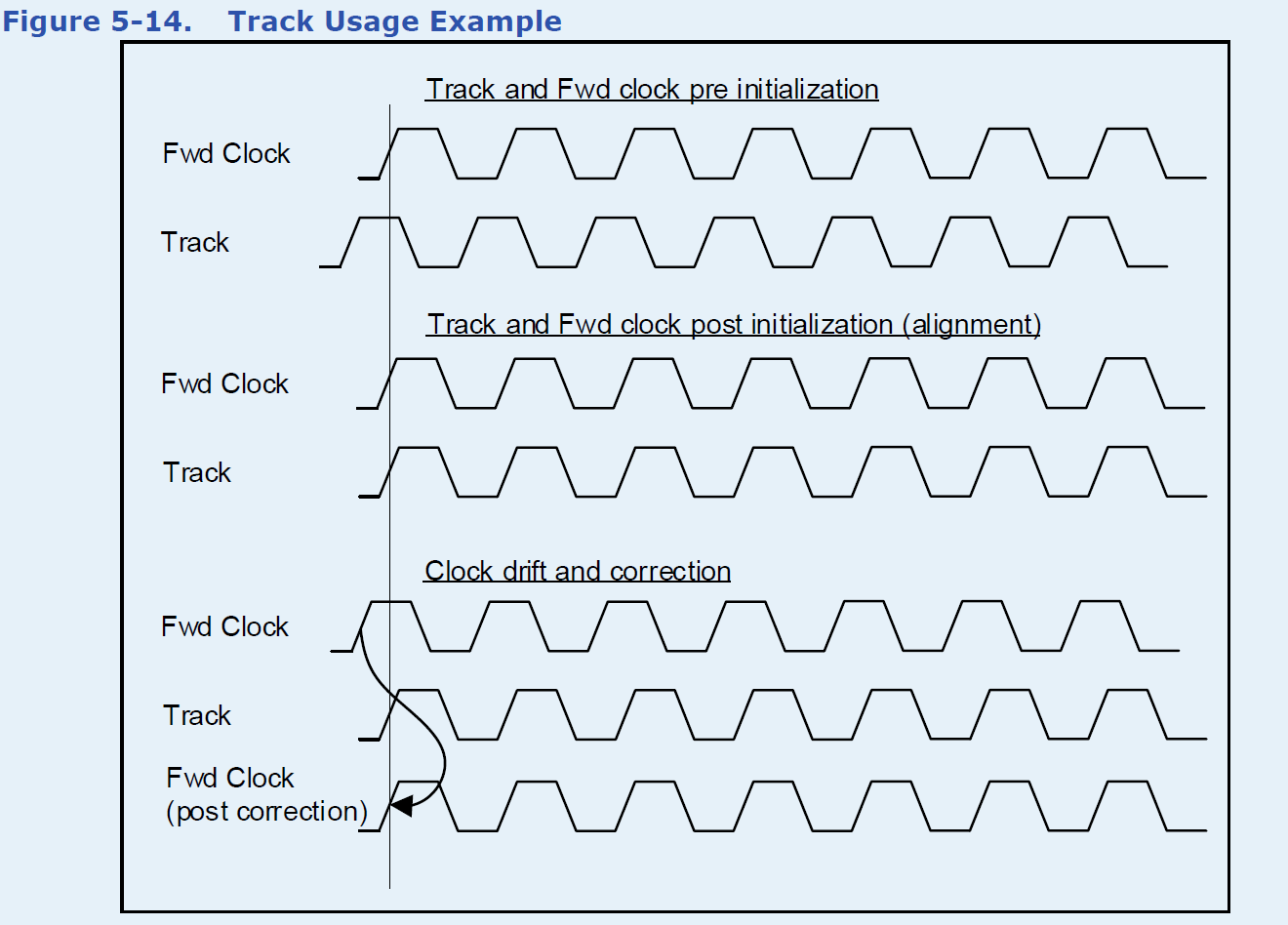

5.5.1 Track

Track 信号可用于执行运行时重新校准,以针对缓慢变化的电压、温度和晶体管老化状况调整接收器时钟路径。

当UCIe 模块请求时,UCIe 模块伙伴在其Track 发送器上发送与转发时钟的相位1 对齐的时钟模式(1010…),如图5-13 所示。

实现说明

本实现说明提供了Track 信号的示例用法,以校准接收器上Data 和Clock 之间与温度和电压相关的缓慢变化的延迟漂移。

Track 使用与Data 相同类型的Tx 驱动器和Rx 接收器(见图5-13)。与转发时钟的相位1对齐的时钟模式从Track 发送器发送,并在Track 接收器上接收。任何初始偏斜都可以在接收器侧的初始化和训练(MBTRAIN.RXCLKCAL)期间校准。在运行时,可以检测到Data和转发时钟之间的任何漂移。检测漂移的一种方法是用转发时钟对Track 进行采样。可以收集特定于实现的样本数量,如果需要,可以取平均值,并用于漂移检测。然后可以在转发时钟上校正此漂移(如果需要)。

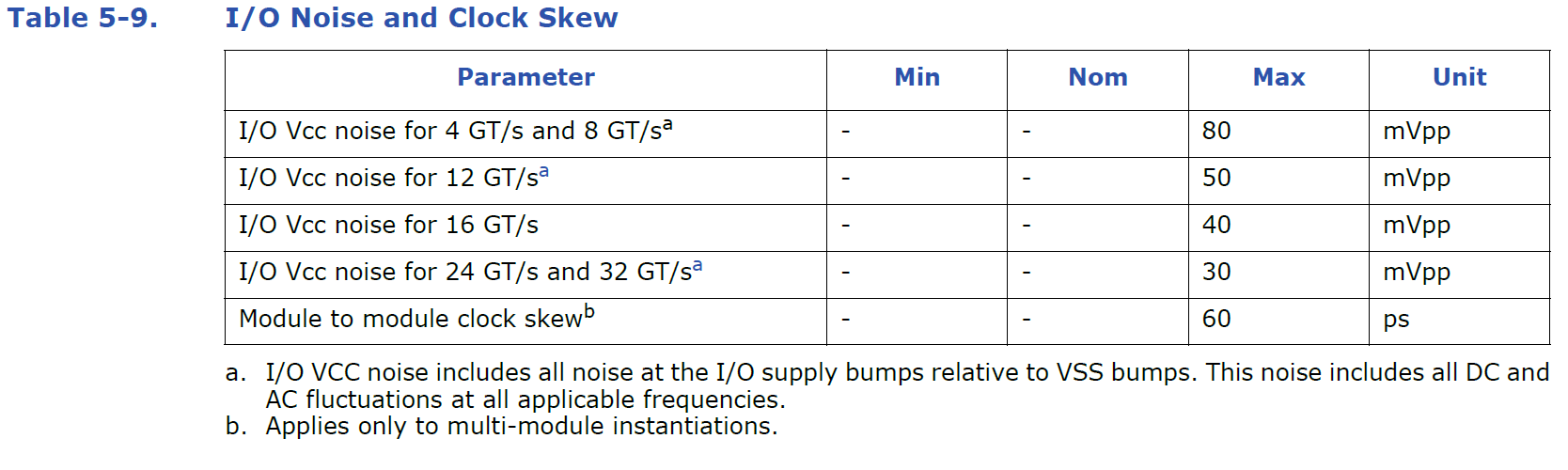

5.6 Supply noise and clock skew

(电源噪声和时钟偏斜)I/O Vcc 噪声和数据模块之间的时钟偏斜应在表5-9 规定的范围内。

a. I/O VCC 噪声包括相对于VSS 凸点在I/O 电源凸点处的所有噪声。此噪声包括在所有适用频率下的所有直流和交流波动。

b. 仅适用于多模块实例化。

实现说明

由于不同的微凸块最大电流容量和供电要求,先进封装中的PHY 可能具有由TX 为RX 电路提供I/O 电源的情况。

由于电流消耗低,强烈建议边带电源电压处于始终开启的电源域。

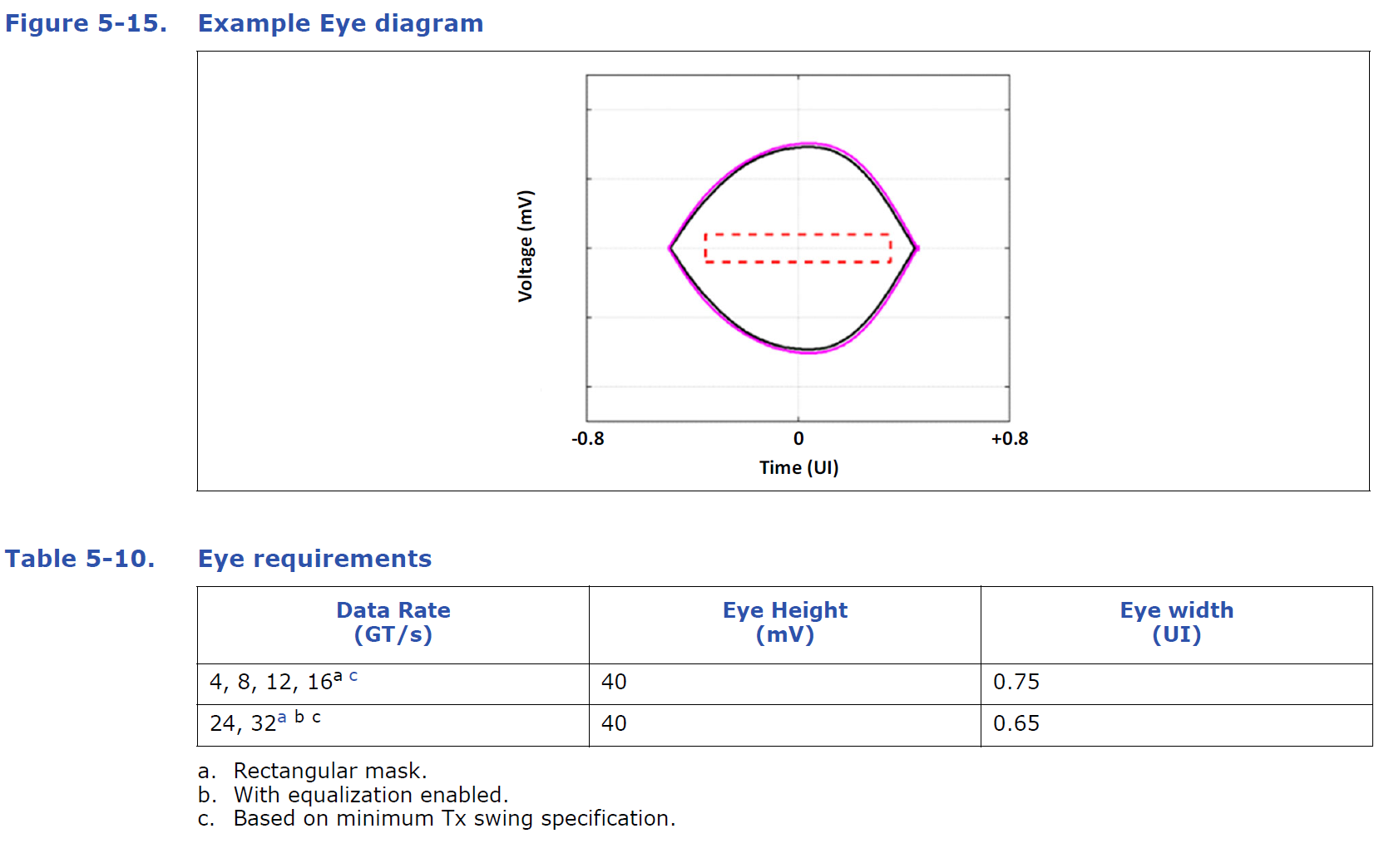

5.7 Ball-out and Channel Specification

UCIe 互连通道需要满足表5-10 中规定的最小矩形眼图张开要求,在无噪声和无抖动行为的

TX 和RX 模型的通道合规性模拟条件下。

a. 矩形掩码。

b. 启用均衡。

c. 基于最小Tx 摆幅规范。

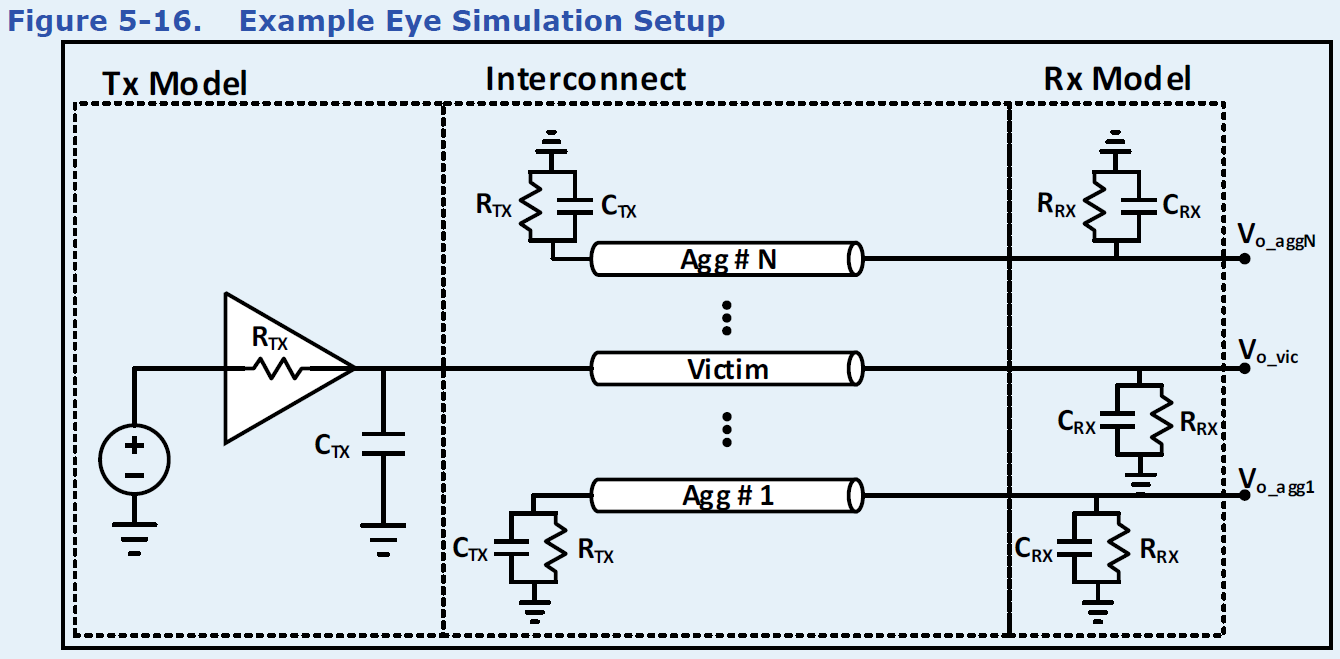

实现说明

图5-16 展示了一个可用于生成图5-15 所示统计眼图的示例电路设置。RTX 是发送器阻抗,RRX 表示接收器端接。CTX、CRX 分别代表有效的发送器和接收器电容。对于串扰,需要包括19 个最大的干扰源。在24 GT/s 和32 GT/s 时启用发送器均衡(TXEQ)。

眼图是通过两步过程生成的。

1. 使用图5-16 所示的电路设置生成ISI 和XTALK 通道阶跃响应。

2. 在信号完整性或通道仿真工具中使用生成的通道响应来生成统计眼图(见图5-15)

其他等效方法也可以使用,具体取决于信号完整性或通道仿真工具。

5.7.1 Voltage Transfer Function(电压传输函数)

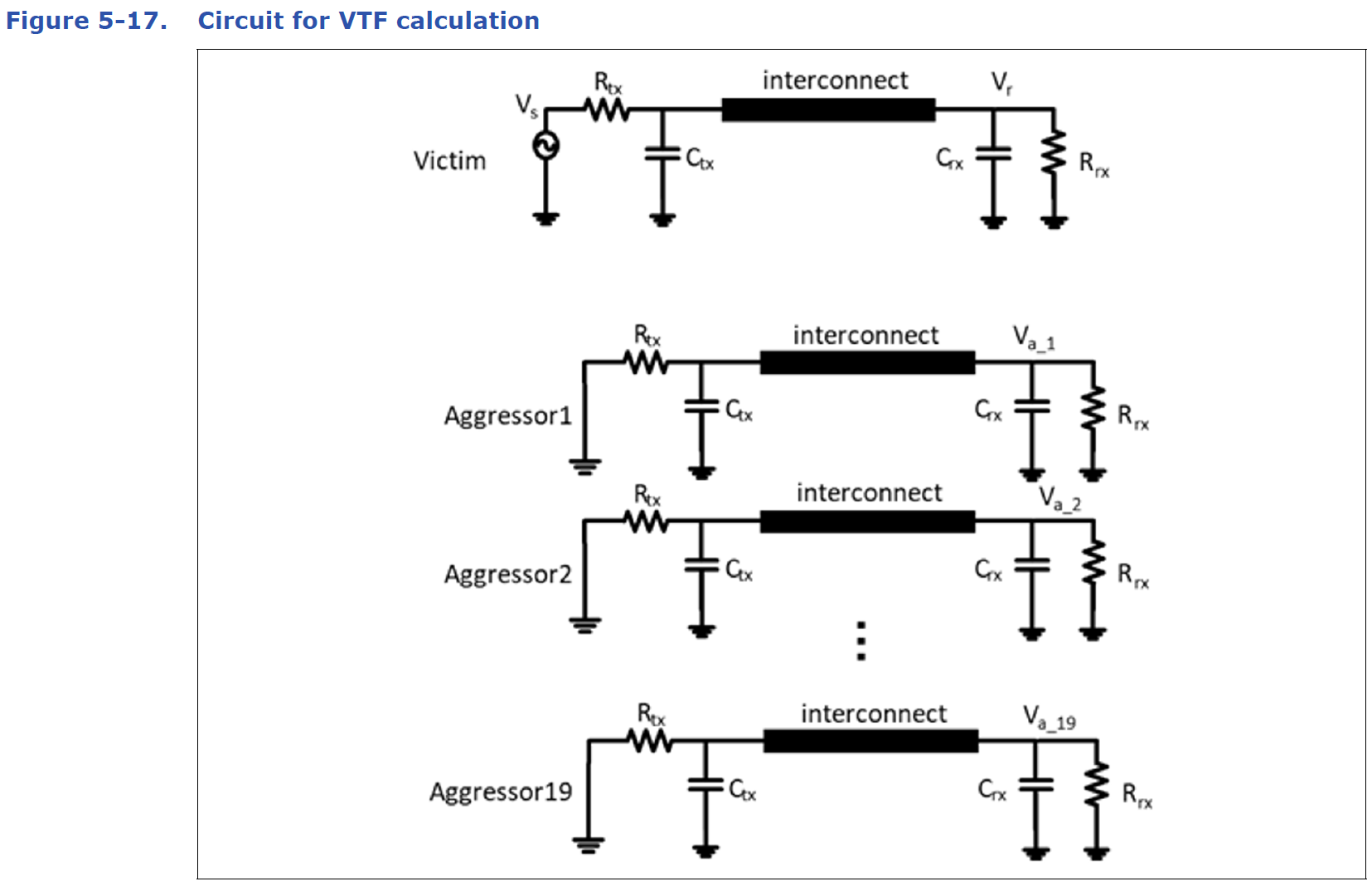

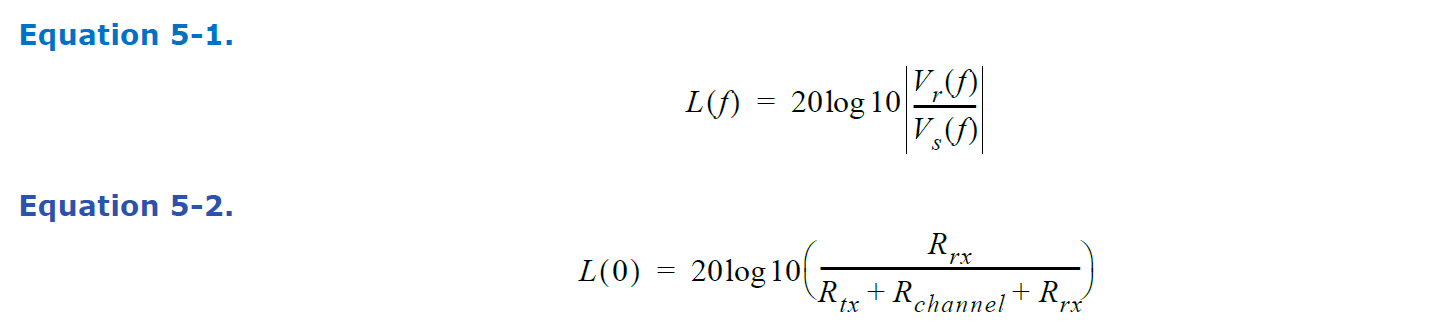

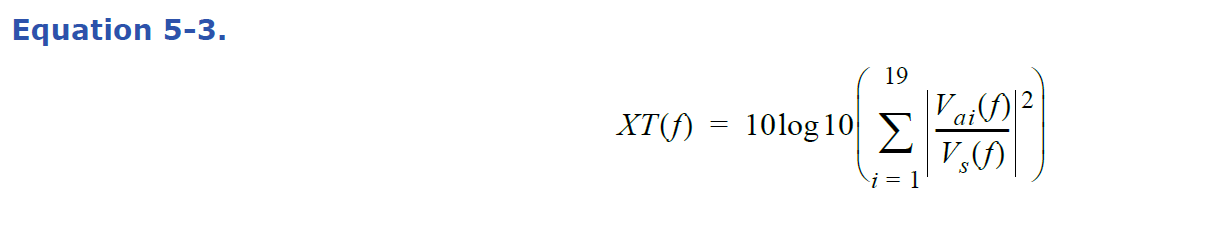

基于电压传输函数(VTF)的指标用于定义插入损耗和串扰。VTF 指标包含了TX 和RX 端接的电阻和电容组件。图5-17 显示了VTF 计算的电路图。

VTF 损耗定义为接收器电压与源电压的比值,如公式5-1 和公式5-2 所示。公式5-1。

L(f) 是与频率相关的损耗,L(0) 是直流损耗。对于未端接的通道,L(0) 实际上为0。VTF 串扰定义为攻击者接收器电压与源电压比值的功率总和。计算中包含19 个攻击者。基于串扰互易性,VTF 串扰可以如公式5-3 所示表达。

5.7.2 Advanced Package

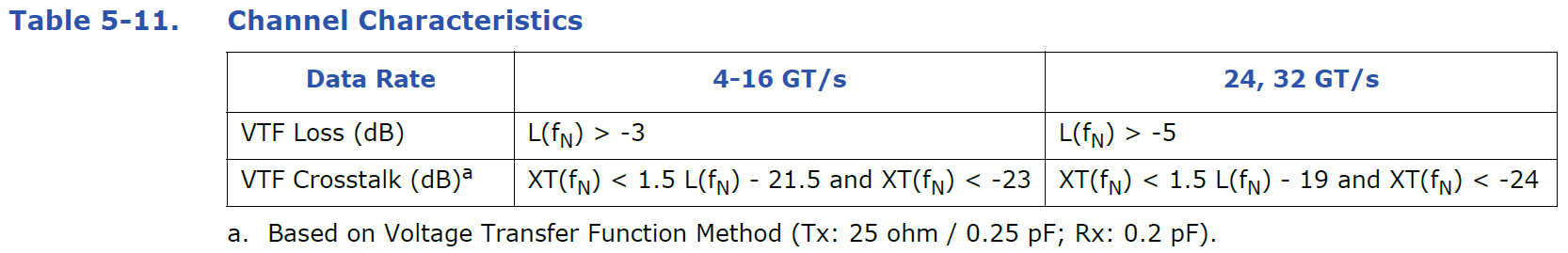

fN 是奈奎斯特频率。表格中的方程在损耗-串扰坐标平面中形成一条分段线,定义了通过/不通过区域。

5.7.2.1 Loss and Crosstalk Mask

损耗和串扰由奈奎斯特频率下的L(fN) 和XT(fN) 定义的掩模指定。对于损耗,它是从直流到fN 的线性掩模,对于串扰,它是平坦掩模,如图5-18 所示。从直流到fN 的损耗需要高于规格线。从直流到fN 的串扰需要低于规格线。图5-18 中的绿线是一个代表性的通过信号。

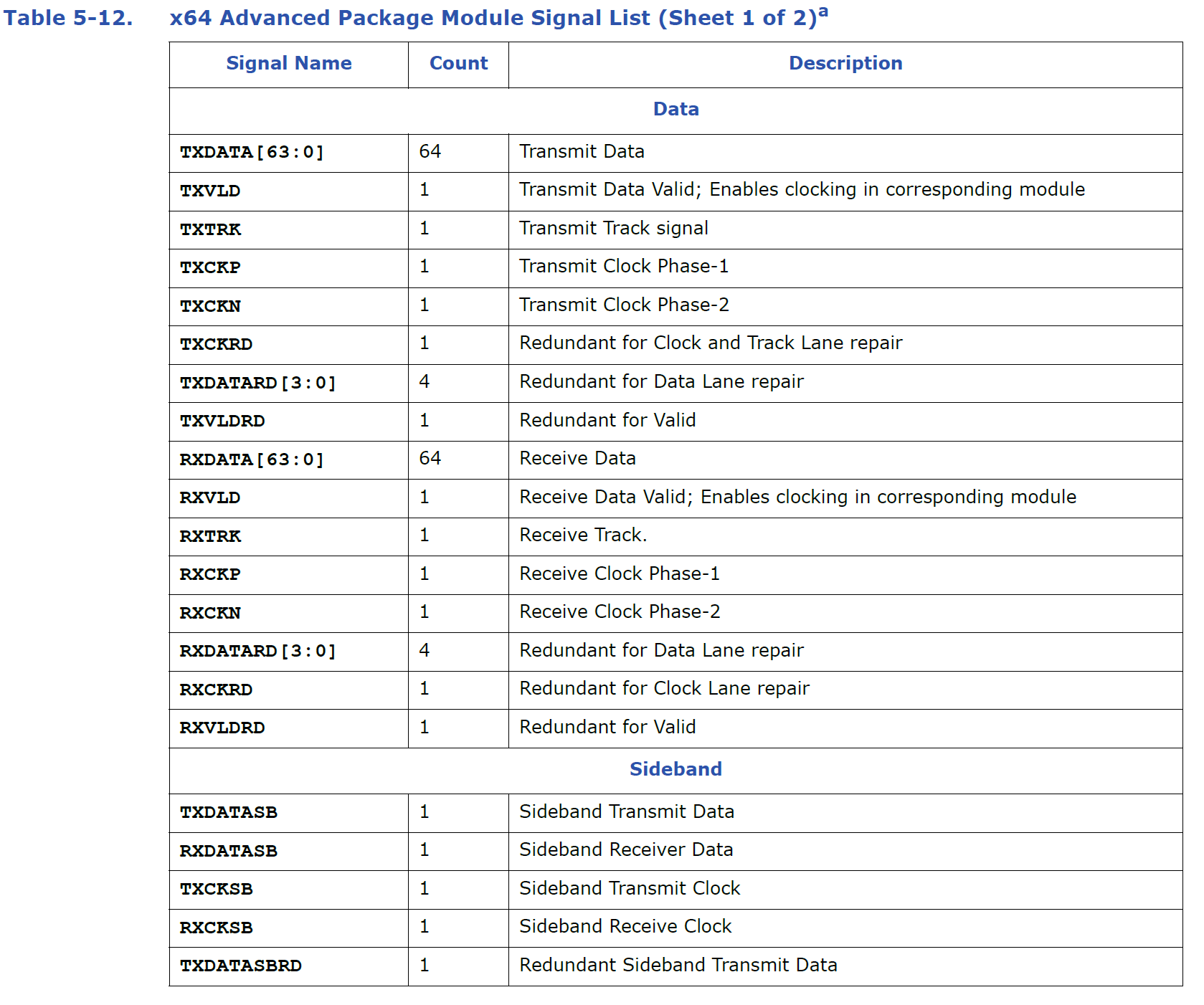

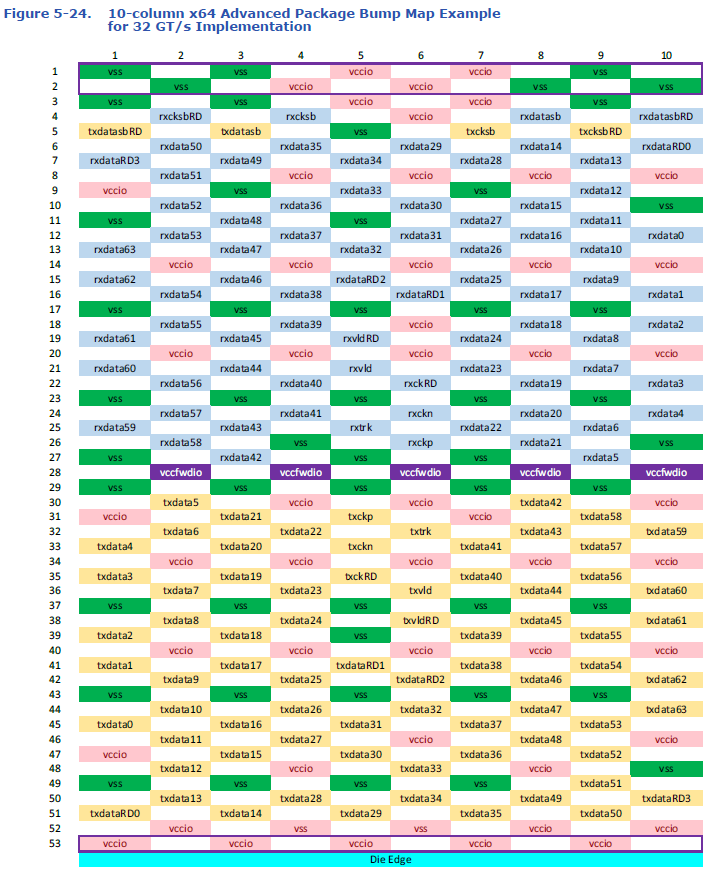

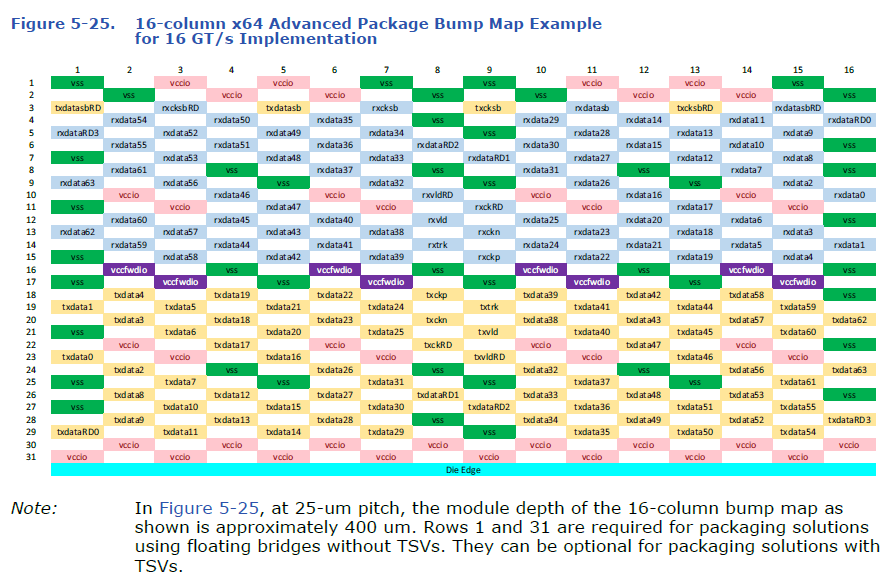

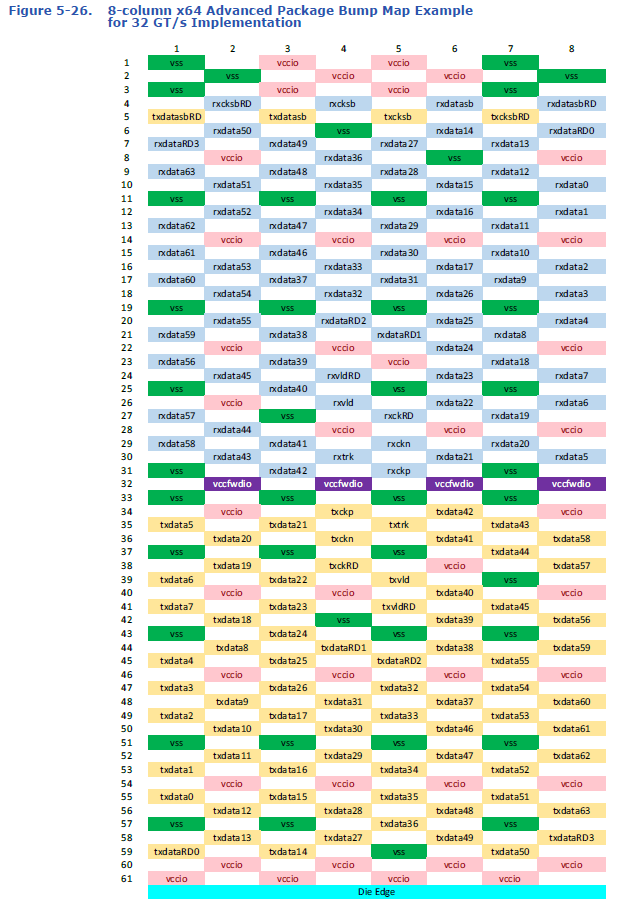

5.7.2.2 x64 Advanced Package Module Bump Map

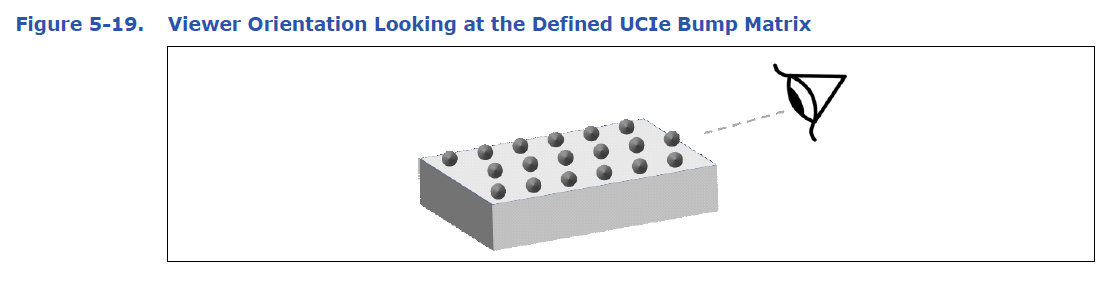

(x64 先进封装模块凸点图)本节及以下所有的凸点矩阵都以“(dead bug)视图定义,这意味着观察者直接看向朝上的UCIe 微凸点,Die 像一样翻转,如图5-19 所示。

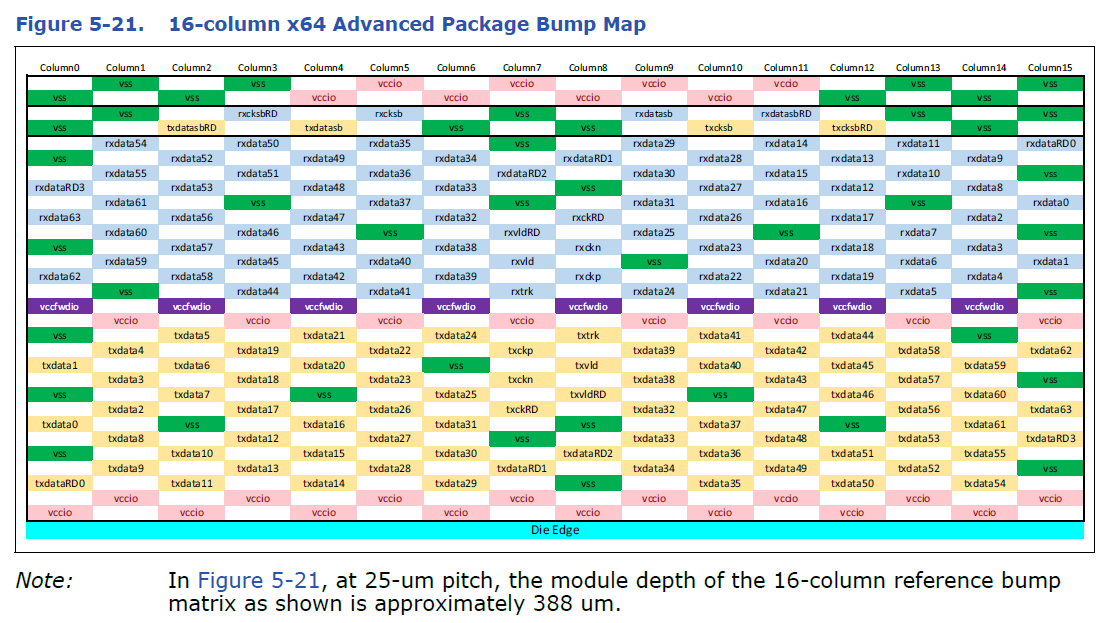

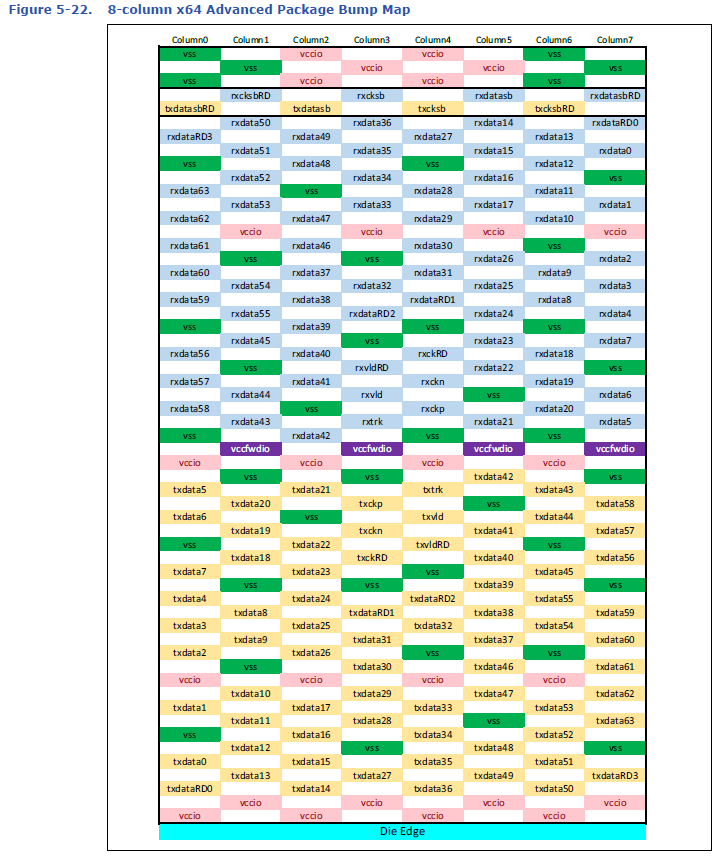

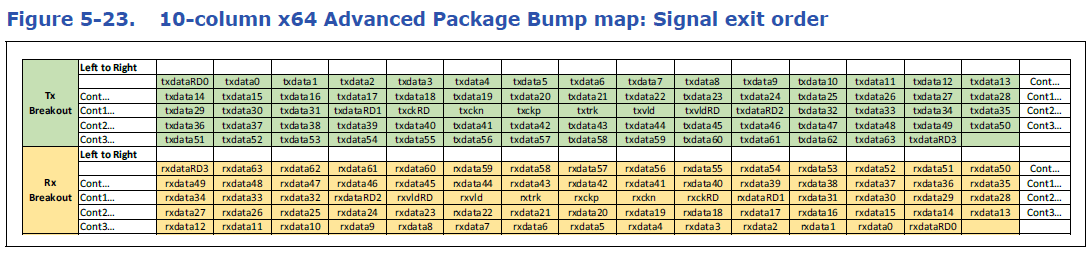

图5-20、图5-21 和图5-22 分别展示了10 列、16 列和8 列x64 先进封装模块的参考凸点矩阵。凸点图的左下角将被视为凸点矩阵的“原点”,最左边的列是第0 列。

强烈建议在x64 先进封装接口中遵循图5-20、图5-21 和图5-22 中提供的凸点矩阵。10 列凸点矩阵对于38 至50 um 的凸点间距范围是最优的。为了在不同的凸点间距下实现最佳的面积缩放,分别为25 至37 um 和51 至55 um 的凸点范围定义了可选的16 列和8 列凸点矩阵,这将在保持388.8 um 的模块宽度的同时实现最佳的模块深度,分别如图5-21 和图5-22 所示。

对于10 列x64 先进封装凸点矩阵,必须遵循以下规则:

列内的信号顺序必须保持。例如,第0 列必须包含以下信号:txdataRD0、txdata0、txdata1、

txdata2、txdata3、txdata4、…、rxdata59、rxdata60、rxdata61、rxdata62、rxdata63、rxdataRD3和txdatasbRD。同样,16 列和8 列的x64 先进封装必须在各自凸点矩阵的列内保持信号顺序。

强烈建议遵循凸点矩阵中所示的电源和接地模式。必须确保提供足够的电源和接地凸点,以满足通道特性(FEXT 和NEXT)和供电要求。

实例化多个先进封装凸点矩阵模块时必须遵循以下规则: 模块必须以相同的方向逐步放置并邻接。

不允许水平或垂直镜像。

不允许模块堆叠。

此外,在多模块实例化中,强烈建议在多模块实例化的每个外边缘添加一列VSS 凸点。镜像Die 实现可能需要一个折弯或额外的金属层以实现适当的连接。

注意:在图5-22 中,在55 um 间距下,如图所示的8 列参考凸块矩阵的模块深度约为1585 um。

图5-23 展示了10 列x64 先进封装凸点图的信号退出顺序。

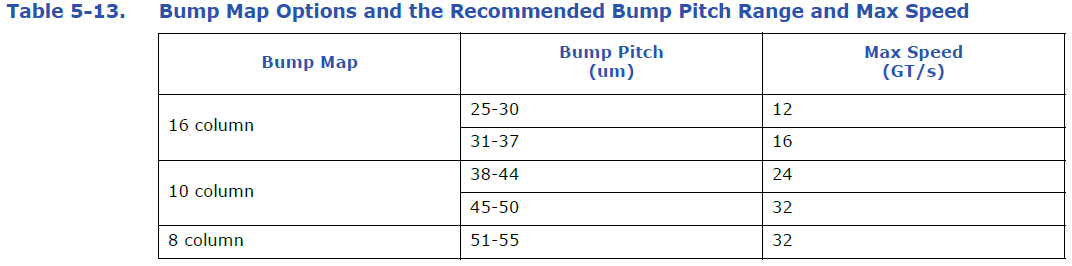

实现说明 —— 最大速度的X64 凸点图

图5-20、图5-21 和图5-22 中的三个参考凸点图针对不同的凸点间距范围进行推荐,而PHY实现具有调整电源和接地凸点的灵活性,以满足通道特性和供电要求,这在很大程度上取决于目标速度和先进封装技术能力。

在更高的速度下,PHY 电路通过凸点汲取更大的电流,并要求封装解决方案具有更好的信号和电源完整性。这通常需要添加电源和接地凸点并优化它们的分布,但该实现还需要最小化通道间的长度偏斜,并保留每列中信号的分配和相对顺序,以符合5.7.2.2 节中的凸点矩阵规则。

制定本实现说明是为了向PHY 实现提供一组参考x64 凸点图,以涵盖指定的最大速度。表5-13 总结了这些凸点图选项的相应最大速度及其推荐的凸点间距范围。

图5-24、图5-25 和图5-26 中的凸点图是对应最大速度的x64 实现参考,增强了电源和接地凸点。它们都符合5.7.2.2 节中的凸点矩阵规则,并在信号退出顺序方面保持向后兼容性。这些参考示例已针对信号完整性、电源完整性、通道间偏斜、电迁移应力和凸点面积基于行业中的大多数先进封装技术进行了优化。请注意,技术要求各不相同,实际实现要求和性能目标仍需与技术提供商核实凸点图。

注意:在图5-24 中,在45 um 间距时,所示的10 列凸点图的模块深度约为1225 um。对于使用无硅通孔(through-silicon vias,TSV)的浮桥的封装解决方案,需要第1、2 和53 行。对于具有TSV 的封装解决方案,它们可以是可选的。

注意:在图5-25 中,在25 um 间距时,所示的16 列凸点图的模块深度约为400 um。对于使用无TSV 的浮桥的封装解决方案,需要第1 行和第31 行。对于具有TSV 的封装解决方案,它们可以是可选的。

注意:在图5-26 中,在55 um 间距时,所示的8 列凸点图的模块深度约为1705 um。对于使用无TSV 的浮桥的封装解决方案,需要第1 行、第2 行和第61 行。对于具有TSV 的封装解决方案,它们可以是可选的。

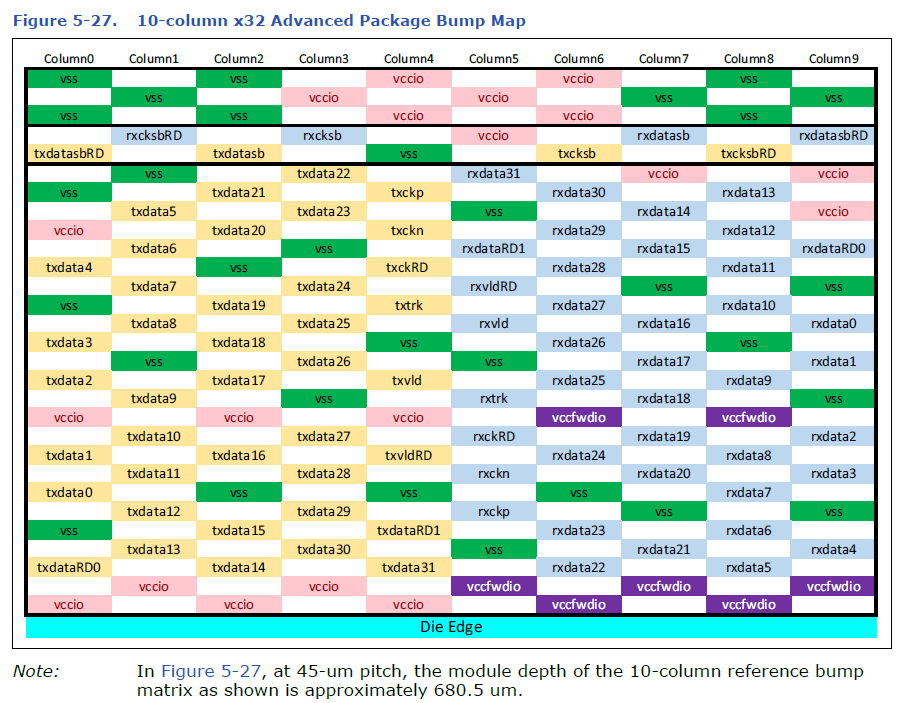

5.7.2.3 x32 Advanced Package Module Bump Map

UCIe 还定义了一个x32 先进封装模块,支持32 个Tx 和32 个Rx 数据信号,以及每个Tx两个和每个Rx 两个(总共四个)冗余凸点用于通道修复功能。所有其他信号,包括边带,与x64 先进封装的相同。

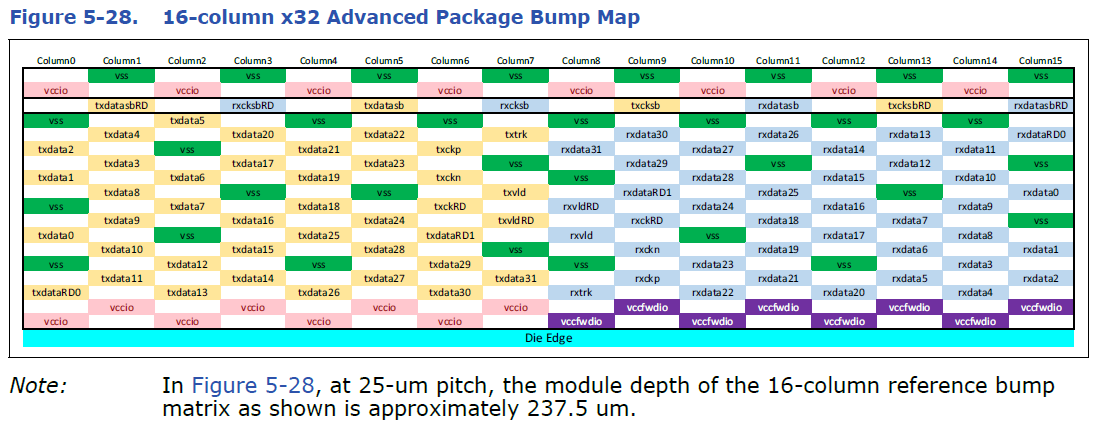

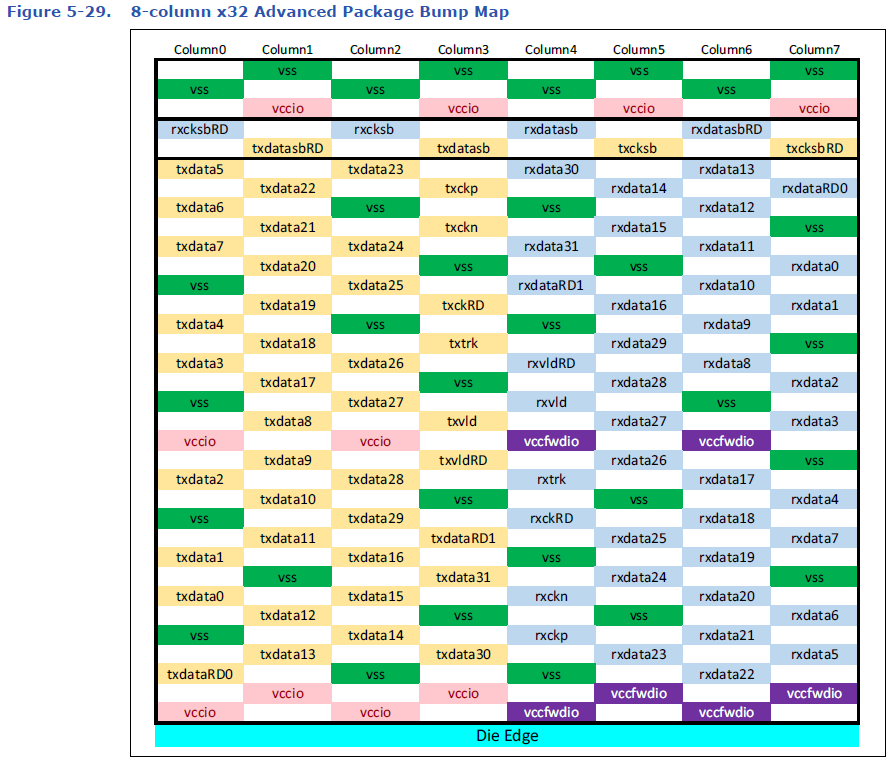

图5-27、图5-28 和图5-29 分别展示了10 列、16 列和8 列x32 先进封装模块的参考凸点矩阵。凸点图的左下角将被视为凸点矩阵的“原点”,最左边的列是第0 列。

强烈建议x32 先进封装模块遵循图5-27、图5-28 和图5-29 中提供的凸点矩阵。

对于10 列x32 先进封装凸点矩阵,必须遵循以下规则:

一列内的信号顺序必须保留。例如,第0 列必须包含信号:txdataRD0、txdata0、txdata1、 txdata2、txdata3、txdata4 和txdatasbRD。同样,16 列和8 列x32 先进封装必须在各自凸点矩阵的一列内保留信号顺序。

强烈建议遵循凸点矩阵中所示的电源和接地模式。必须确保提供足够的电源和接地凸点,以满足通道特性(FEXT 和NEXT)和供电要求。

实例化多个x32 先进封装模块时,必须遵循5.7.2.2 节中定义的相同规则。

注意:在图5-27 中,在45 um 间距时,所示的10 列参考凸点矩阵的模块深度约为680.5 um。

注意:在图5-28 中,在25 um 间距时,所示的16 列参考凸点矩阵的模块深度约为237.5 um。

注意:在图5-29 中,在55 um 间距时,所示的8 列参考凸点矩阵的模块深度约为962.5 um。

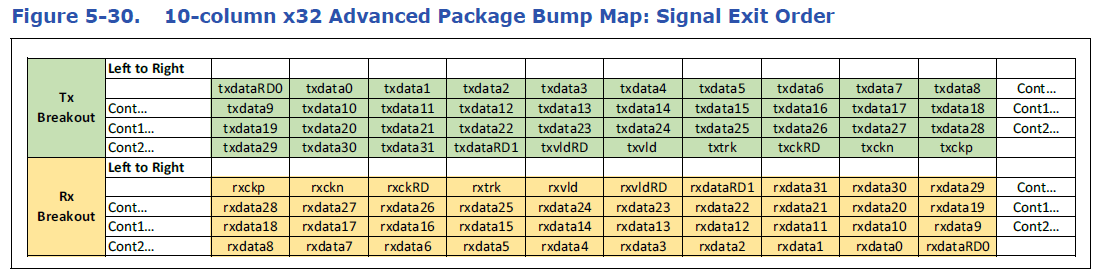

图5-30 展示了10 列x32 先进封装凸点图的信号退出顺序。

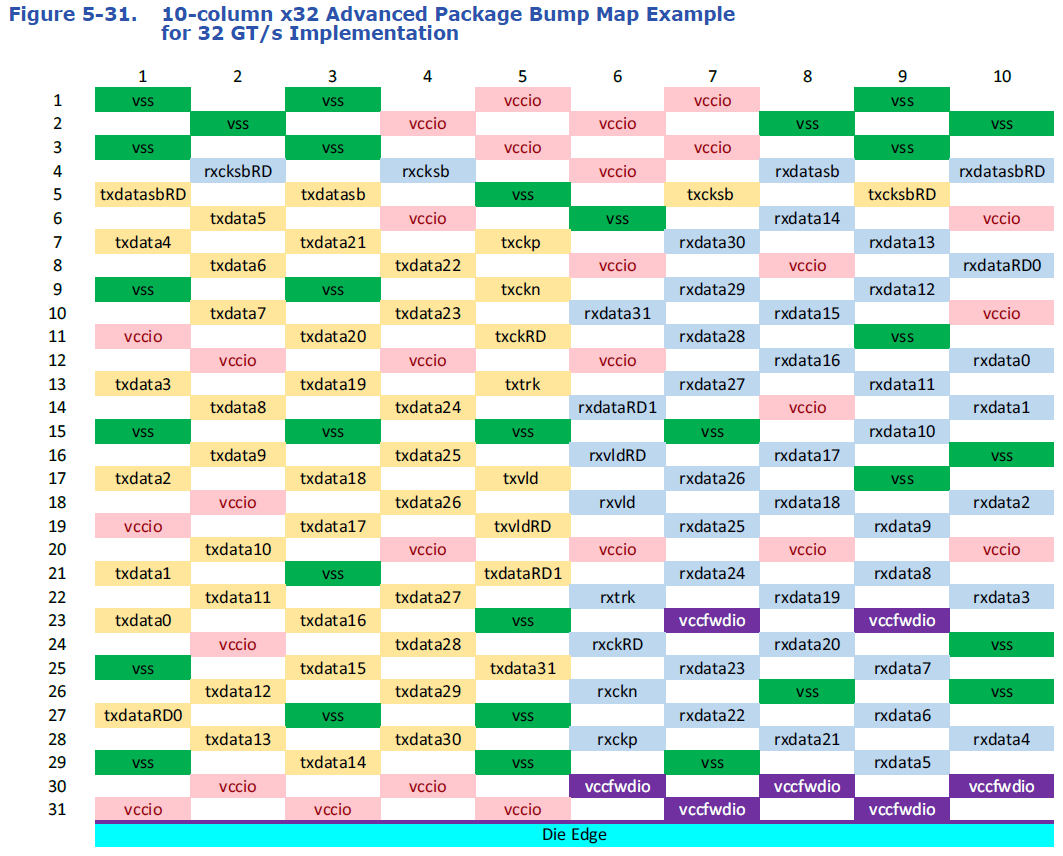

实现说明——最大速度的X32 凸点图

本实现说明旨在为PHY 实现提供一组参考x32 凸点图,以涵盖指定的最大速度。

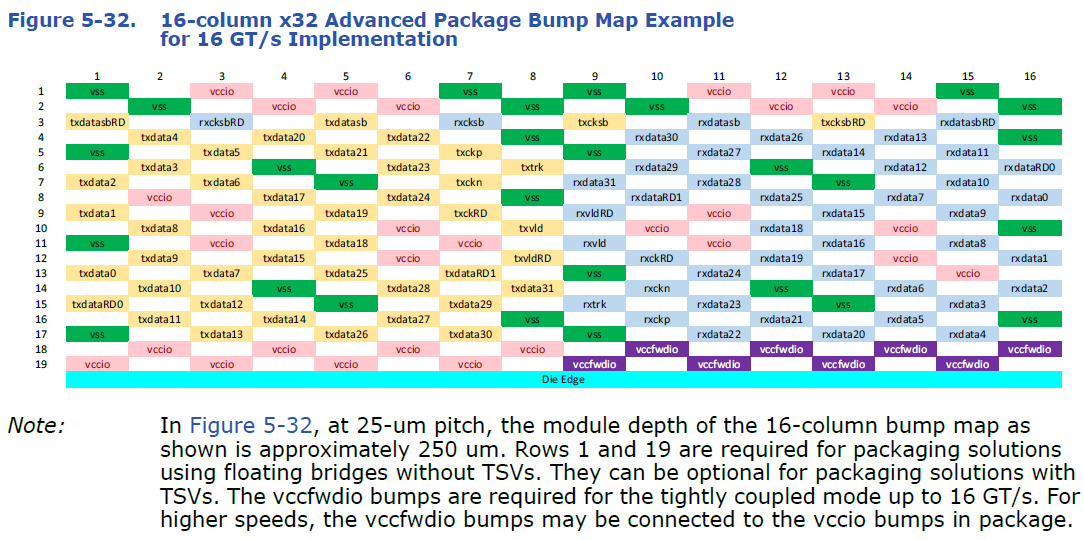

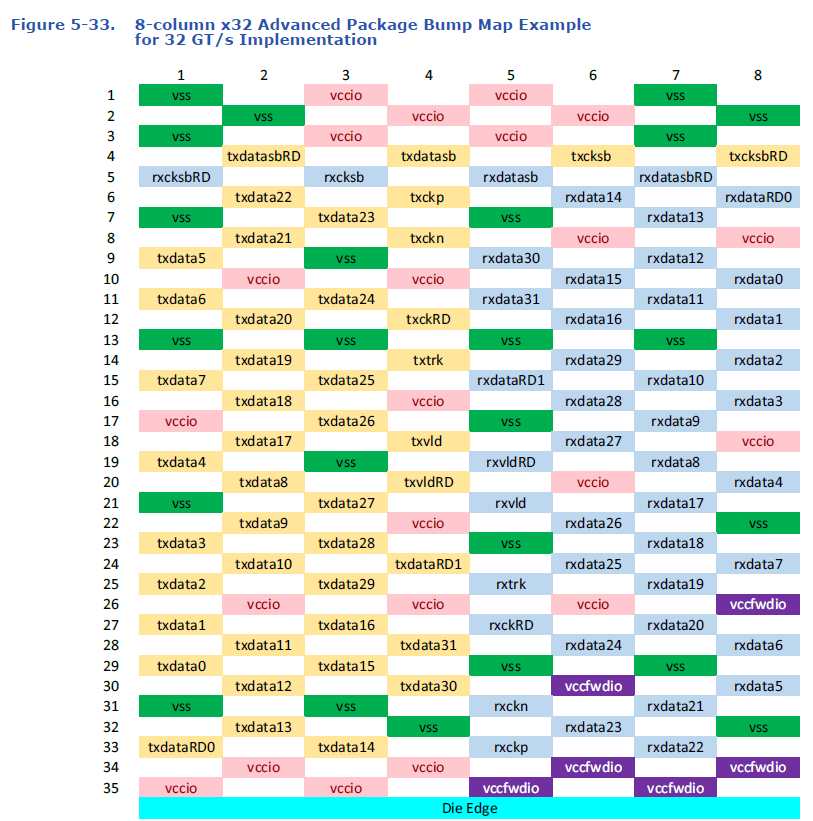

图5-31、图5-32 和图5-33 中的凸点图是对应最大速度的x32 实现参考,增强了电源和接地凸点。它们都符合5.7.2.3 节中的凸点矩阵规则,并在信号退出顺序方面保持向后兼容性。

这些参考示例已针对信号完整性、电源完整性、通道间偏斜、电迁移应力和凸点面积基于行

业中的大多数先进封装技术进行了优化。请注意,技术要求各不相同,实际实现要求和性能

目标仍需与技术提供商核实凸点图。

注意:在图5-31 中,在45 um 间距时,所示的10 列凸点图的模块深度约为725 um。对于使用无硅通孔(through-silicon vias,TSV)的浮桥的封装解决方案,需要第1 行、第2 行和第31 行。对于具有TSV 的封装解决方案,它们可以是可选的。在高达16 GT/s 的紧耦合模式下,需要vccfwdio 凸点。对于更高的速度,vccfwdio 凸点可以在封装中连接到vccio 凸点。

Implementation

注意:在图5-32 中,在25 um 间距时,所示的16 列凸点图的模块深度约为250 um。对于使用无TSV 的浮桥的封装解决方案,需要第1 行和第19 行。对于具有TSV 的封装解决方案,它们可以是可选的。在高达16 GT/s 的紧耦合模式下,需要vccfwdio 凸点。对于更高的速度,vccfwdio 凸点可以在封装中连接到vccio 凸点。

Implementation

注意:在图5-33 中,在55 um 间距时,所示的8 列凸点图的模块深度约为990 um。对于使用无TSV 的浮桥的封装解决方案,需要第1 行、第2 行和第35 行。对于具有TSV 的封装解决方案,它们可以是可选的。在高达16 GT/s 的紧耦合模式下,需要vccfwdio 凸点。对于更高的速度,vccfwdio 凸点可以在封装中连接到vccio 凸点。

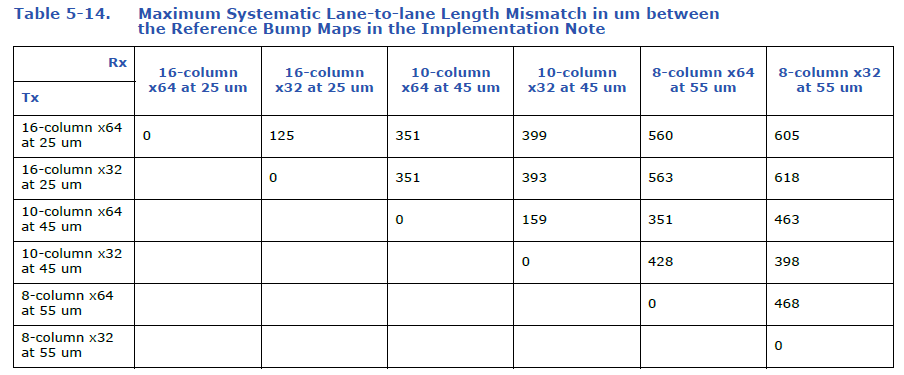

这些凸点图已进行优化,以最大程度减少通道间布线不匹配,当不同凸点间距的两个不同凸点互操作时,这种不匹配是不可避免的。表5-14 总结了代表性案例中由于凸点位置导致的最大偏斜。根据经验,每150 um 的不匹配会导致约1 ps 的时序偏斜。这种偏斜可以通过封装通道布局设计中的长度匹配工作来减少或消除。

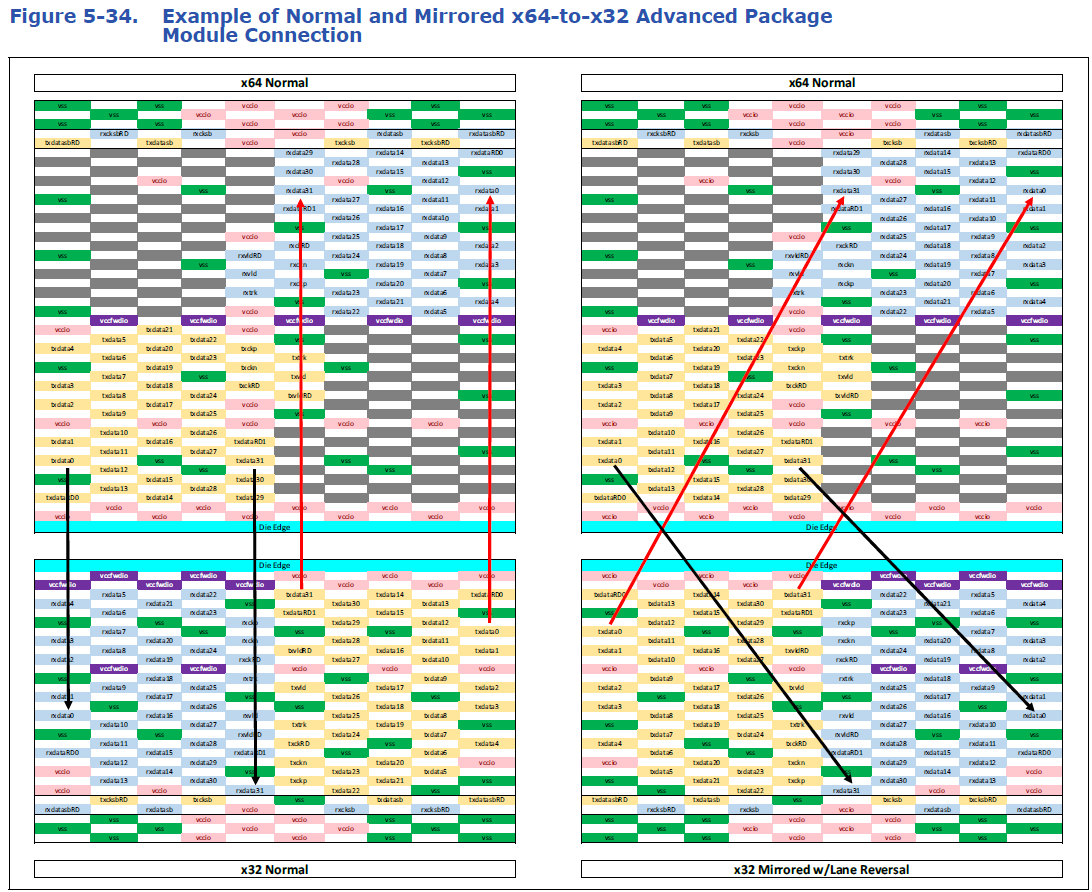

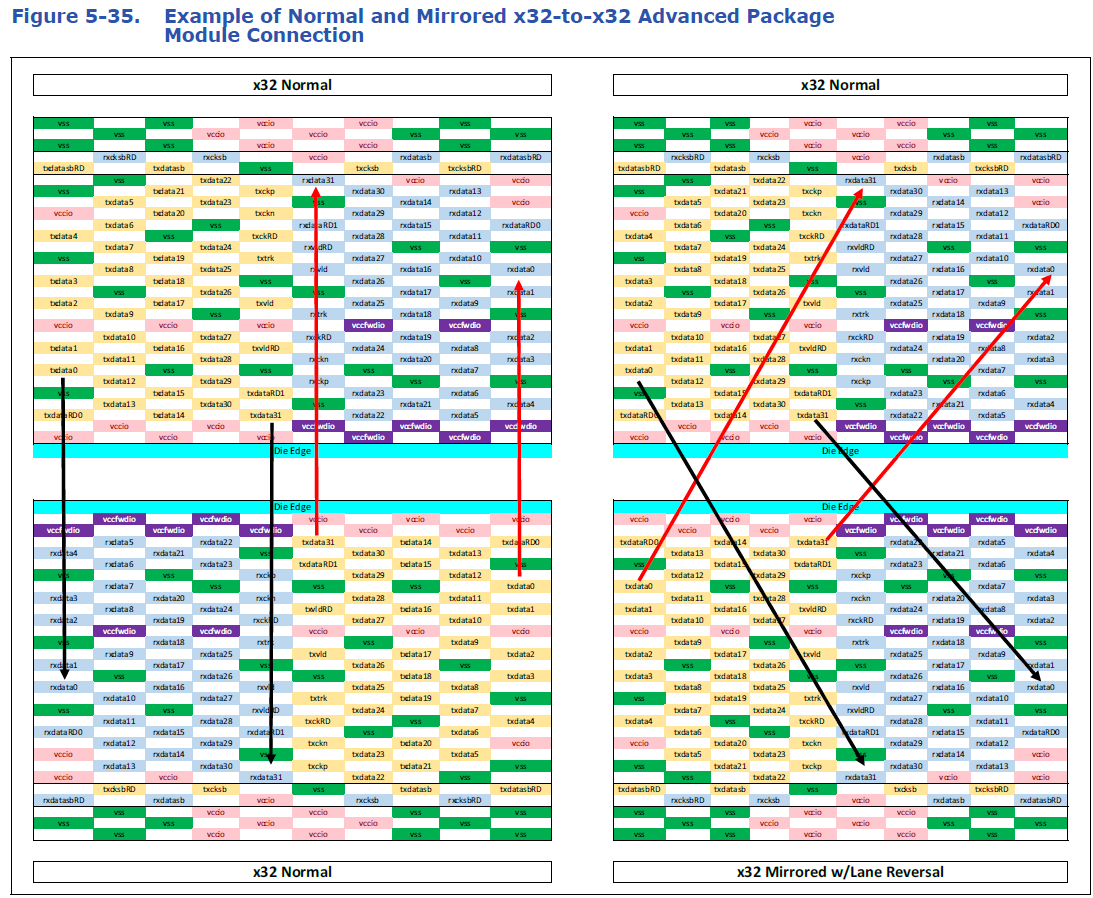

5.7.2.4 x64 and x32 Advanced Package Module Interoperability

x64 和x32 先进封装模块凸点图使x64 或x32、10 列、16 列或8 列模块的所有Tx 和Rx 组合在Normal-to-Normal 模块方向或Normal-to-Mirrored 模块方向之间能够互操作。然而,如果x64 到x32 模块或x32 到x32 模块分别具有如图5-34 和图5-35 所示的正常和镜像方向,TX 半部分和RX 半部分之间的信号走线将纵横交错,需要交错技术,这是指重新排列两个芯粒的信号凸点之间的物理连接,以优化中介层或基板上的布局和布线。它涉及在不改变网表或设计的电气功能的情况下,更改不同层上的连接或路线的顺序。此外,8 列、16 列和10 列模块之间的连接可能需要布线到相邻列(交错并跨越)。在所有情况下,所有这些连接都必须满足电气规格。

x64 模块支持与x32 模块的互操作性是可选的。当x64 模块支持x32 互操作性时,以下要求适用:

当x64 模块连接到x32 模块时,连接应始终包含在x64 模块的下半部分。即使下面描述 了x32 通道反转,也必须遵循这一点。

对于需要信号布线交错的组合,必须满足电气规格。

CKP-、CKN-、CKRD-、VLD-、VLDRD-、TRK-和边带相关引脚不允许通道反转。这些引脚需要适当连接。这些连接的交错是可以接受的。

x64 模块必须以x32 的方式支持通道反转模式(即,TD_P[31:0] = TD_L[0:31]。当x64 模块连接到x32 模块时,无论是正常方向还是镜像方向,高32 位都不使用,应禁用。

不允许较大宽度的单个模块同时与两个或多个较小宽度的模块互操作。例如,禁止将x64 先进封装模块物理连接到两个x32 先进封装模块。

可能需要额外的技术能力或层来完成数据/辅助信号的交错。

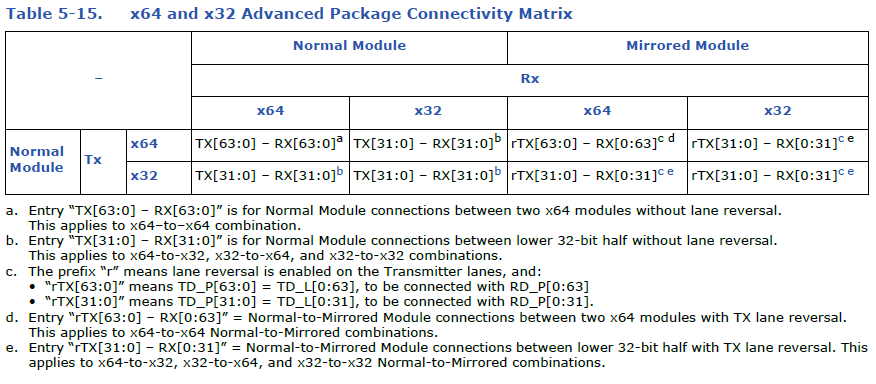

表5-15 总结了x64 和x32 模块在Normal-to-Normal 和Normal-to-Mirrored 模块方向上的组合之间的连接。该表适用于链路两侧的10 列、16 列或8 列模块的所有组合。

所定义的凸块矩阵可以在不同深度的凸块矩阵之间实现最佳偏斜,并且最坏情况下的走线到达偏斜预计在第5.3 节和第5.4 节中定义的相应数据速率的最大通道间偏斜限制内。图5-34 和图5-35 分别展示了正常和镜像的x64-to-x32 以及x32-to-x32 先进封装模块连接的示例。

5.7.2.5 Module Naming of Advanced Package Modules

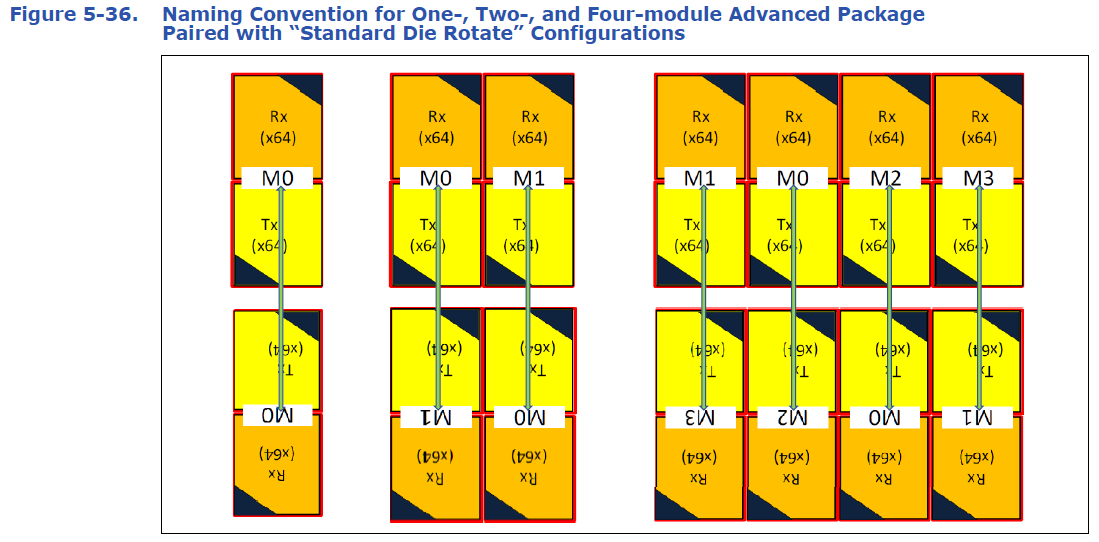

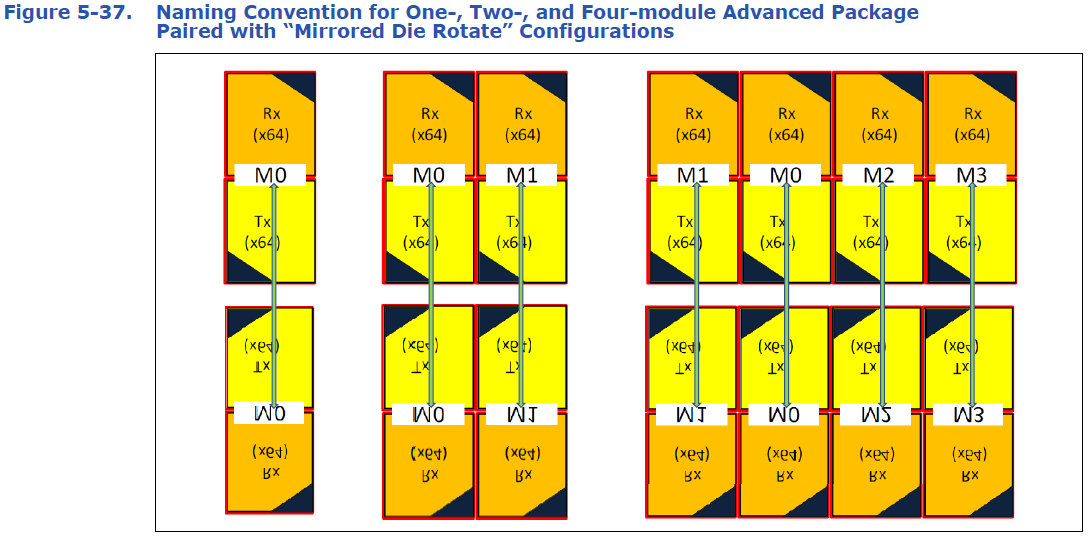

本节描述了多模块配置中x64 和x32 先进封装模块的模块命名约定。

模块命名被定义为有助于确定性地连接模块,这反过来又有助于最小化多模块PHY 逻辑(Multi-module PHY Logic,MMPL)中的复用要求。

M0、M1、M2 和M3 的命名将应用于通过MMPL 聚合的1、2 或4 个先进封装模块。图5-36 展示了1 个、2 个或4 个先进封装模块在与具有相同数量先进封装模块的“Standard Die Rotate”模块对应件相连接时的命名约定。

注意:图5-36 至图5-39 中的双头箭头表示模块到模块的连接。

图5-37展示了1个、2个或4个先进封装模块在与具有相同数量先进封装模块的“Mirrored Die Rotate”对应件相连接时的命名约定。

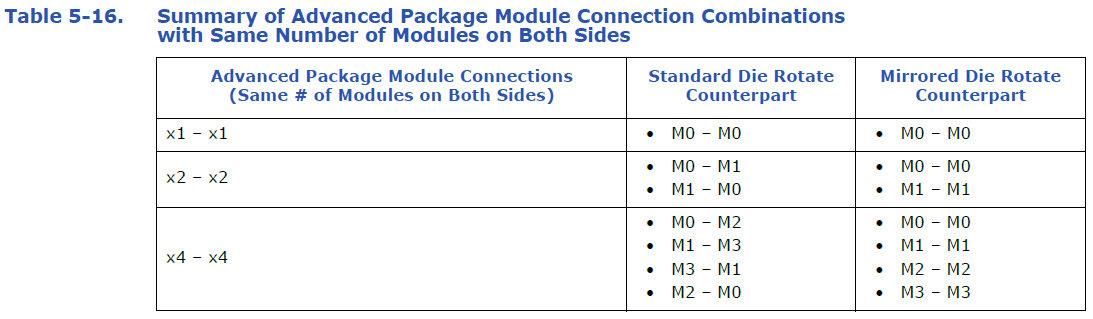

表5-16 总结了图5-36 和图5-37 中所示组合之间的连接。

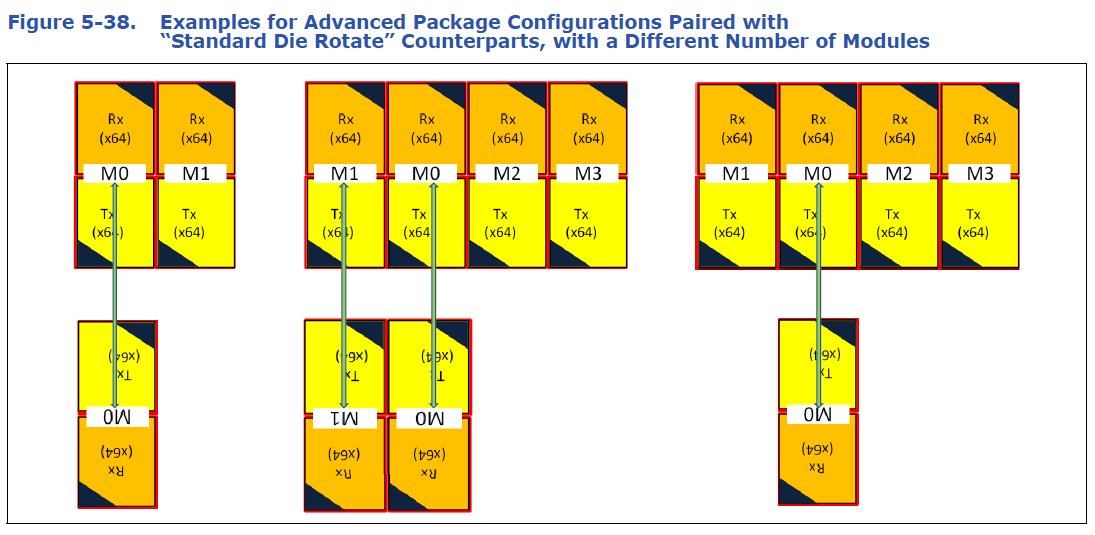

图5-38 展示了1 个、2 个或4 个先进封装模块在与具有不同数量先进封装模块的“Standard Die Rotate”对应件相连接时的命名约定。

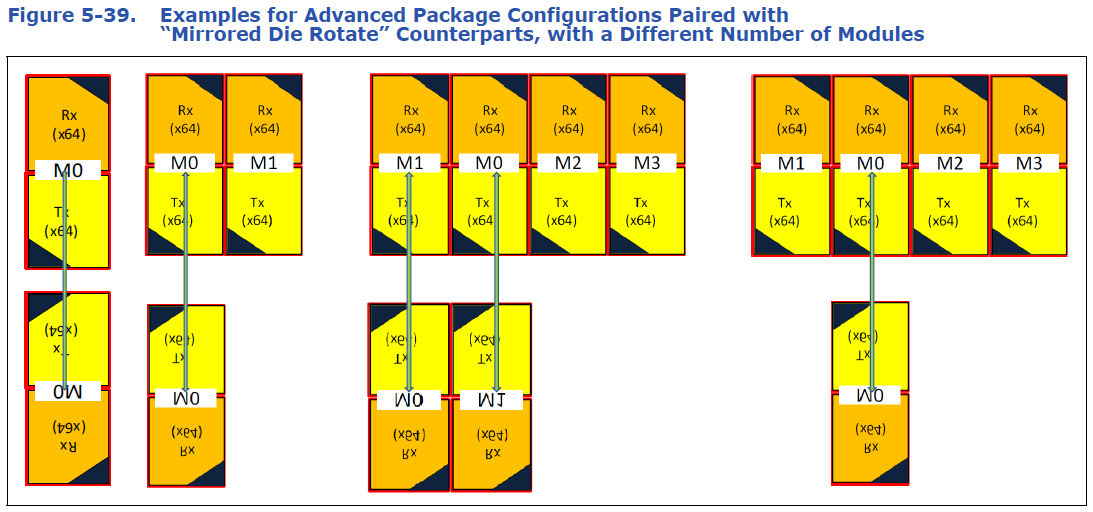

图5-39展示了1个、2个或4个先进封装模块在与具有不同数量先进封装模块的“Mirrored Die Rotate”对应件相连接时的命名约定。

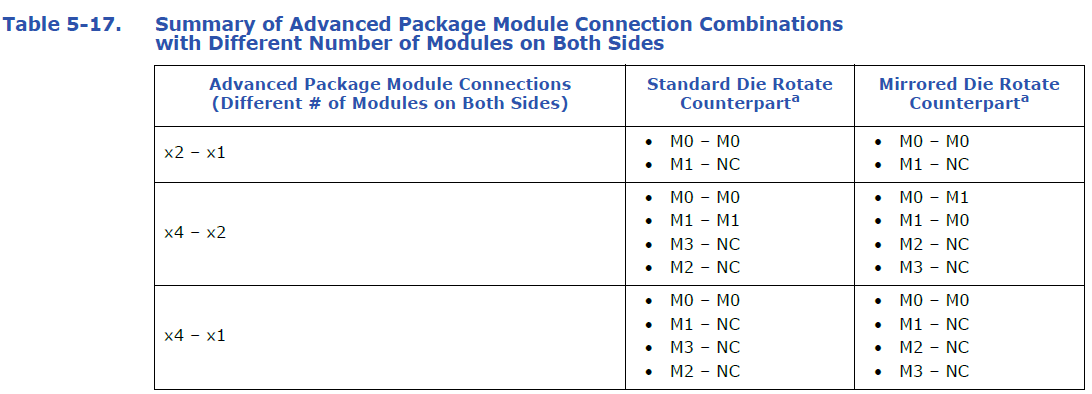

表5-17 总结了图5-38 和图5-39 中所示组合之间的连接。

5.7.3 Standard Package

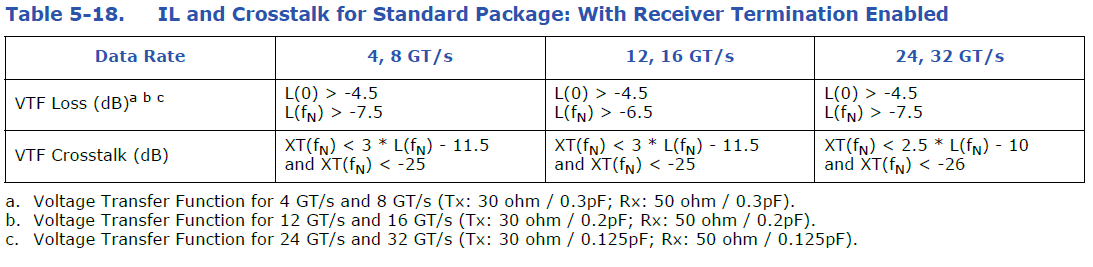

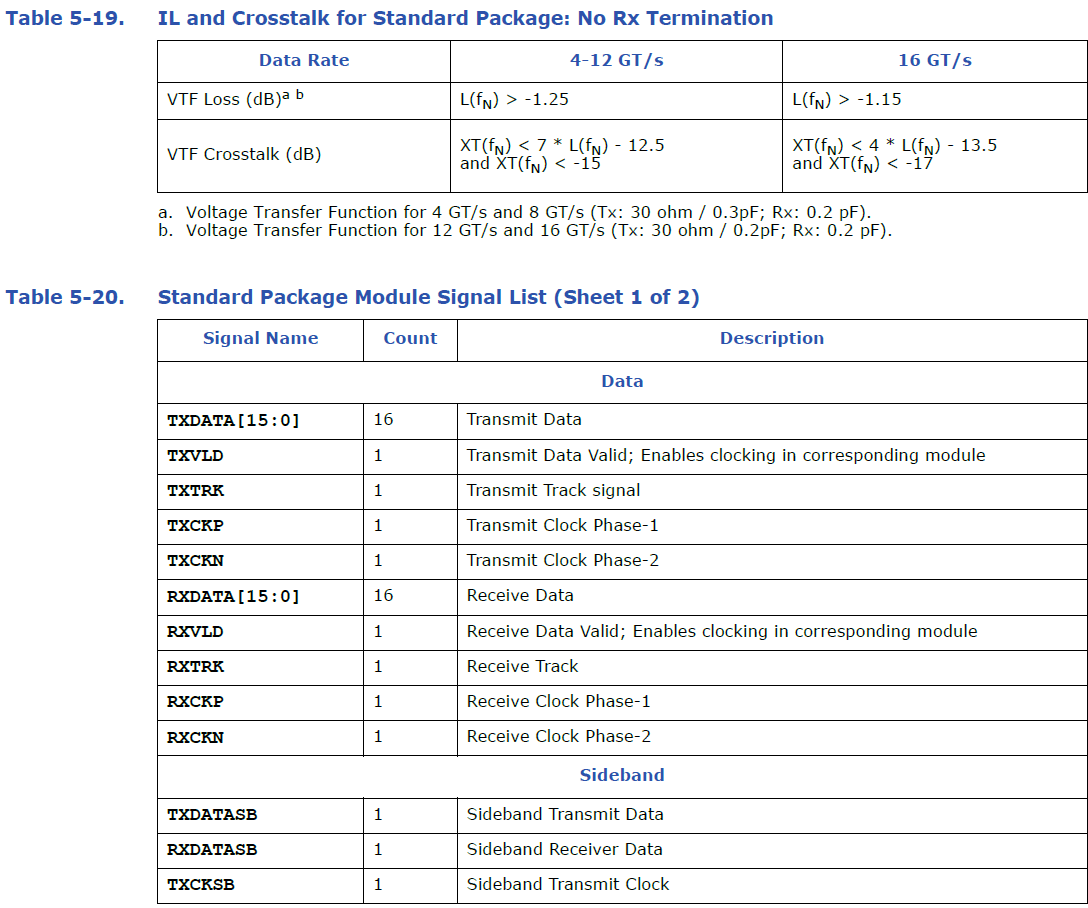

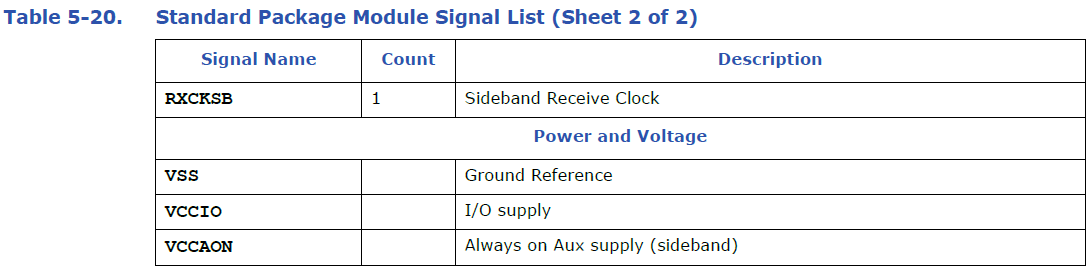

互连通道应设计为具有50 欧姆的特性阻抗。带有接收器端接的奈奎斯特频率下的插入损耗和串扰要求在表5-18 中定义。

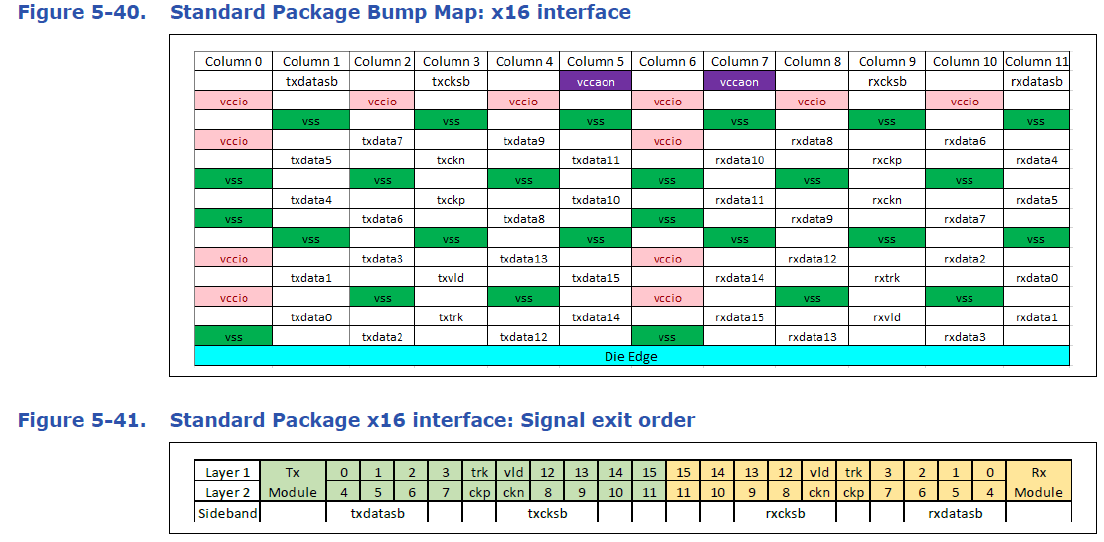

5.7.3.1 x16 Standard Package Module Bump Map

图5-40 和图5-42 分别展示了x16(一个模块)和x32(两个模块)标准封装的参考凸点矩阵。

强烈建议遵循图5-40 中提供的一个模块的凸点矩阵和图5-42 中提供的两个模块的标准封装的凸点矩阵。凸点图的左下角将被视为凸点矩阵的“原点”。

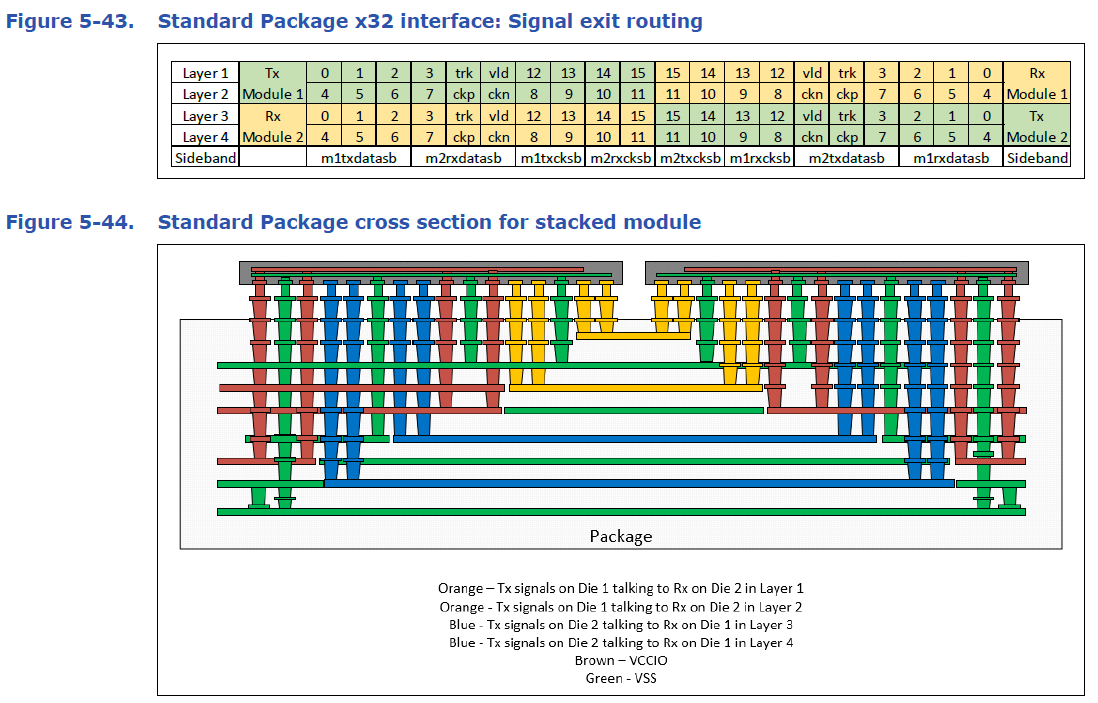

x16 和x32 标准封装凸点矩阵的信号退出顺序分别如图5-41 和图5-43 所示。

对于标准封装凸点矩阵,必须遵循以下规则:

一列中的信号必须保留。例如,对于图5-40 所示的x16(一个模块标准封装),第1 列必须包含信号:txdata0、txdata1、txdata4、txdata5 和txdatasb。

信号必须按照图5-41 所示的顺序离开凸块区域。第1 层和第2 层是标准封装中的两个 不同的信号布线层。

强烈建议遵循凸点矩阵中所示的电源和接地模式。必须确保提供足够的电源和接地凸点,以满足通道特性(FEXT 和NEXT)和供电要求。

对于实例化标准封装凸点矩阵的多个模块,必须遵循以下规则:

当观察Die,使得UCIe 模块位于南侧时,在从左到右沿着Die 边缘的一个模块内,Tx应始终先于Rx。

当实例化多个模块时,这些模块必须以相同的方向逐步排列并邻接。不允许水平或垂直镜像。

如果需要更高的Die 边缘带宽密度,则允许在邻接之前堆叠两个模块。如果堆叠两个模块,封装可能需要至少支持四层布线用于UCIe 信号布线。堆叠标准封装模块实例化的示例见图5-42。

如果只实例化一个堆叠模块,当观察Die 使得UCIe 模块在南侧时,在从左到右沿着 Die 边缘的一个模块内,Tx 应始终先于Rx。

当实例化多个堆叠模块时,这些模块必须以相同的方向逐步排列并邻接。

不允许水平或垂直镜像。

注意:堆叠模块的信号布线示例见图5-44。

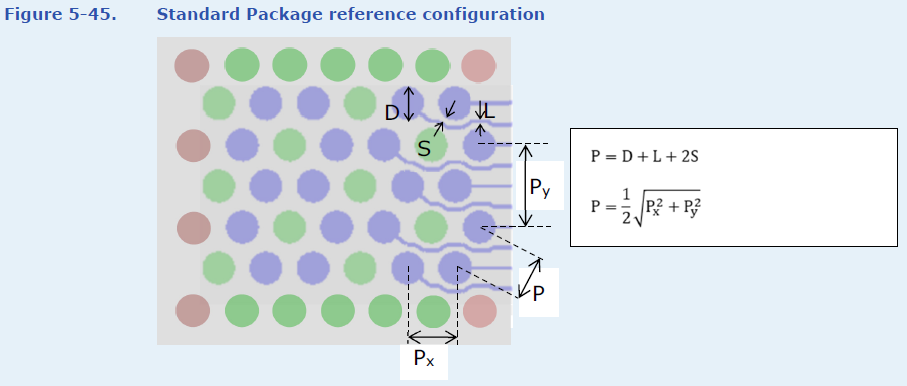

图5-45 展示了基于凸块间距和布线设计规则的带有标准封装通道的分支(breakout)设计参考。

・每个布线层4 行深度分支

・示例1:Py = 190.5 um,Px = 111.5 um,P = 110 um

・示例2:Py = 190.5 um,Px = 177 um,P = 130 um

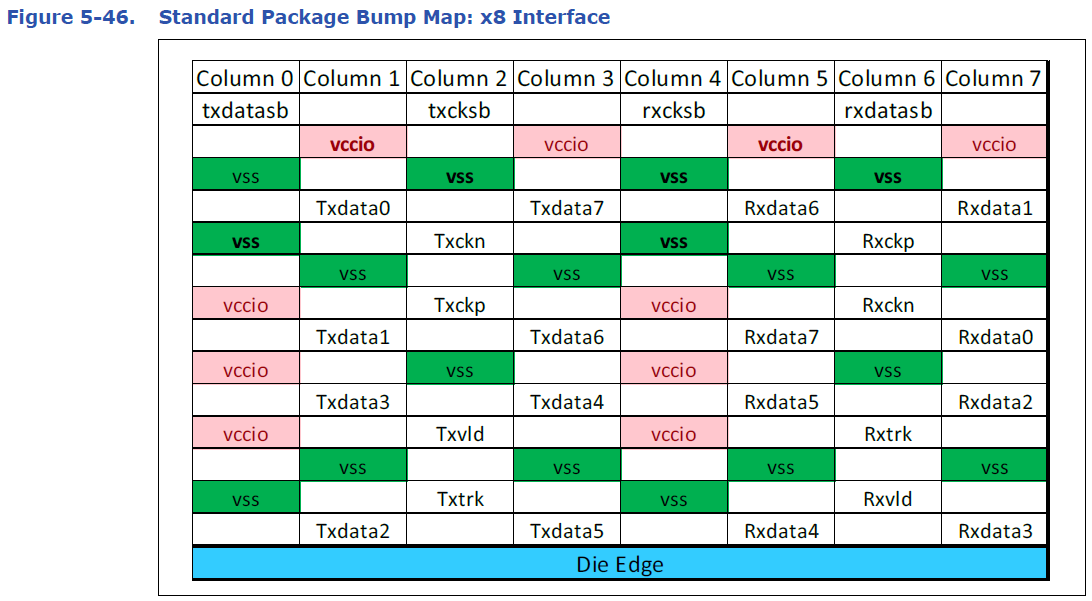

5.7.3.2 x8 Standard Package Module Bump Map

在需要UCIe 高带宽但设计为先进封装设计或出于任何其他原因的场景中,设计可以选择添加UCIe-S 端口用于分类/预键合测试目的。为了在支持这种UCIe-S 使用时减少芯粒的Die边缘,提供了x8 版本的UCIe-S。这是除了可用的标准x16 UCIe-S 端口选项之外的额外选项。UCIe-S x16 模块可以选择支持连接到UCIe-S x8 模块,并且在支持时,连接始终在其较低的x8 通道(即通道7:0)上。UCIe-S x8 设计必须支持通道反转和降级模式操作到x4。支持连接到x8 模块的UCIe-S x16 设计必须支持通道反转,并且在连接到x8 模块时,其较低的8 个通道必须支持降级模式操作到x4。

UCIe-S x8 支持仅限于单个模块配置。当UCIe-S x8 端口连接到多模块x16 端口时,它始终连接到Module 0 UCIe-S x16。

强烈建议遵循图5-46 中提供的凸块矩阵。凸块图的左下角将被视为凸块矩阵的“原点”。对于x8 凸点矩阵,必须遵循5.7.3.1 节中提到的关于x16 和x32 标准封装凸点矩阵的相同规

则。

5.7.3.3 x16 and x8 Standard Package Module Interoperability

x8 凸点矩阵要么连接到另一个x8 凸点矩阵,要么连接到x16 凸点矩阵的位[7:0]。

5.7.3.4 Module Naming of Standard Package Modules

本节描述了多模块配置中标准封装模块的模块命名约定。

M0、M1、M2 和M3 的命名将适用于通过MMPL 聚合的1、2 或4 个标准封装模块,包括堆叠和非堆叠的配置组合。

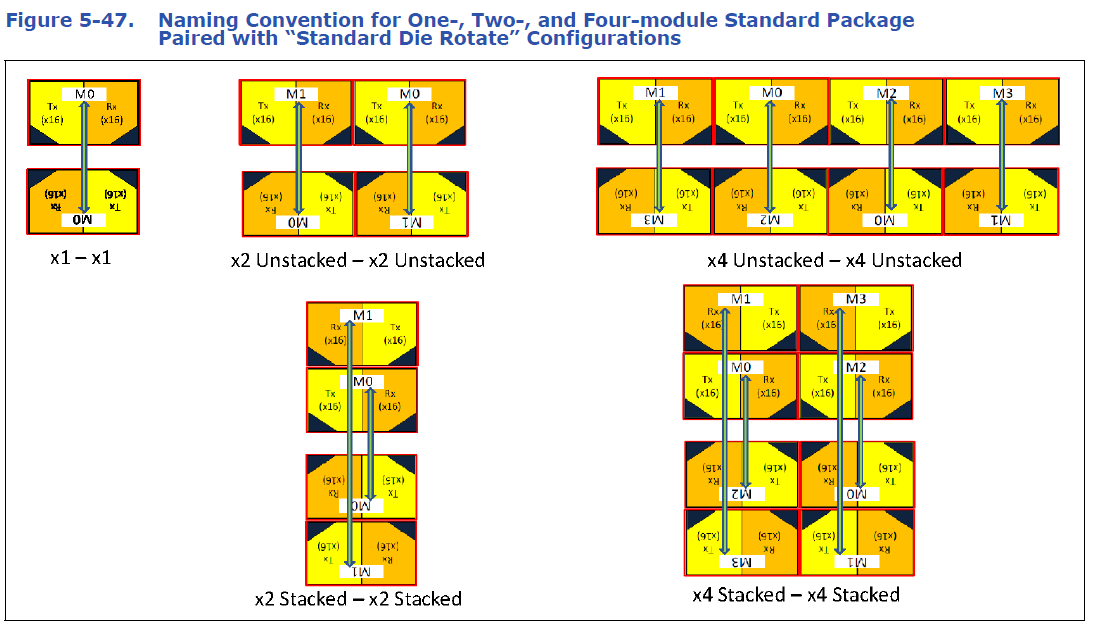

图5-47 展示了1、2 或4 个标准封装模块在与其具有相同数量标准封装模块的“Standard Die Rotate”模块对应物连接时的命名约定,具有相同的堆叠或相同的非堆叠配置。

注意:图5-47 至图5-51 中的双头箭头表示模块到模块的连接。

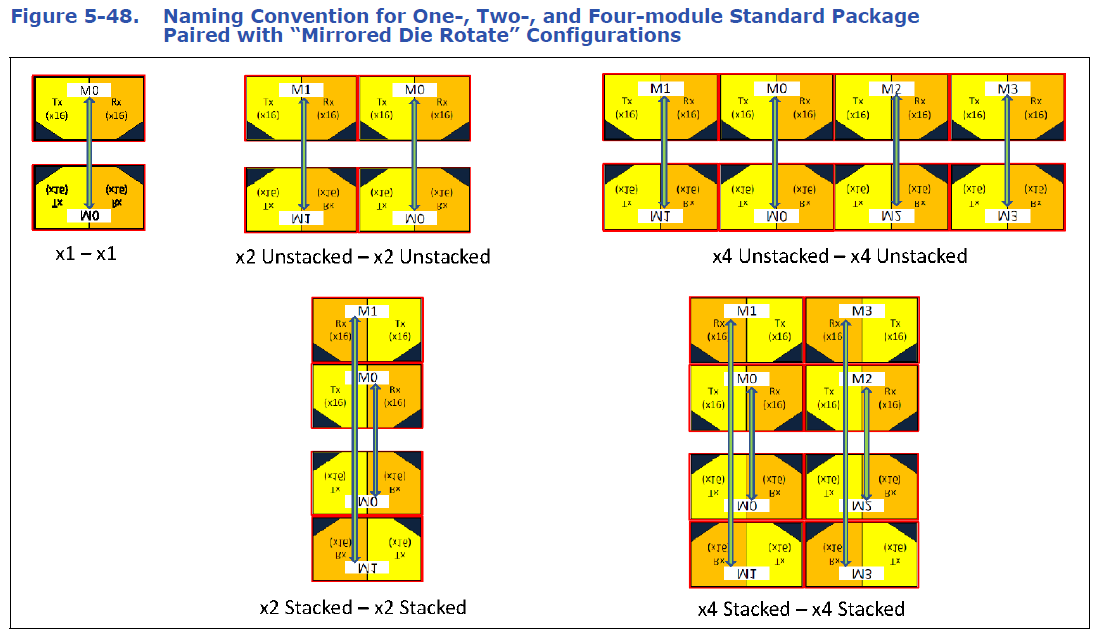

图5-48 展示了1、2 或4 个标准封装模块在与其具有相同数量标准封装模块的“Mirrored Die Rotate”对应物连接时的命名约定,具有相同的堆叠或相同的非堆叠配置。

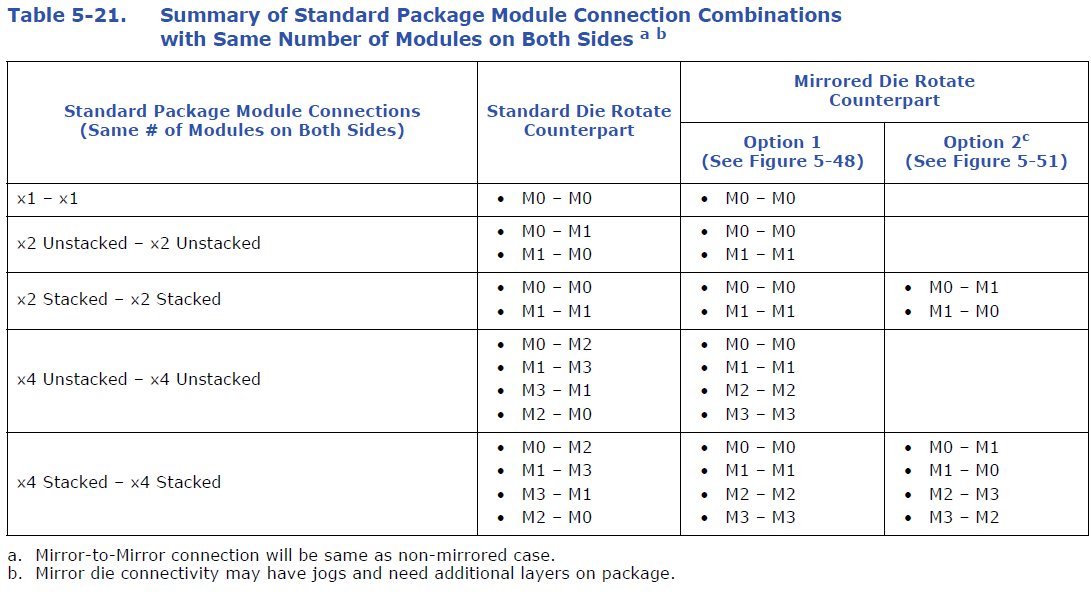

表5-21 总结了图5-47 和图5-48 中所示组合之间的连接。

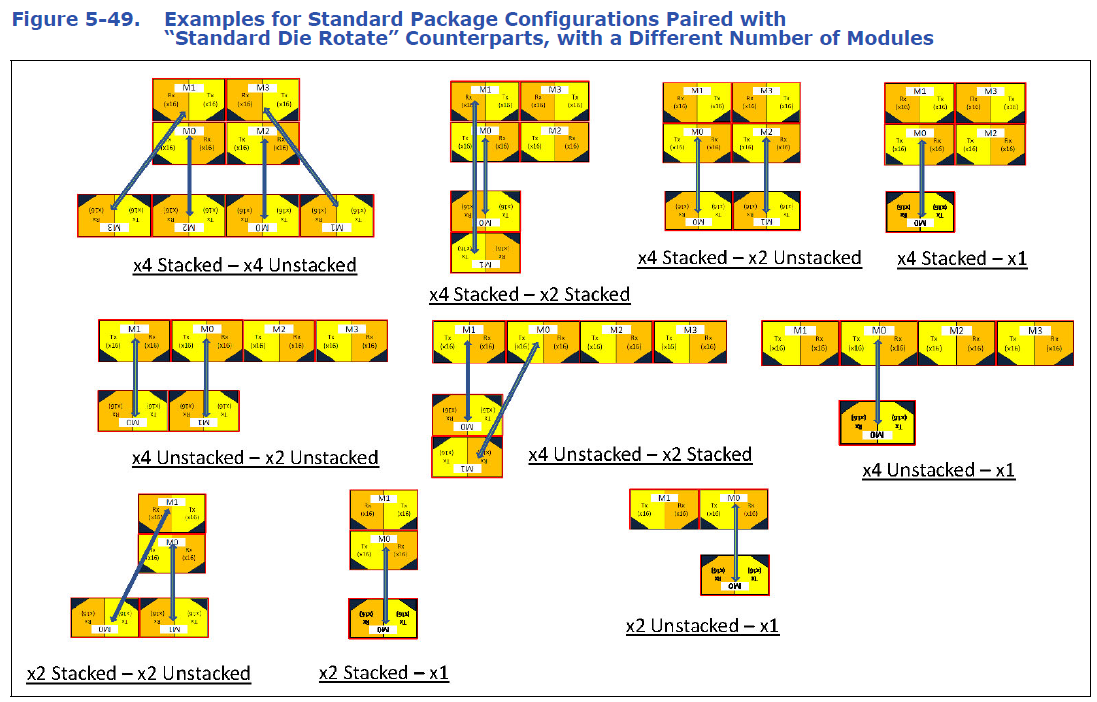

图5-49 展示了1、2 或4 个标准封装模块在与其具有不同数量标准封装模块的“Standard Die Rotate”对应物连接时的命名约定。

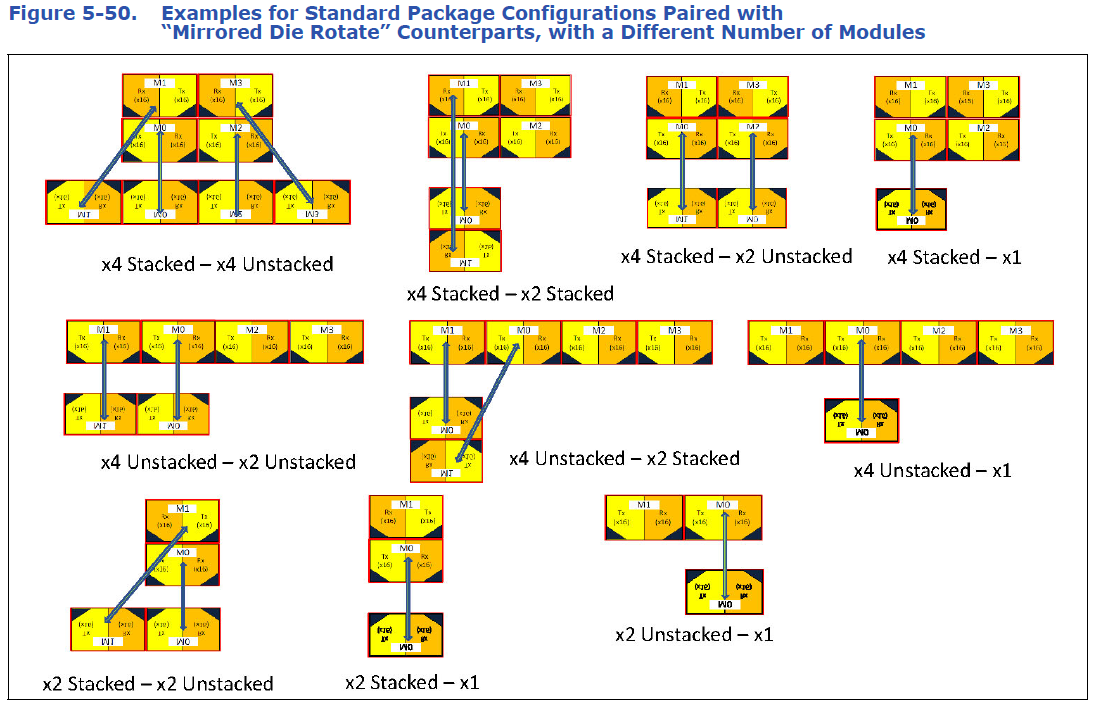

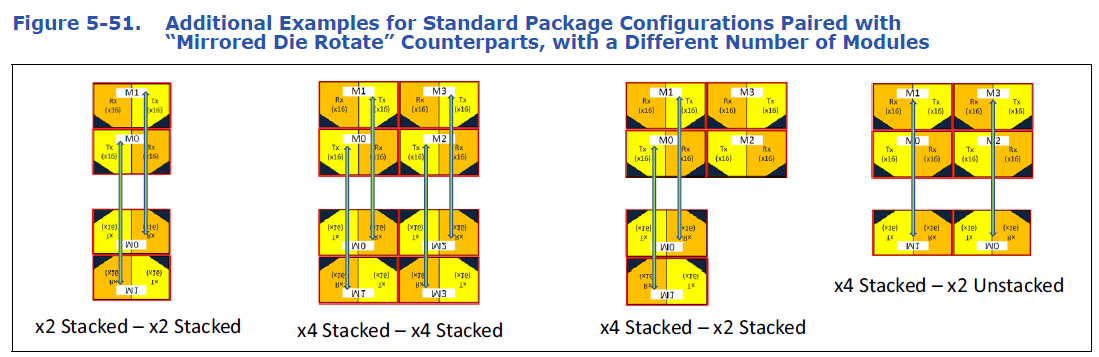

图5-50 展示了1、2 或4 个标准封装模块在与其具有不同数量标准封装模块的“Mirrored Die Rotate”对应物连接时的命名约定。

图5-51 说明了某些镜像情况的可能替代连接,以允许在更多布线层与由于潜在串扰导致的最大数据速率降低之间进行设计选择,如表5-21 和表5-22 中的Option 2 所示。

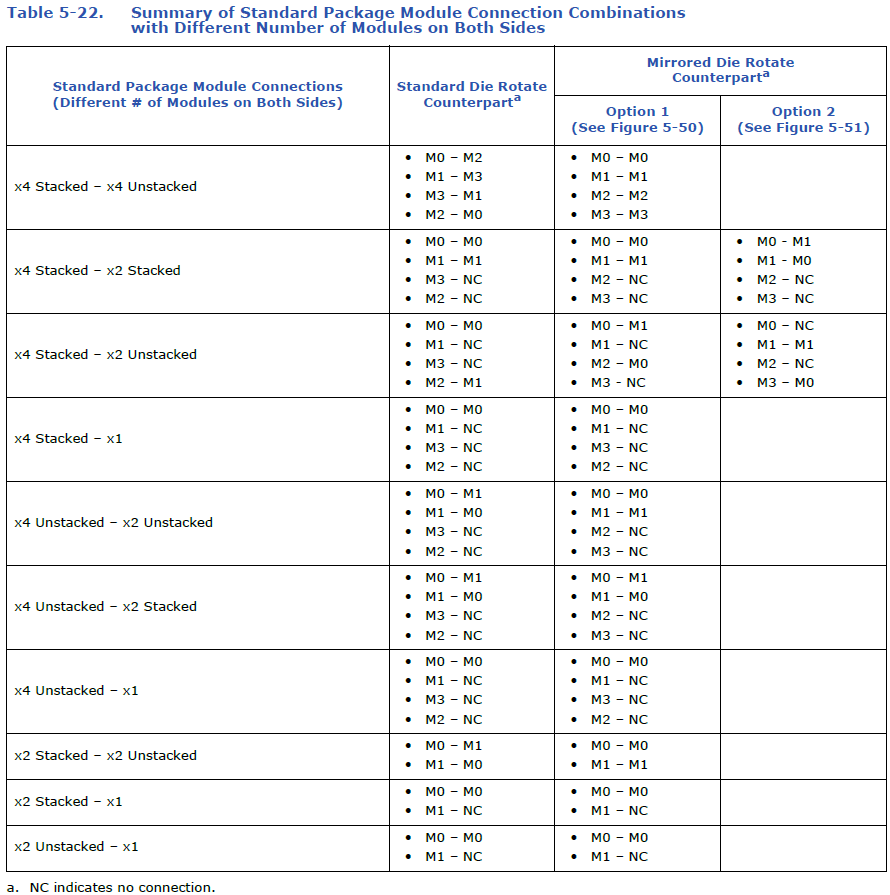

表5-22 总结了图5-49、图5-50 和图5-51 中所示组合之间的连接。

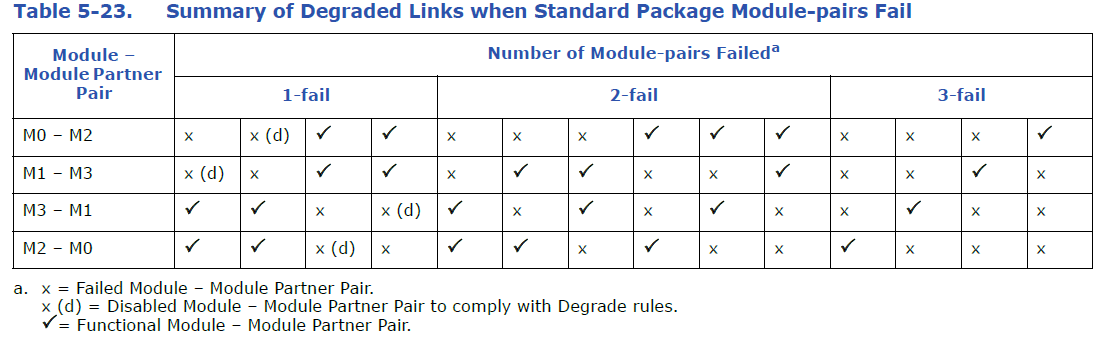

5.7.3.4.1 Module Degrade Rules

在2 模块或4 模块链路中,如果一个或多个模块对出现故障,链路将降级,并应遵循以下规则:

1. 降级的链路应为一个或两个模块,不应为三个模块。

a. 对于4 模块链路:

i. 如果任何一个模块对出现故障,它应降级为2 模块链路。

ii. 如果任何两个模块对出现故障,它应降级为2 模块链路。

iii. 如果任何三个模块对出现故障,它应降级为1 模块链路。

b. 对于2 模块链路:

i. 如果任何一个模块对出现故障,它应降级为1 模块链路。

2. 对于4 模块链路,如果只有一个模块对出现故障,属于4 模块“同一半”(沿Die 边缘)的一个额外模块对将被禁用/降级。

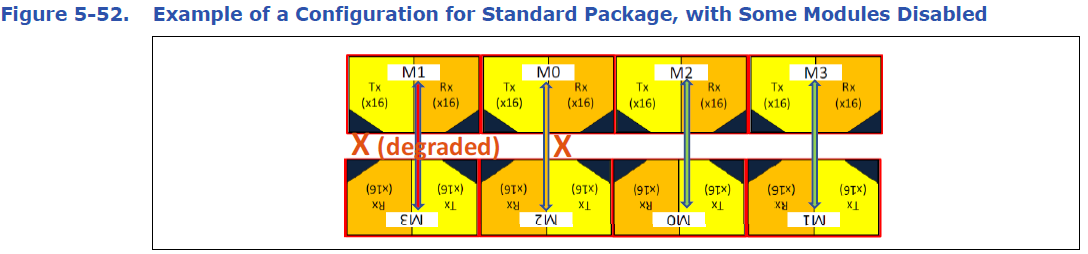

图5-52 展示了一个示例,其中一个x4 非堆叠连接到一个x4 非堆叠“Standard Die Rotate”对应物,且有一个M0-M2 对出现故障。其左侧的M1-M3 对应相应地被禁用,以符合上述定义的规则,这在表5-23 中将被表示为“x (d)”。

注意:图5-52 中的双头箭头表示模块到模块的连接。

表5-23 总结了对于x4 非堆叠到x4 非堆叠配置,如果有一个、两个或三个故障模块对,所

产生的降级链路。

所有其他模块配置应遵循上述相同的模块降级规则。

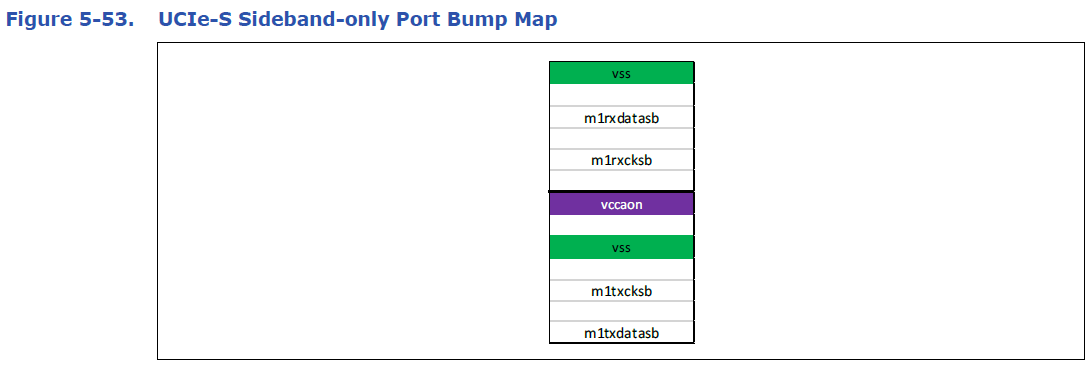

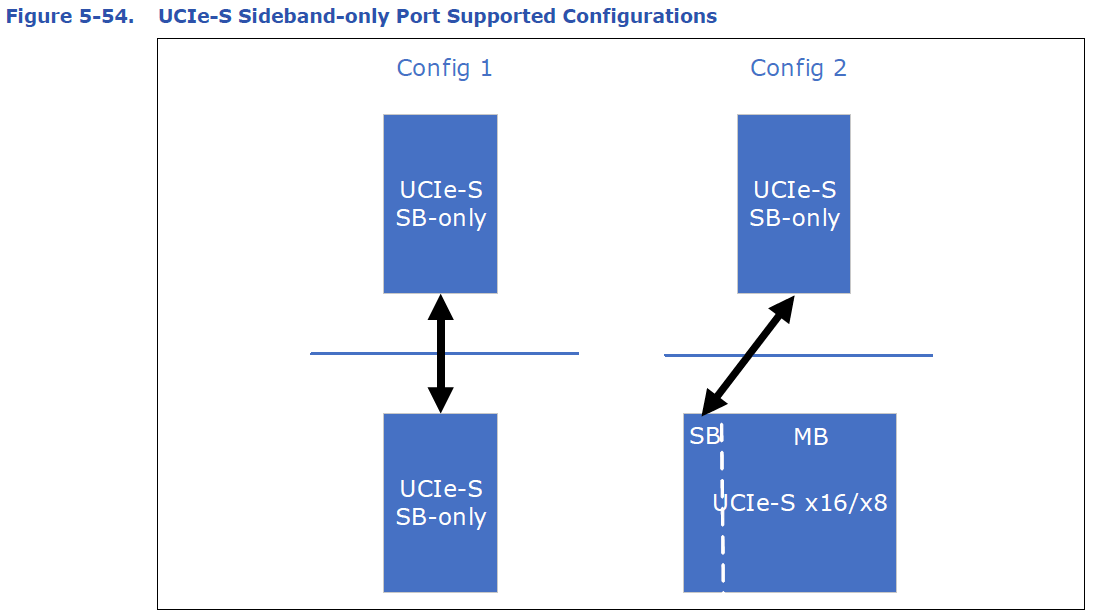

5.7.4 UCIe-S Sideband-only Port

出于测试/可管理性目的,也允许使用UCIe-S Sideband-only 端口。对于仅边带配置,到边带端口的RDI 信号与边带加主带配置的相同(后者的详细信息见第10.0 章)。

图5-53 展示了UCIe-S Sideband-only 端口的凸点图。图5-54 展示了UCIe-S Sideband-only 端口的支持配置。

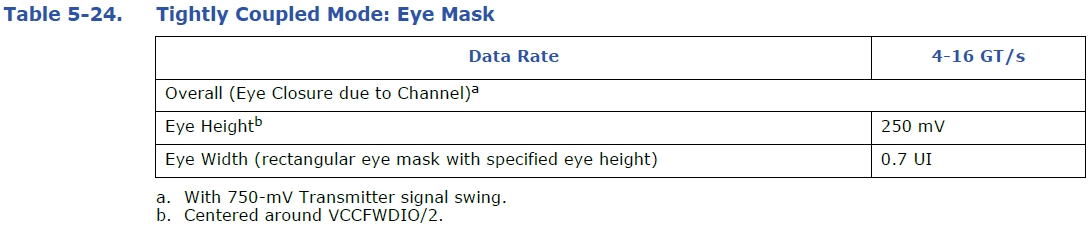

5.8 Tightly Coupled Mode

紧耦合PHY 模式定义为满足以下两个条件时:

Tx 和Rx 之间共享电源,或从Tx 到Rx 的转发电源

通道支持表5-24 中定义的更大眼图掩码

在此模式下,没有接收器端接,并且发送器必须提供全摆幅输出。在此模式下,可以对PHY电路进行进一步优化并降低功耗。例如,可以使用调谐逆变器代替前端放大器。诸如电压基准之类的训练复杂性可以简化。

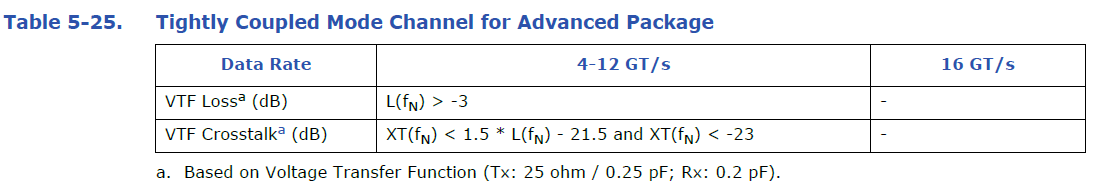

损耗和串扰要求遵循相同的VTF 方法,调整到表5-24 中定义的眼图掩码。表5-25 显示了奈奎斯特频率下的规格。

直流和奈奎斯特频率fN 之间的损耗和串扰规格遵循5.7.2.1 节中定义的相同方法。

尽管此模式的使用主要用于先进封装,但当两个Die 彼此靠近且接收器必须未端接时,它也可用于标准封装。

5.9 Interconnect redundancy Remapping

5.9.1 Advanced Package Lane Remapping

先进封装模块中支持互连通道重映射,以提高组装良率和恢复功能。每个模块支持:

四个用于数据的冗余凸点

一个用于Clock 和Track 的冗余凸点

一个用于Valid 信号的冗余凸点

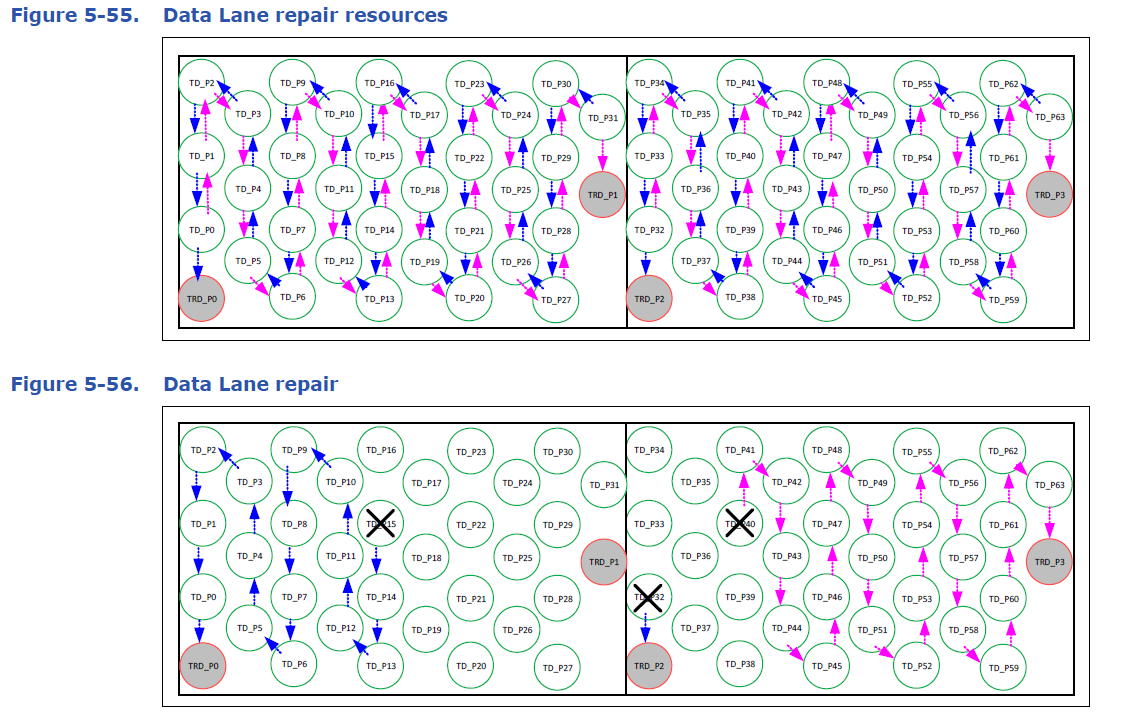

对于x64 Advanced Package 模块,用于数据修复的四个冗余凸点分为两组,每组两个。图5-55展示了x64 Advanced Package 模块数据信号冗余凸点分配的图示。TRD_P0 和TRD_P1 分配给较低的32 个数据通道,TRD_P2 和TRD_P3 分配给较高的32 个数据通道。每组允许重新映射最多两个通道。例如,TD15 是下半部分的故障通道,TD_P32 和TD_P40 是上半部分32 个通道中的故障通道。图5-56 展示了故障通道的通道重映射。

对于x32 Advanced Package 模块,在图5-55 和图5-56 中,只有较低的32 个数据通道以及TRD_P0 和TRD_P1 适用。

Data、Clock、Track 和Valid 信号的通道重映射的详细信息和实现见第4.3 节。

5.9.2 Standard Package Lane remapping

标准封装模块不支持通道修复。

5.10 BER requirements, CRC and retry

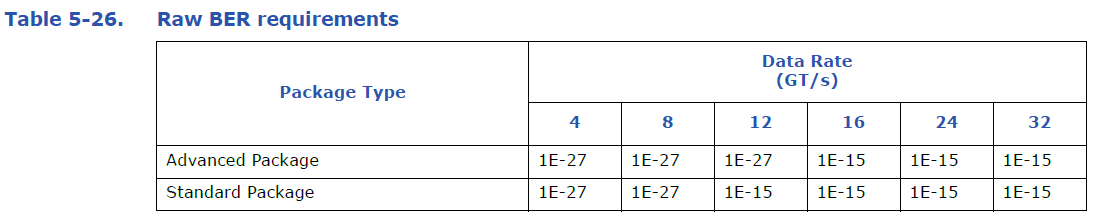

基于5.7 节中定义的信道可达范围的误码率要求如表5-26 所示。对于1E-15 的误码率,需要诸如CRC 和重试之类的错误检测和纠正机制,以实现显著小于1 的所需故障时间(Failure In Time,FIT)率(1 FIT = 1 个设备在109小时内出现故障)。UCIe 规范中定义的CRC 和重试在第3.0 章中有详细说明。对于1E-27 的误码率,可以使用奇偶校验或CRC,并且必须调用适当的错误报告机制,以确保FIT 显著小于1。

5.11 Valid and Clock Gating

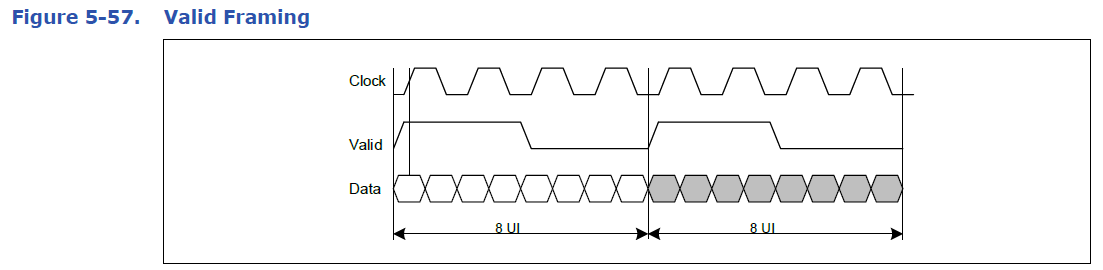

有效信号用于界定传输数据。对于8 UI 数据包的单次传输,有效信号在前4 个UI 被置位,在后4 个UI 被复位。图5-57 显示了两个连续的8 UI 数据包的传输。

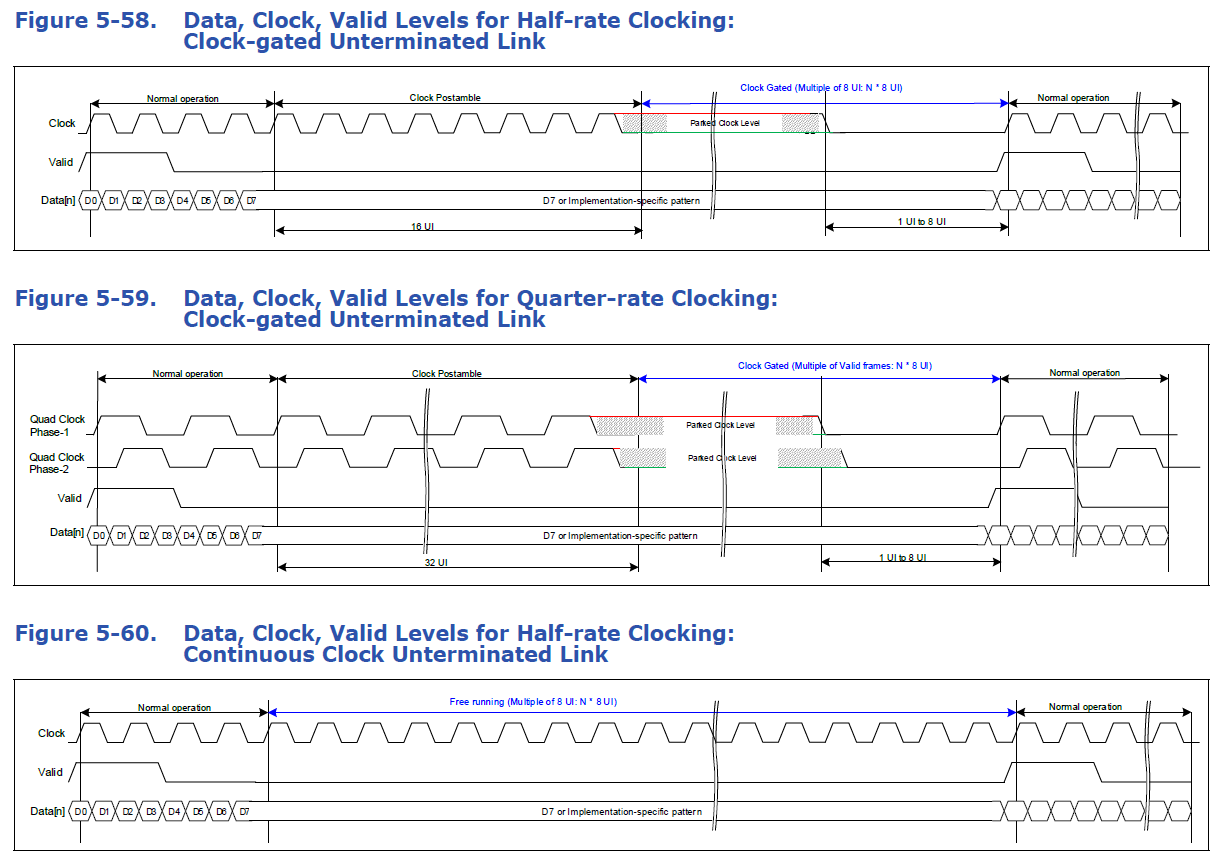

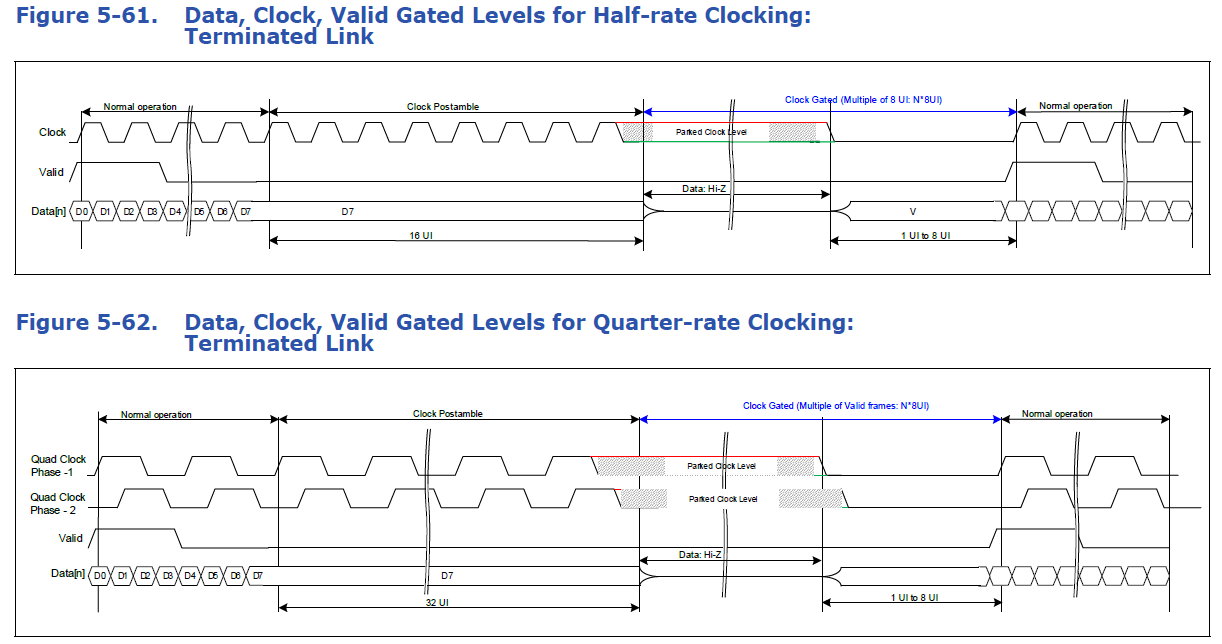

如4.1.3 节所述,对于半速率时钟,仅当Valid 信号在后导时钟的16 个UI(8 个周期)保持为低,对于四分之一速率时钟,仅当Valid 信号在后导时钟的32 个UI(8 个周期)保持为低时,时钟才必须被门控,除非协商了自由运行时钟模式。

空闲状态是指在主带上没有数据传输。在空闲状态期间,Data、Clock 和Valid 通道必须保持如下值:

如果链路未端接(所有先进封装和未端接的标准封装链路),一些数据通道发送器被允许保持翻转,翻转密度与加扰数据相同,但不推进加扰器状态。其余数据通道发送器必须保持最后发送位的数据。有效通道必须保持为低,直到下一次正常传输。

— 在选通模式下,对于半速率时钟(满足后序要求后),处于时钟门控状态的时钟电平在连续的时钟门控事件期间必须在差分高电平和差分低电平之间交替。对于四分之一速率时钟,处于时钟门控状态的时钟电平必须在两个相位(相位1 和相位2)同时在高电平和低电平之间交替。在正常操作之前,对于半(四分之一)速率时钟,时钟必须驱动差分(同时)低电平至少1 个UI 或最多8 个UI。总时钟门控周期必须是8 个UI 的整数倍。示例见图5-58 和图5-59。

— 在连续模式下,时钟保持自由运行(示例见图5-60)。总空闲周期必须是8 个UI的整数倍。

如果链路已端接(标准封装端接链路),一些数据通道发送器被允许保持翻转,翻转密度与加扰数据相同,但不推进加扰器状态。其余数据通道发送器保持最后发送位的数据。

有效通道必须保持为低,直到下一次正常传输。请注意,保持发送器翻转将导致额外的功率损耗,应谨慎使用。

— 在选通模式下,对于半速率时钟(满足后序要求后),处于时钟门控状态下的时钟电平在连续的时钟门控事件期间必须在差分高电平和差分低电平之间交替。对于四分之一速率时钟,处于时钟门控状态下的时钟电平必须在两个相位(相位1 和相位2)同时在高电平和低电平之间交替。发送器必须将数据通道预处理为0 或1(V),并且在正常传输之前,对于半(四分之一)速率时钟,时钟必须驱动差分低电平至少1 个UI 或最多8 个UI。总时钟门控周期必须是8 个UI 的整数倍。示例见图5-61 和图5-63。

— 在连续模式下,时钟保持自由运行(示例见图5-64)。发送器必须将数据通道预处理为0 或1(V)至少1 个UI 或最多8 个UI。总空闲周期必须是8 个UI 的整数倍。

注意:进入和退出高阻态是模拟转换。高阻态代表发送器状态,在此期间由于接收器端接到地,实际电压将被拉低。

5.12 Electrical Idle

一些训练状态在发送器和接收器等待生成和接收模式时需要电气空闲。

本规范中关于主带上的电气空闲描述为:当发送器和接收器启用时;Clock、Valid和Track 通道保持低电平,Clock 处于高电平和低电平。

5.13 Sideband signaling

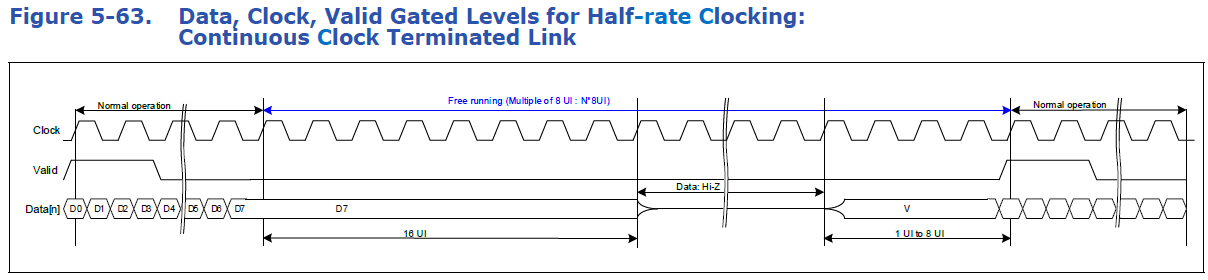

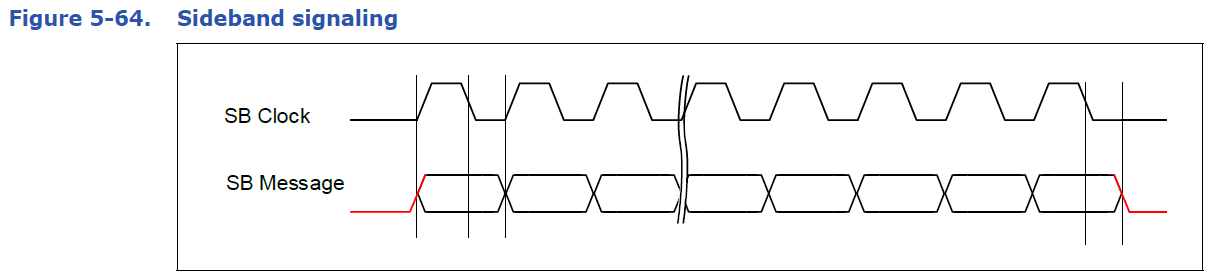

每个模块支持一个边带接口。边带是一个用于发送和接收方向的双信号接口。边带数据是一个800 MT/s 的单数据速率信号,具有800 MHz 源。边带必须在源自辅助时钟(AUXCLK)源的电源和时钟上运行,该源始终开启(VCCAON)。有关AUXCLK 的详细信息,请参阅第5.13.2 节。

边带数据与选通脉冲的正沿边沿对齐发送。接收器必须用选通脉冲对输入数据进行采样。选通脉冲的负沿用于对数据进行采样,因为数据使用单数据速率信令,如图5-64 所示。边带传输在4.1.5 节中有描述。

对于先进封装模块,边带接口支持冗余。边带初始化和修复在第4.5.3.2 节中描述。标准封装模块上没有冗余且不支持通道修复。

5.13.1 Sideband Electrical Parameters

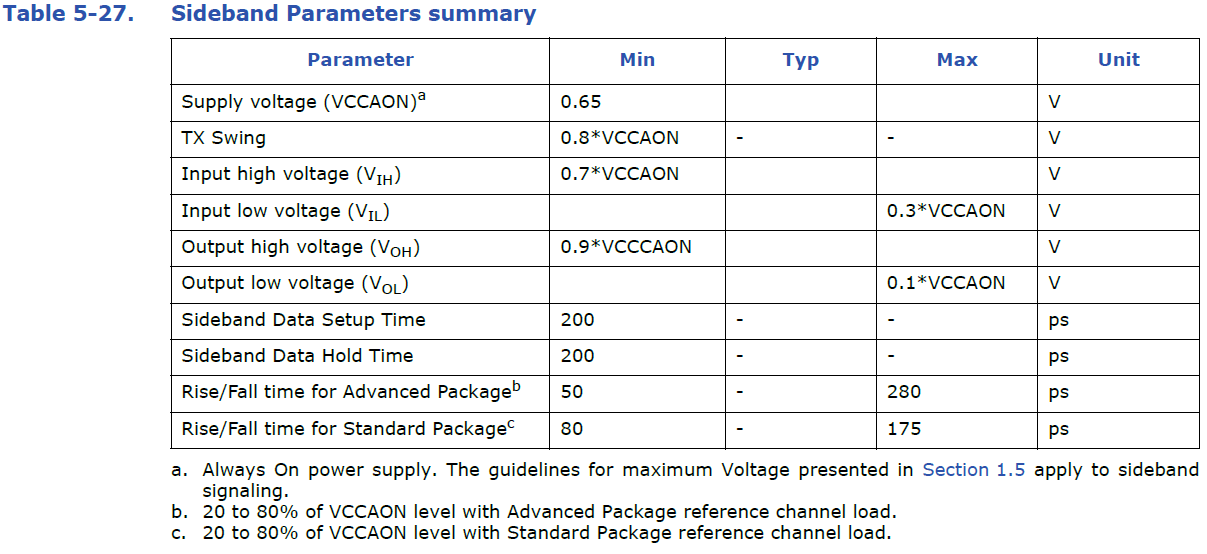

表5-27 展示了边带电气参数。

强烈建议边带I/O 链路的两侧共享相同的电源轨。

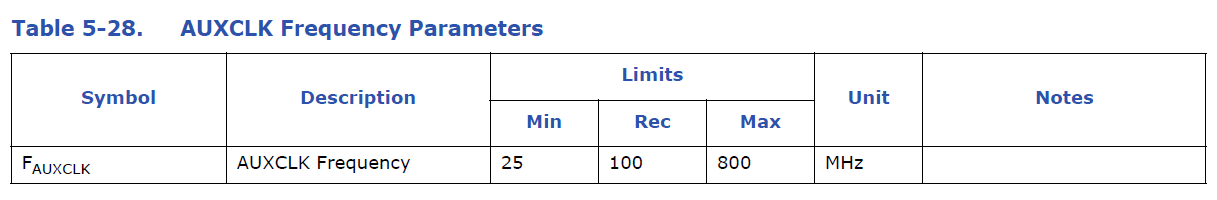

5.13.2 Auxiliary Clock (AUXCLK)

辅助时钟(AUXCLK)可以来自任何时钟源。尽管其他时钟频率也是可能的,但建议每个芯粒也应使用100 MHz 时钟源。表5-28 列出了允许的辅助时钟频率范围。表中列出的最小和最大频率表示限制,并不表示需要支持整个频率范围。如果始终开启,参考时钟(REFCLK;见第5.1.2 节)可以使用。允许扩频时钟(Spread-Spectrum Clocking,SSC)。AUXCLK 与REFCLK 相比具有更严格的容差。

6 UCIe-3D

6.1 Introduction(介绍)

3D 异构集成技术为开发新的电子系统提供了机会,与2D 和2.5D 架构相比,具有更高的带宽和更低的功耗优势。3D 将使数据移动规模对于单片、2D 或2.5D 方法不切实际的应用成为可能。

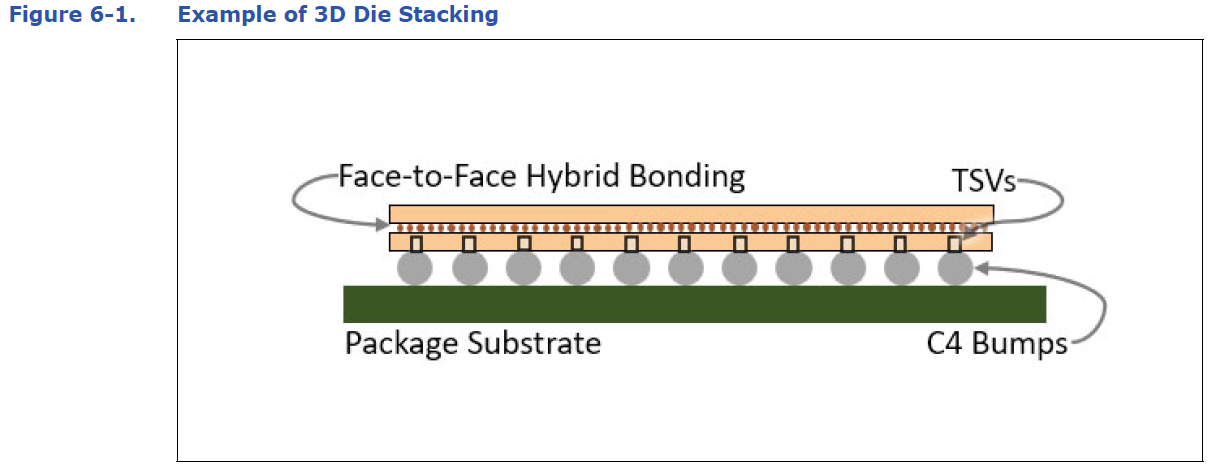

用于3D 封装的通用芯粒互连快速通道(UCIe-3D)被设计为一种普遍适用于3D Die-to-Die通信的接口。图6-1 展示了两个Die 以3D 配置堆叠的示例。UCIe-3D 使用二维的互连凸点阵列在Die 之间进行数据传输。

6.2 UCIe-3D Features and Summary

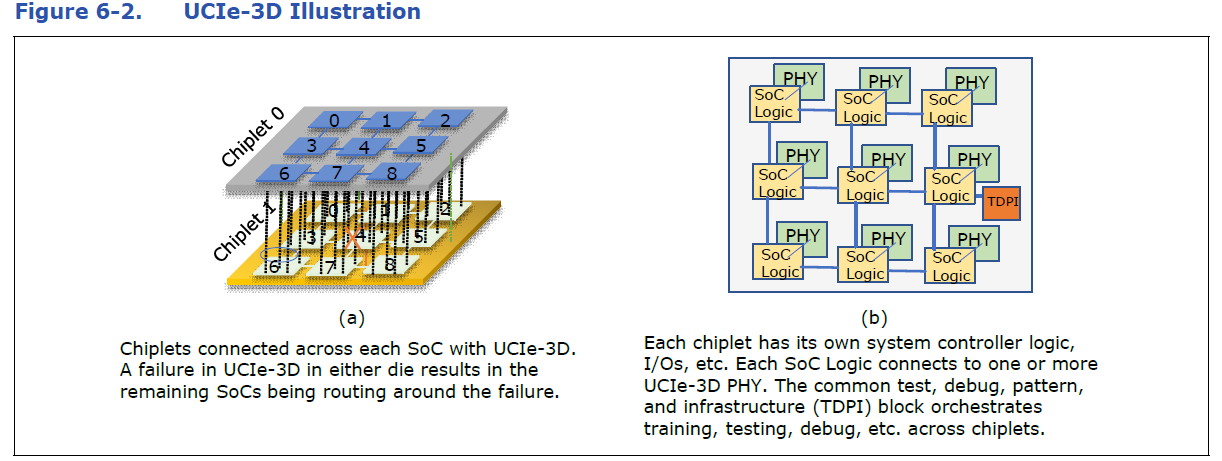

虽然UCIe 的2D 和2.5D 模型致力于实现无缝的即插即用互操作性,但由于封装技术的固有特性,UCIe-3D 模型需要一种更集成的方法。目的是提供一系列选项或“菜单”,用户可以从中选择最适合其需求的内容。UCIe-3D 的主要目标和一般方法如下:

电路和逻辑必须适配在凸点区域内(即,UCIe 将继续受凸点限制)。鉴于高密度,这 将转化为更低的工作频率和大大简化的电路(例如,在1 um 的凸点间距下,按逐通道 分摊的UCIe-3D 面积必须小于1 um2)。

无D2D 适配器。由于低频和几乎为零的通道距离,误码率低——无需CRC/重放。

一个固化的最小PHY,例如简单的反相器/驱动器。SoC 逻辑直接连接到PHY。

所有调试/可测试性钩子(hook)都位于一个公共块内(跨越所有UCIe-3D 链路),该公共块连接到芯粒内部的SoC 逻辑网络。

通道修复变为由SoC 逻辑协调的捆绑式宽修复。

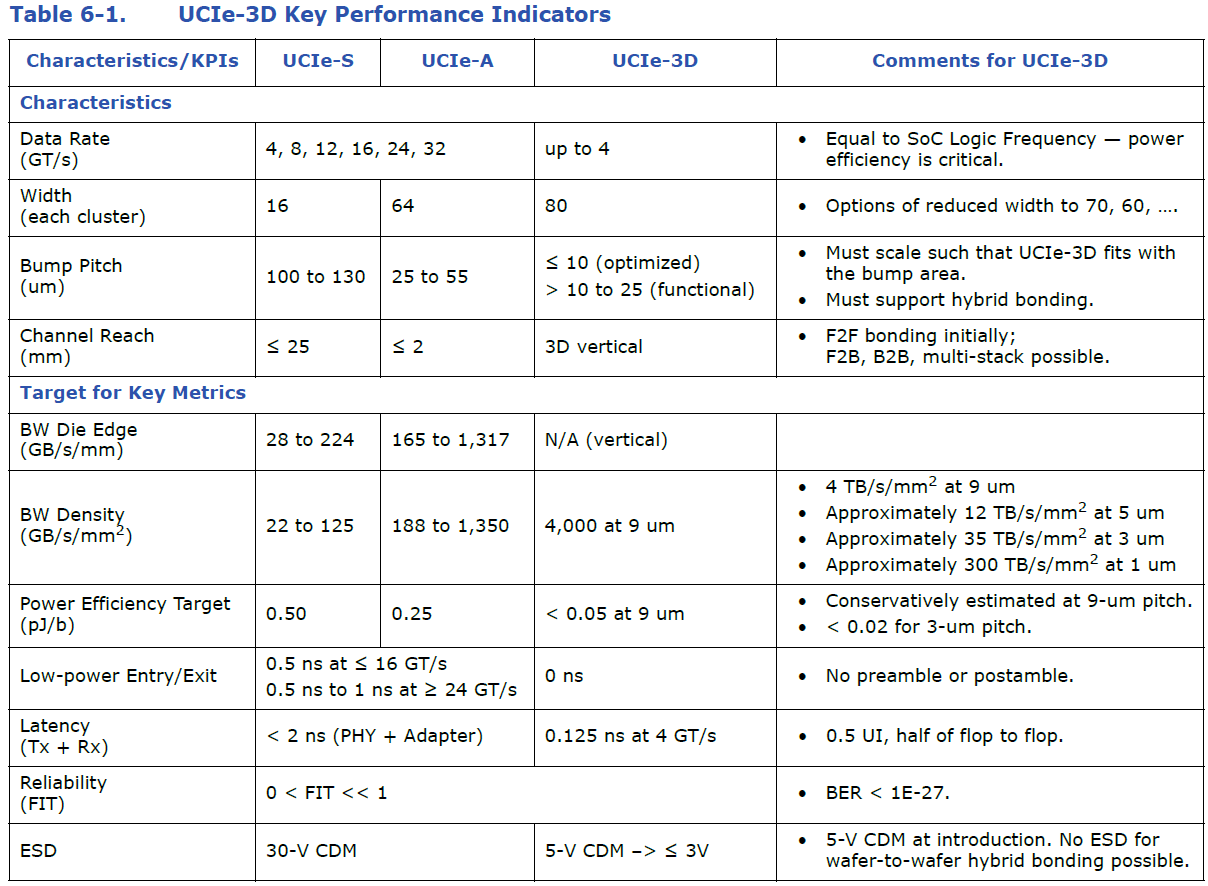

表6-1 总结了所提出的UCIe-3D 的关键性能指标。

6.3 UCIe-3D Tx, Rx, and Clocking

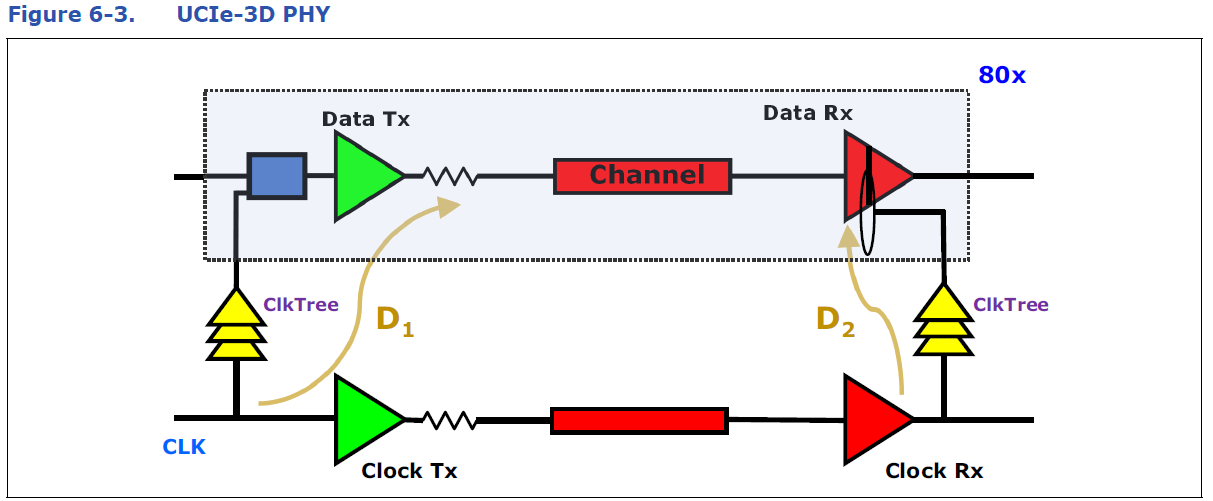

图6-3 展示了UCIe-3D 的收发器(Trx)架构。如图5-4、图5-8 和图5-13 所示的匹配架构提供了最佳的电源噪声抑制。然而,这是以增加功耗为代价的。图6-3 中所示的架构避免了这种功耗损失,同时保持了相同水平的电源噪声抑制。UCIe-3D 规范将为时钟分配延迟D1和D2 确定目标值和容差。

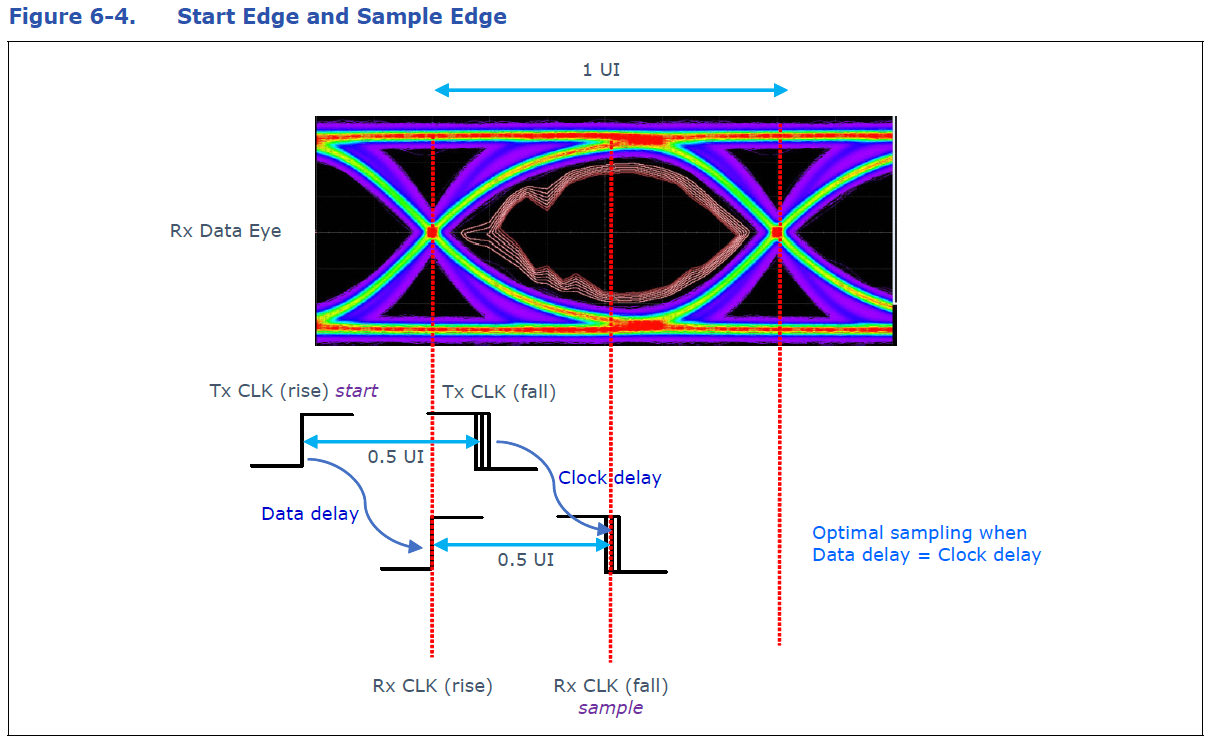

需要强调的是,UCIe-3D 采用上升到下降的时序方法,这与典型的片上逻辑设计中使用上升到上升的时序方法不同。这两种情况的主要区别在于,片上逻辑必须考虑组合逻辑引起的延迟,而UCIe-3D 具有匹配的数据和时钟缓冲延迟,导致接近零的差分。如图6-4 所示,上升到下降的时序为零延迟差分产生了最优的时序余量。

6.4 Electrical Specification

6.4.1 Timing Budget

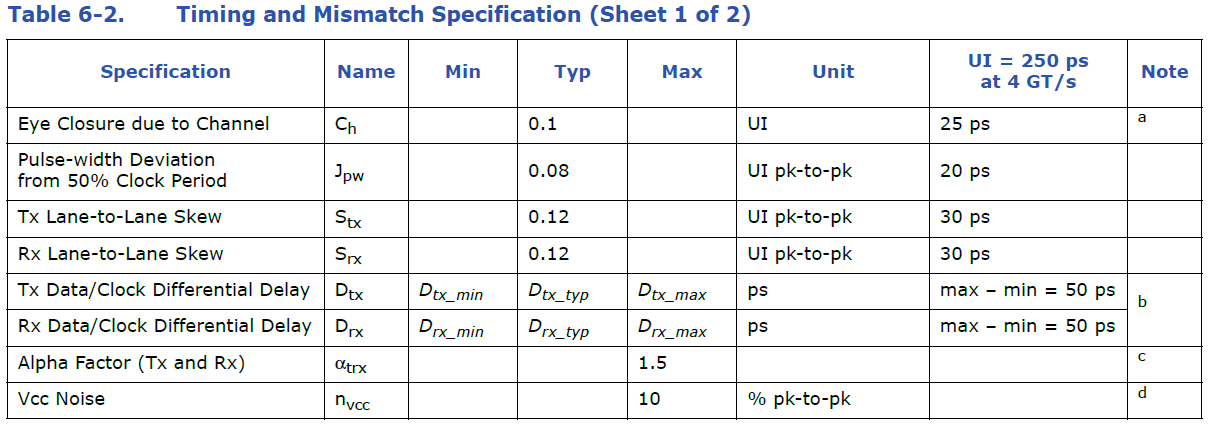

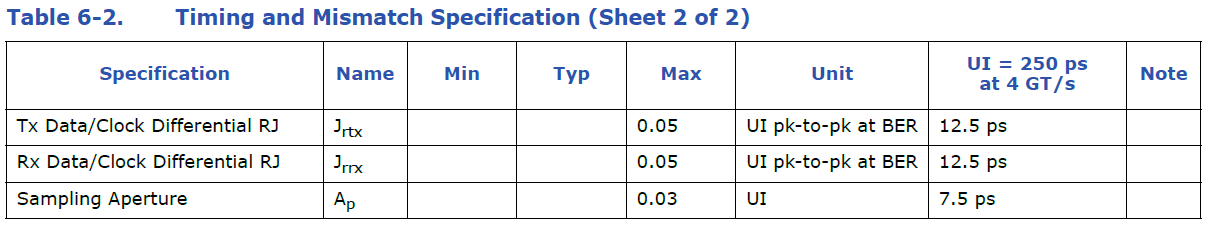

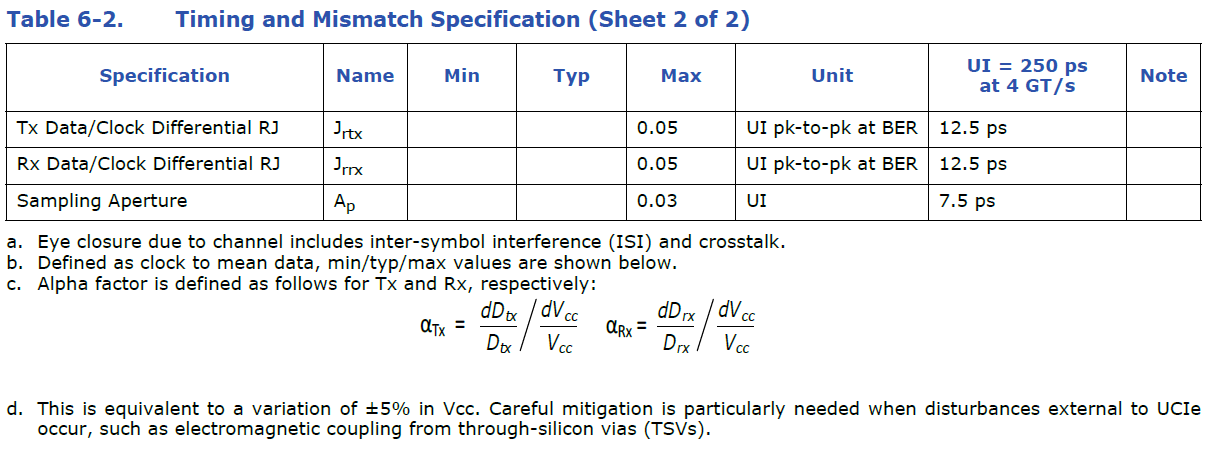

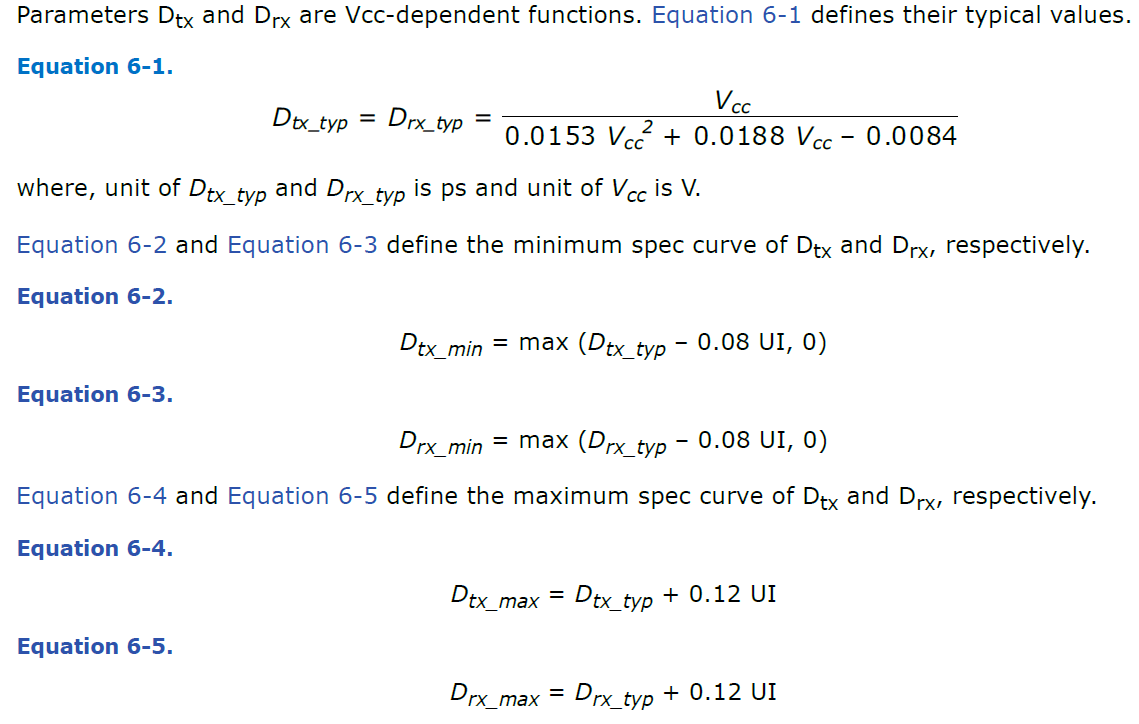

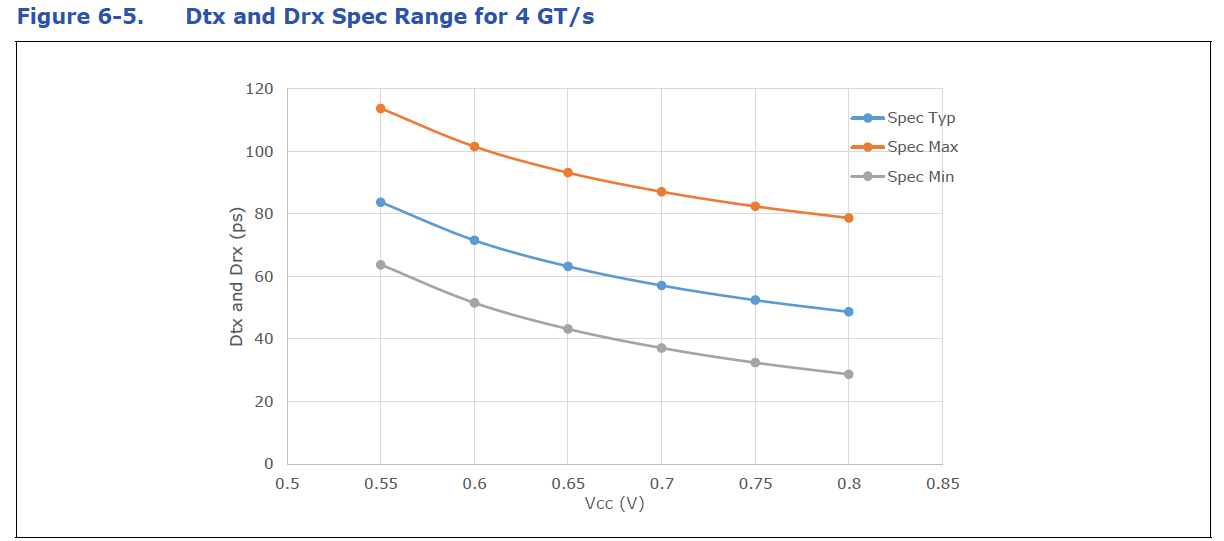

对于链路时序预算,考虑诸如抖动、噪声、失配和误差项等各种因素至关重要。表6-2 列出了与链路时序相关的UCIe-3D 规范参数。偏离50%时钟周期的脉冲宽度偏差包括静态误差(占空比误差)和动态误差(脉冲宽度抖动)。通道间偏斜考虑了数据通道之间的变化,数据/时钟差分延迟考虑了时钟到数据通道分布中心的延迟。

图6-5 展示了4 GT/s 的规格范围图。

从缓冲链的一般理论导出的延迟时间方程,在分母中包含与Vcc 成比例的项和Vcc 的二次依赖项。此方程适用于特定的工艺和设计。典型设计预计具有相同的趋势,并保持在上曲线和下曲线的边界内。不需要与中心曲线对齐。

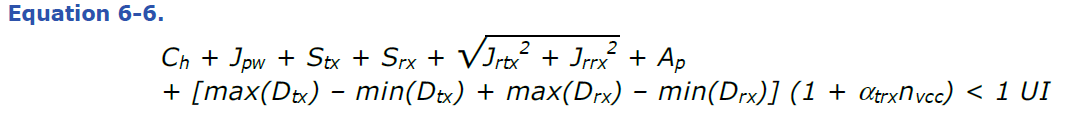

方程6-6 对于完成时序预算至关重要,随后得出定义的规格限制。方程6-6。

当Vcc 发生变化时,例如在动态电压频率缩放(dynamic voltage frequency scaling,DVFS)的情况下,Dtx 和Drx 的规格范围会相应地调整。这提供了一定程度的设计灵活性,因为延迟不需要在整个Vcc 范围内符合固定的频段。鉴于从最大值到最小值的范围保持不变,时序余量不受影响。

6.4.2 ESD and Energy Efficiency

数据和时钟信号应符合眼图上的掩码,其规定如下:

最小电压摆幅

输出电压稳定的最小持续时间

最大允许过冲和下冲

Tx 输出摆幅范围在0.40 V 至0.75 V 之间。

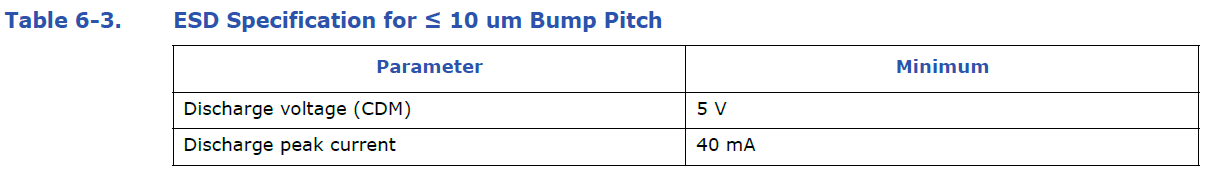

表6-3 定义了ESD 目标。

对于大于10 um 至小于25 um 的凸块间距,可以允许更高的ESD。

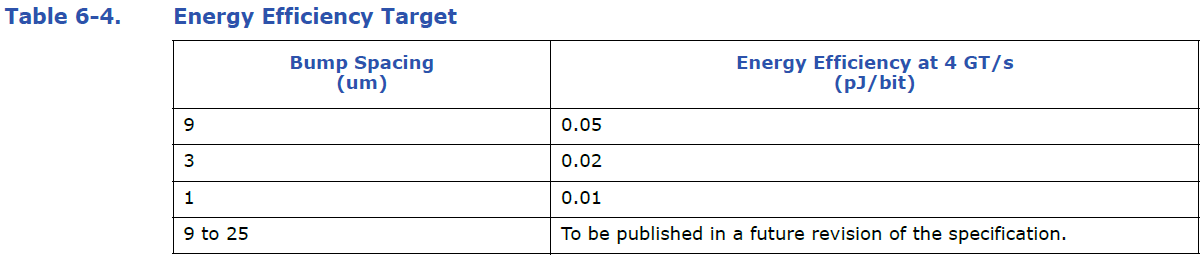

表6-4 列出了能源效率目标。

6.4.3 UCIe-3D Module and Bump Map

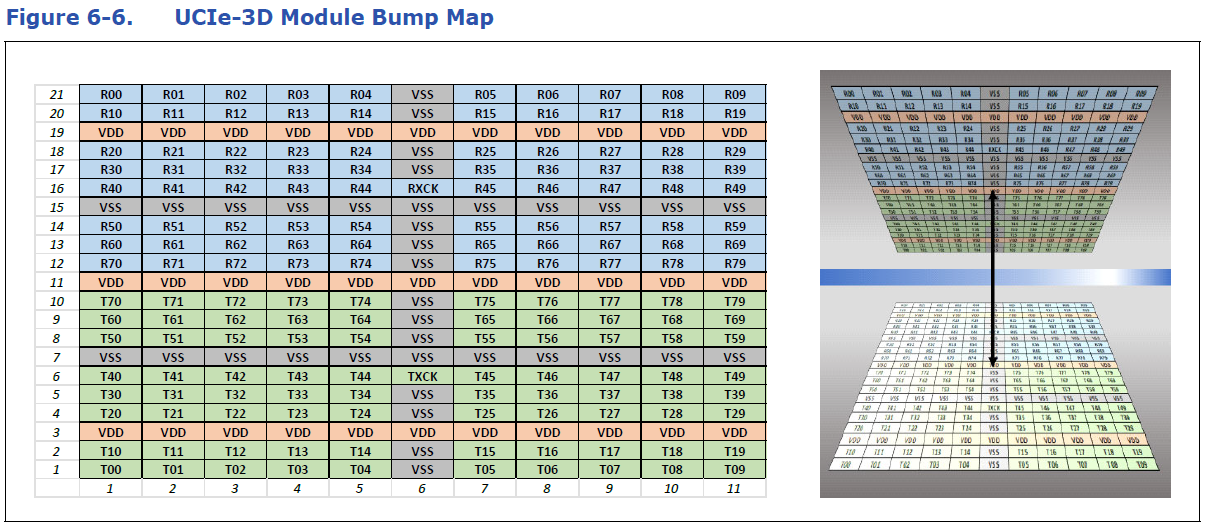

图6-6 描绘了UCIe-3D 的潜在凸块图。信号的排列方式使得顶部Die 和底部Die 可以使用相同的PHY。图6-6 中使用的单位是凸块间距。在9 um 间距下,x80 模块(包括Tx 和Rx)的估计面积约为0.02 mm2。需要注意的是,面积与凸块间距的平方成正比。

UCIe-3D 标准并未规定强制的凸块间距;然而,在引入时建议采用9 um 的间距。随着技术的进步,将确定其他特定的推荐间距值。

尽管UCIe-3D 本身并未预先定义适配器,但用户可以根据需要灵活地在模块内为适配器功能分配一些数据通道,例如Valid、Data Mask、Parity 和ECC。UCIe-3D 不需要初始化的边带。如果需要类似于边带的低带宽数据链路,则由实现来决定如何为此目的分配一组通道。

可以使用位复制或其他形式的冗余来保证链路的可靠性。

如果模块在物理上相邻,可以在它们之间添加额外的VDD,以提供物理隔离、屏蔽和额外的供电。

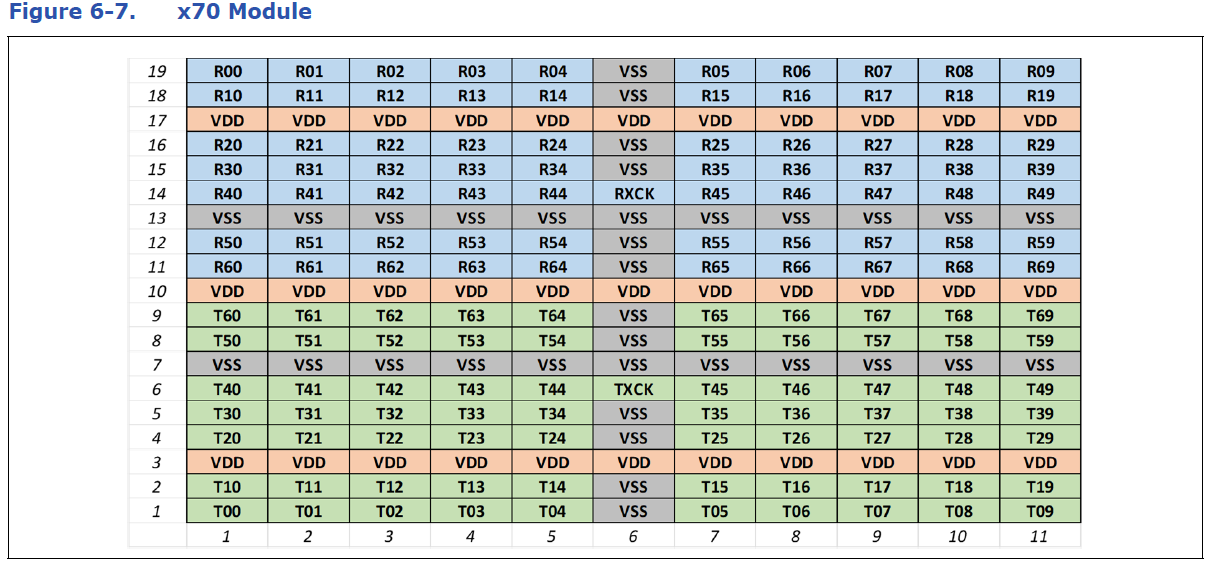

连同x80,x70 模块的凸块图如图6-7 所示。如果需要,其他模块宽度的凸块图可能会在本规范的未来更新中纳入,使用类似的布局。

6.4.4 Repair Strategy

缺陷大小(更确切地说,受单个缺陷影响的硅面积)由概率分布定义。其大小受诸如SoC中的I/O 数量、所使用的封装技术和凸块间距等因素的影响。一个标准需要涵盖来自多家公司的技术,可扩展到未来的凸块间距,以及不同的SoC 大小。基于固定缺陷大小的通道修复对于一个有效的标准来说是不实际的。

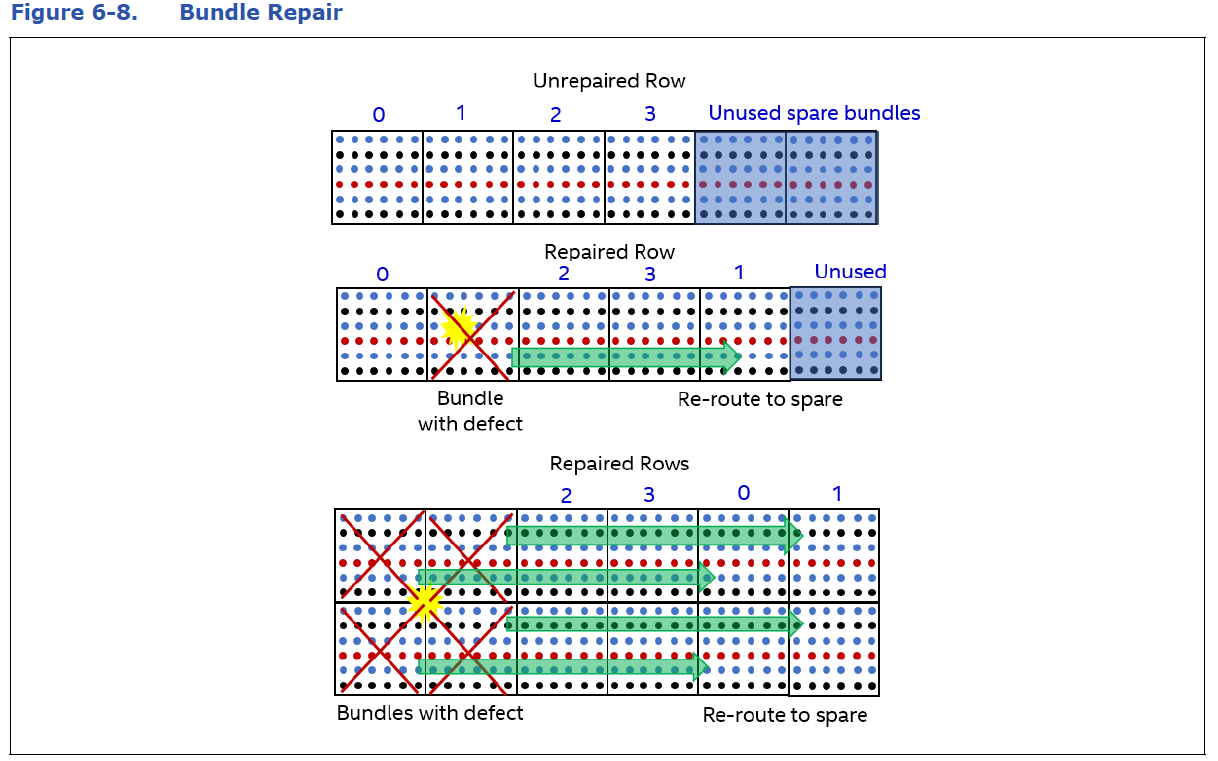

鉴于这些考虑因素,为UCIe-3D 提出了一种bundle 修复策略。这涉及在SoC 内预留束用于修复目的,在发生故障时可以重新布线作为备份,如图6-8 所示。该图显示了无修复、1-bundle修复和4-bundle 修复的情况。对于密集封装的2D UCIe 模块阵列,建议预留两个完整的模块(相当于四个bundle)来修复单个故障。这假定在至少一个方向上Tx 和Rx bundle 交替排列。每个模块配备一个Tx bundle(包括一个x80 Tx + Clock)和一个Rx bundle(包括一个x80 Rx + Clock)。

为了缩放大量UCIe 链路的一般情况,可以使用以下数学模型来计算修复要求:

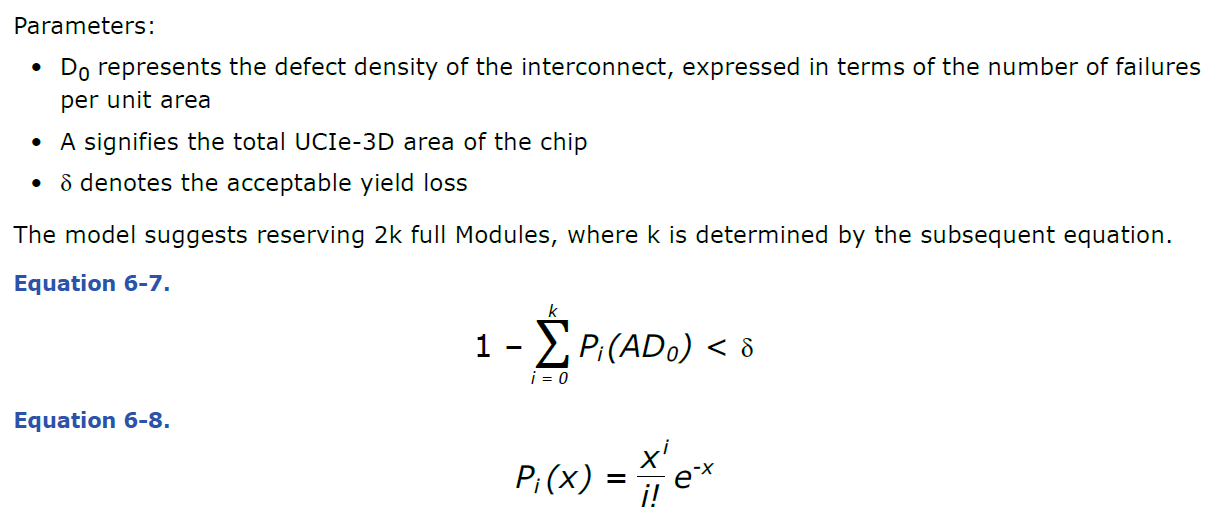

参数:

D0 表示互连的缺陷密度,以每单位面积的故障数量来表示

A 表示芯片的总UCIe-3D 面积

δ 表示可接受的成品率损失

该模型建议预留2k 个完整模块,其中k 由后续方程确定。方程6-7。

方程6-7 和方程6-8 中的计算假定与bundle 大小相当的大型互连缺陷相对较少。如果大缺陷的密度超过一定限度,使得方程6-9 不成立,则可能需要更多的备用bundle。

方程6-9。

其中,D1 是直径大于bundle 大小的缺陷的密度。确切的数量可以通过模拟确定。

当UCIe-3D 链路不是密集封装时,在bundle 之间战略性地放置间距可以有效地减少所需的修复bundle 的数量。例如,在行之间有足够的间距时,可以防止单个缺陷消除四个bundle的情况发生。然而,这种间距的精确确定高度依赖于所使用的特定技术,因此超出了本规范的范围。本规范仅将此作为一个潜在的选项加以强调。

预计修复的启动将源自于UCIe-3D PHY 之外的SoC 逻辑,因此在此不作详细阐述。其实现可以是特定于系统的。

6.4.5 Channel and Data Rate Extension

虽然UCIe-3D 目前的重点是Face-to-Face 混合键合,但所提出的架构设计为适用于Face-to-Back、Back-to-Back 和多堆叠配置。

需要进行全面的通道和电路模拟来确定这些场景的最佳数据速率。对于Face-to-Back 和Back-to-Back 配置,预计数据速率降低10%或更少。