BUCK电路的环路补偿

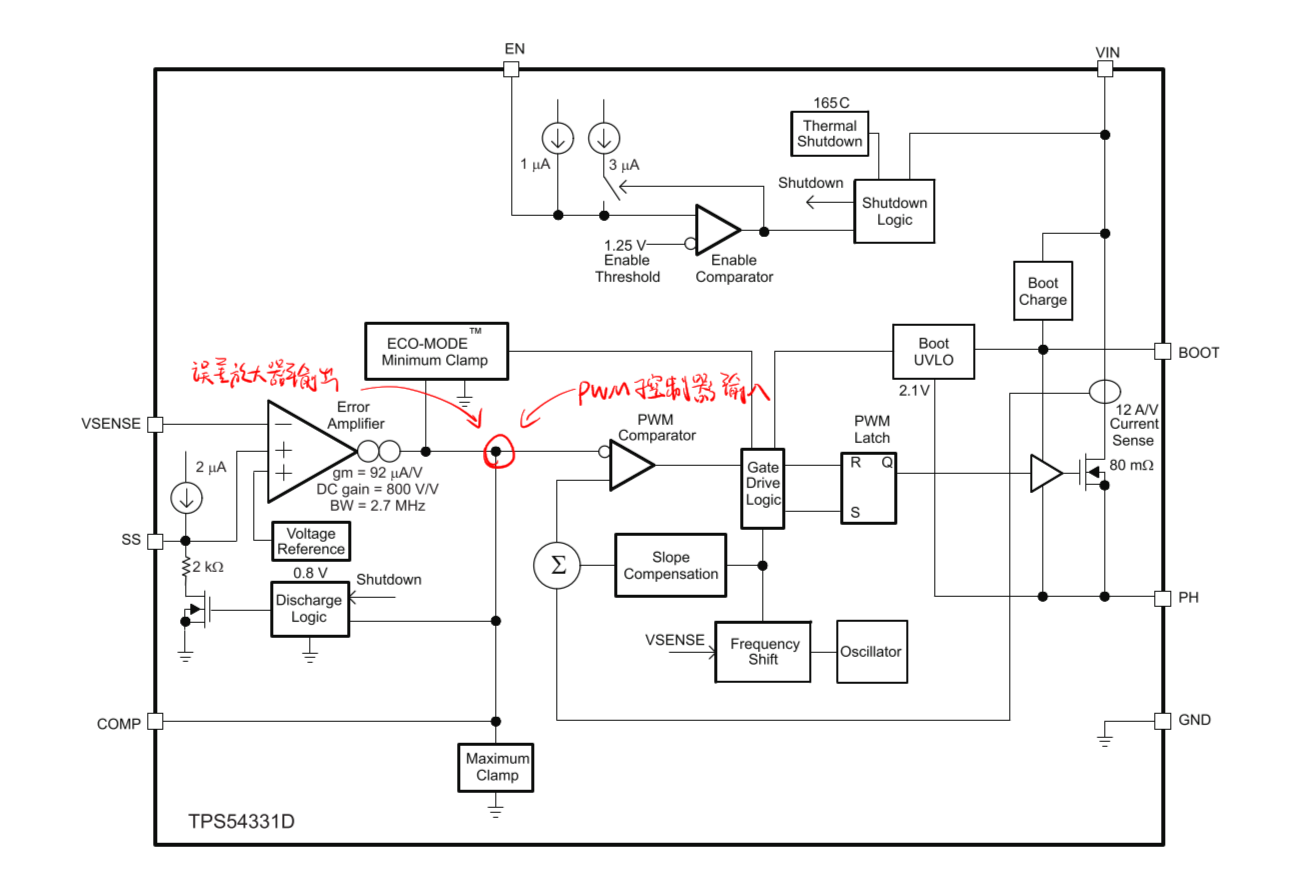

芯片的COMP脚是用来设计环路补偿用的,它给芯片内部的误差放大器的输出和PWM控制器输入做补偿,如果环路补偿设计得不好,会更容易引起环路的不稳定或振荡,也可能导致输出电压异常。环路补偿涉及三个指标:剪切频率,相位裕量,增益裕量。一般剪切频率要设计到1/10-1/50,相位裕度要>45°,增益裕量<-10dB。

在进行环路补偿的时候,我们先定一个剪切频率,比如我们的芯片是570KHZ的,我们就取剪切频率为25K,再设定相位裕度PM=60°,这样我们就可以计算得到缺失相位PL和相位补偿PB

这里是等效串联电阻,Co是输出电容。

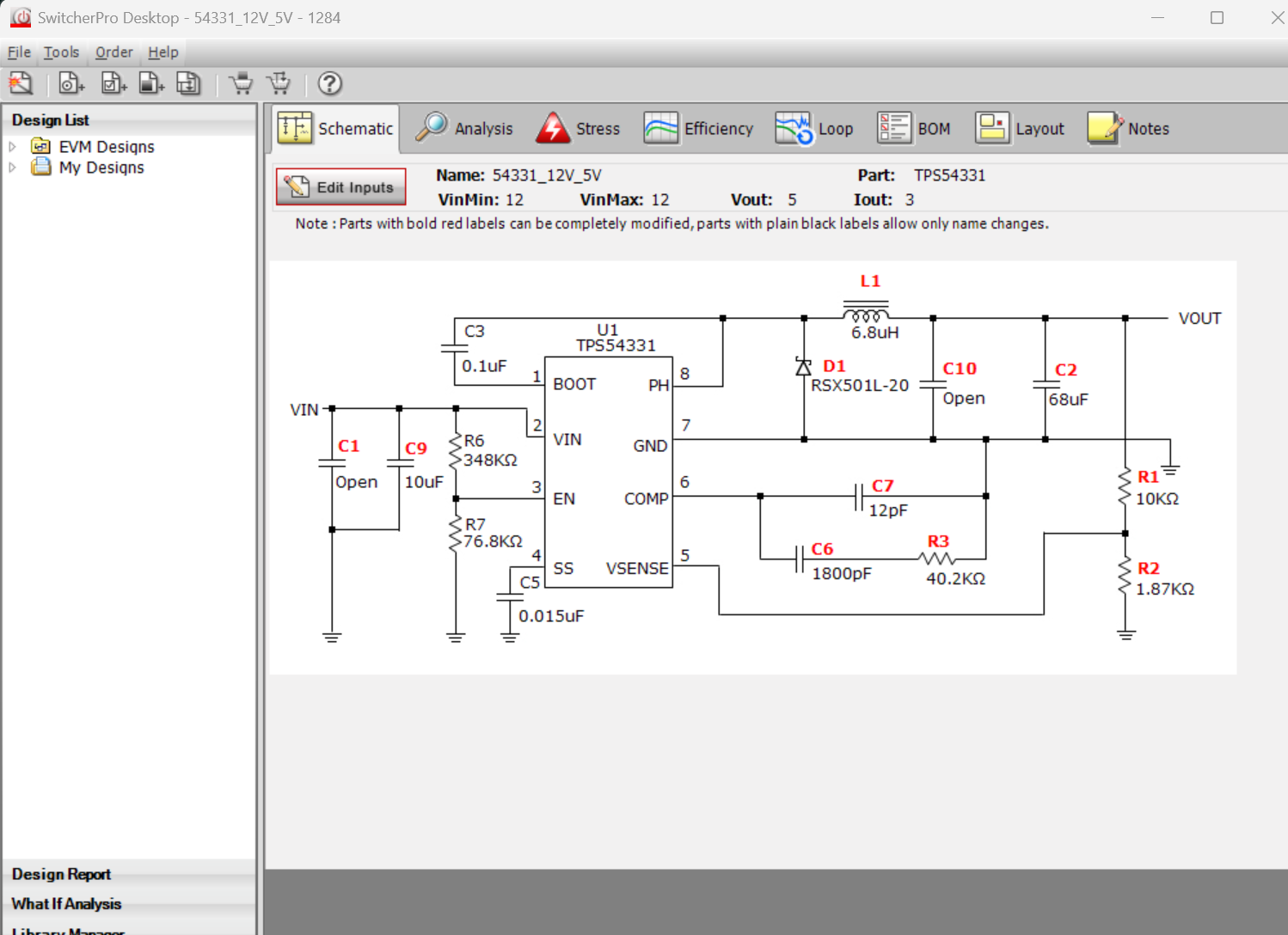

最终计算出来的Rz,Cz和Cp就是我们需要的环路补偿电路的阻容的取值。当然,每次都这样计算是比较麻烦的,所以我们可以使用TI提供的环路仿真工具。

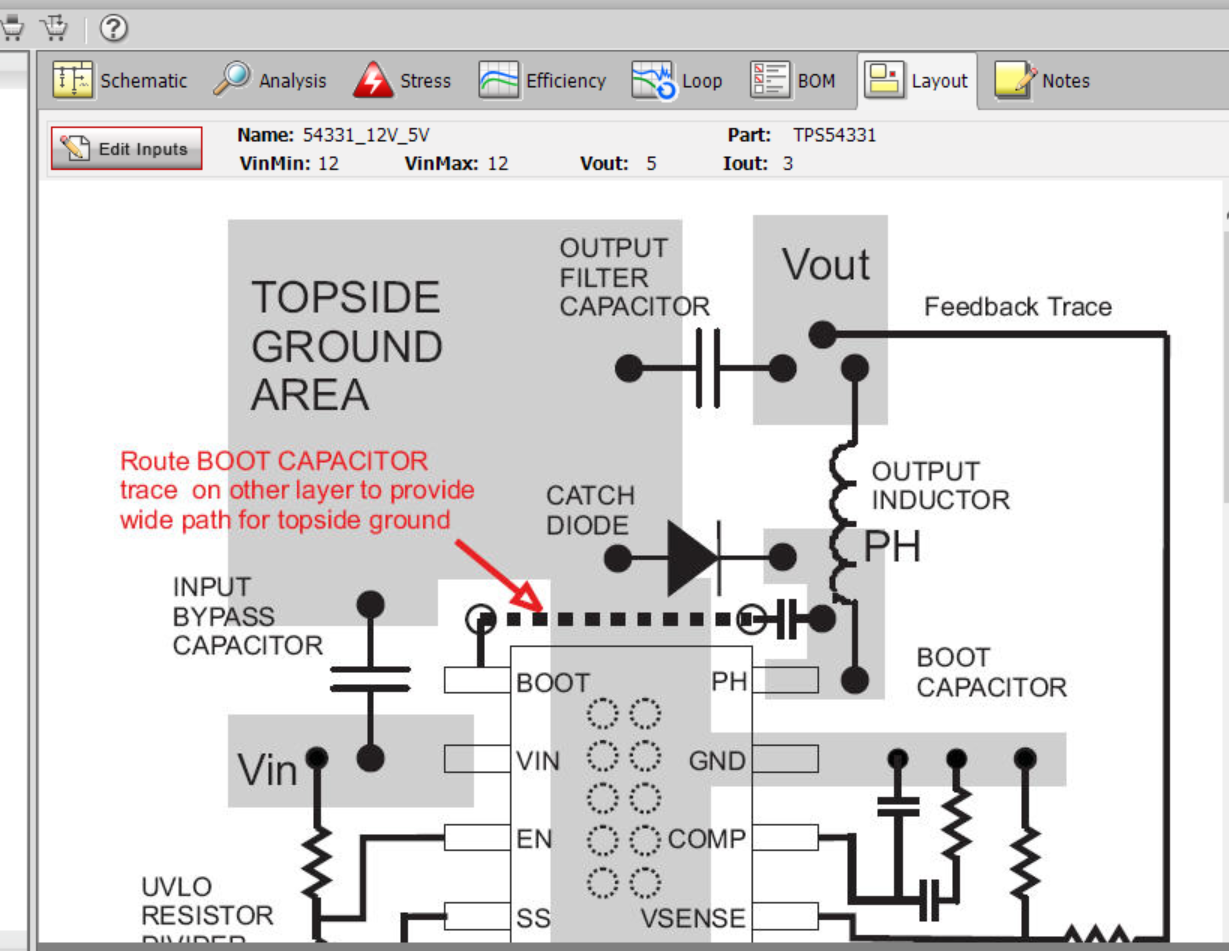

打开后选择所使用的芯片,再选择输入电压,输出电压,输出电流等参数,软件会自动计算环路补偿的器件参数,包括后面还有Layout的指导。

DCDC电路的PCB设计_dcdc pcb-CSDN博客