FPGA时序分析(四)

接上一篇文章:FPGA 时序分析(三)-CSDN博客

7、输出延迟约束

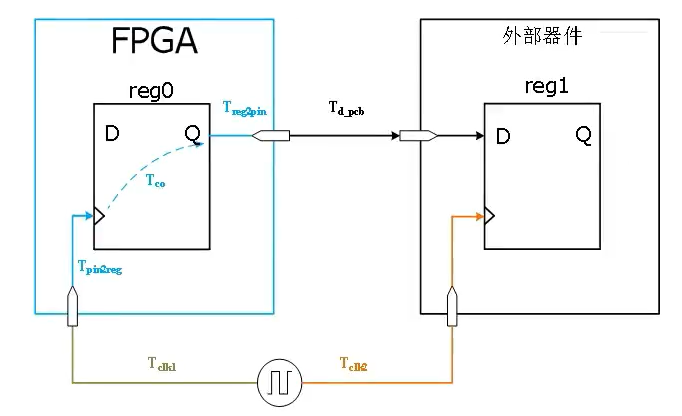

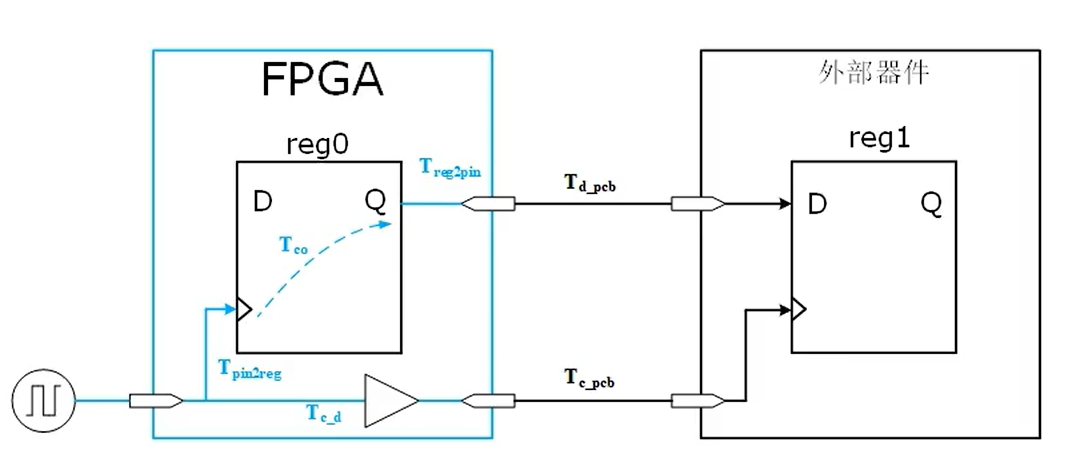

输出延迟约束,其路径模型为寄存器到FPGA引脚的路径。输出延迟约束,定义为:FPGA引脚上数据和时钟信号的相位关系。输出延迟约束指示了时钟锁存边沿对于数据的延时,表示外部器件在这样一个延迟范围内能够采集到FPGA发送的数据。

本章内容可以参考文章 :FPGA时序分析(二)。

7.1 系统同步时钟下的单边沿采样

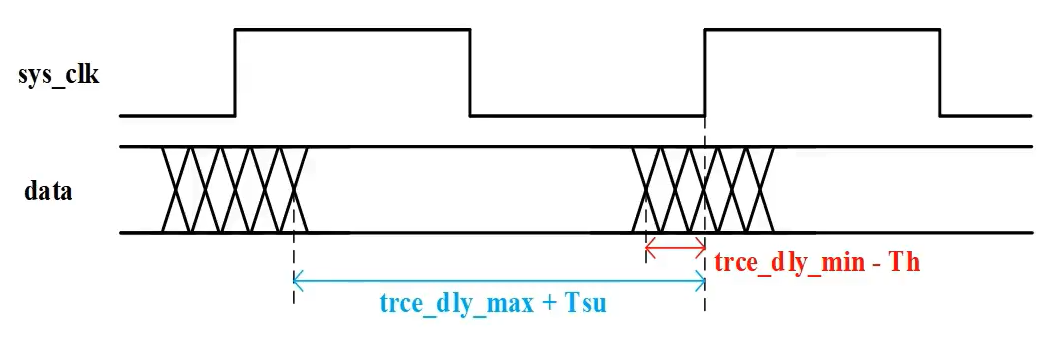

对于系统同步时钟接口的上升沿采样,系统时钟的相同有效边沿作用于FPGA和外部器件,数据和时钟的对应关系如下图所示(此图中,数据和时钟未满足时序收敛,需要进行相应的最大输出延时和最小输出延时后,才能满足时序收敛)。

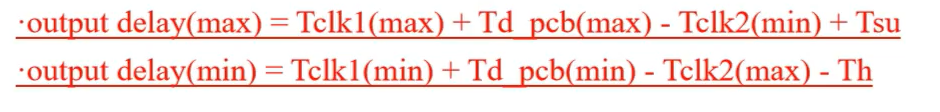

标准情况下,计算output_delay的公式如下:

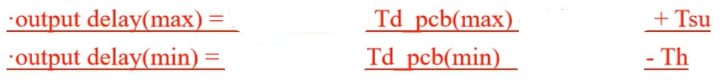

由于clk1和clk2的时钟延迟相差不大,因此我们暂时认为其数值为0,即得到如下的公式:

这样就可以近似得到trce_dly_max=Td_pcb(max),trce_dly_min=Td_pcb(min)。

因此最大延时记为max_dly = trce_dly_max + Tsu;(Tsu为外部器件的建立时间,此时满足外部器件的简历时间)

因此最小延时记为min_dly = trce_dly_in - Th;(Th为外部器件的保持时间,此时满足外部器件的保持时间)

vivado中的约束指令编写如下:

set_output_delay -clock <sys_clk> -max max_dly [get_ports data] -clock_rise

set_output_delay -clock <sys_clk> -min min_dly [get_ports data] -clock_rise#若为下降沿采样,仅需要更改clock_rise为clock_fall即可

set_output_delay -clock <sys_clk> -max max_dly [get_ports data] -clock_fall

set_output_delay -clock <sys_clk> -min min_dly [get_ports data] -clock_fall

增加外上述约束后,vivado会自动调整FPGA内部的走线,使输出到外部器件的时钟和数据,满足外部器件本身的建立时间和保持时间。

7.2 源时钟同步单边沿采样

对于源同步接口采样,输出延迟的计算可以通过两种方式进行参考,一是基于目标器件的建立时间和保持时间要求,二是基于时钟和数据的偏斜。

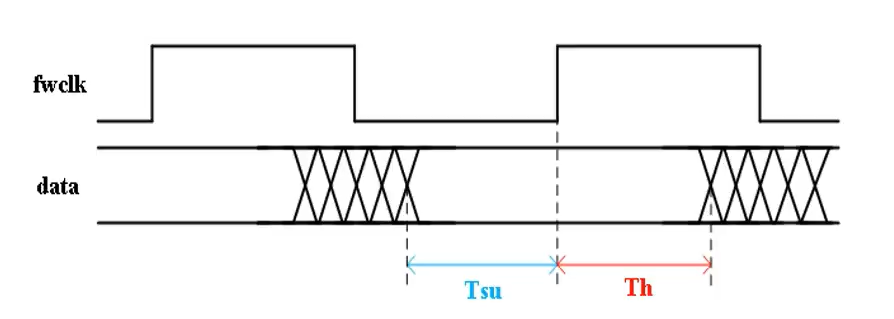

情况一: 基于目标器件的建立时间和保持时间要求

计算输出延迟的示意图如下:

因此最大延时记为max_dly = trce_dly_max + Tsu;(Tsu为外部器件的建立时间,此时满足外部器件的简历时间)(此处的trce_dly_max指的是PCB走线的延时,基本可忽略)

因此最小延时记为min_dly = trce_dly_in - Th;(Th为外部器件的保持时间,此时满足外部器件的保持时间)(此处的trce_dly_min指的是PCB走线的延时,基本可忽略)

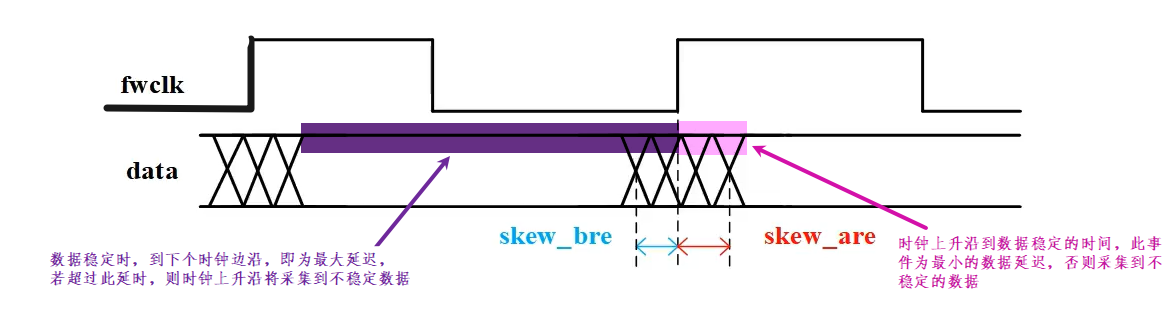

情况二: 基于时钟和数据的偏斜

计算输出延迟的示意图如下:

因此最大延时记为max_dly = cycle - skew_are;(cycle指的是时钟周期,skew_are指的是skew after rise edge,若数据延迟大于此数值,则可能导致时钟上升沿无法采集到此数据)

因此最小延时记为min_dly = skew_bre;(skew_bre指的是skew before rise edge,若数据延迟小于此数值,则可能导致时钟上升沿无法采集到此数据)

vivado中的约束指令编写如下:

set_output_delay -clock <fwclk> -max max_dly [get_ports data] -clock_rise

set_output_delay -clock <fwclk> -min min_dly [get_ports data] -clock_rise#若为下降沿采样,仅需要更改clock_rise为clock_fall即可

set_output_delay -clock <fwclk> -max max_dly [get_ports data] -clock_fall

set_output_delay -clock <fwclk> -min min_dly [get_ports data] -clock_fall

7.3 源同步时钟双边沿采样

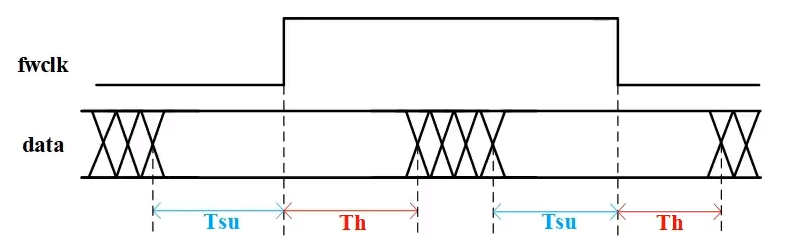

情况一:基于外部器件的建立时间要求和保持时间要求计算输出延迟

其示意图如下所示:

上升沿的最大延时记为 rise_max_dly = trce_dly_max + Tsu_r;(Tsu_r:外部器件的上升沿建立时间)

上升沿的最小延时记为 rise_min_dly = trce_dly_min - Th_r;(Th_r:外部器件的上升沿保持时间)

下降沿的最大延时记为 fall_max_dly = trce_dly_max + Tsu_f;(Tsu_f:外部器件的下降沿建立时间)

下降沿的最大延时记为 fall_max_dly = trce_dly_min - Th_f;(Th_f:外部器件的下降沿保持时间)

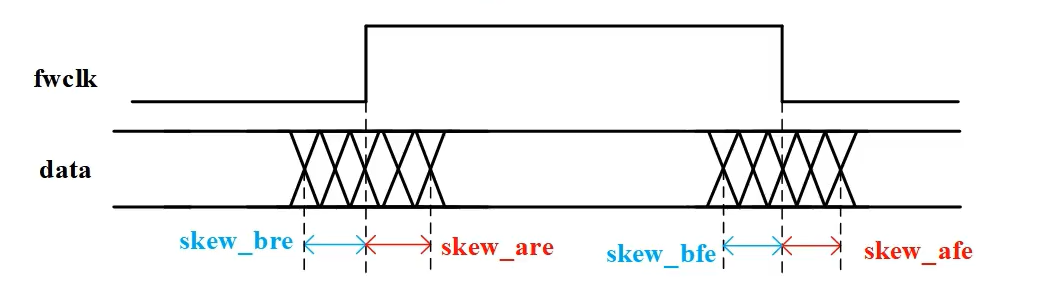

情况二:基于时钟和数据的偏斜计算输出延迟

上升沿最大延时记为rise_max_dly = cycle/2 - skew_afe;(skew after fall edge)

上升沿最小延时记为rise_min_dly = skew_bre;(skew before rise edge)

下降沿最大延时记为fall_max_dly = cycle/2 - skew_are;(skew after rise edge)

下降沿最小延时记为fall_max_dly = skew_bfe; (skew before fall edge)

输出延迟的约束命令如下:

set_output_delay -clock <fwclk> -max rise_max_dly [get_ports data] -clock_rise

set_output_delay -clock <fwclk> -min rise_min_dly [get_ports data] -clock_rise

#增加-add_delay方式覆盖上面的上升沿约束

set_output_delay -clock <fwclk> -max fall_max_dly [get_ports data] -clock_fall -add_delay

set_output_delay -clock <fwclk> -min fall_min_dly [get_ports data] -clock_fall -add_delay