DDR3入门系列(一)——初识DDR3

1. DDR是什么

DDR的全称是 Double Data Rate Synchronous Dynamic Random-Access Memory,中文译为 双倍数据速率同步动态随机存取存储器。DDR SDRAM 自诞生以来(约 2000 年),凭借其显著的性能优势,已经完全取代了 SDR SDRAM,并成为过去二十多年个人电脑、服务器、工作站、笔记本电脑乃至许多其他电子设备(如游戏机、显卡)中使用的主导性内存技术。

DDR 技术本身也在不断迭代更新,每一代都带来更高的速度、更大的容量和更低的电压/功耗:

DDR (DDR1): 第一代 DDR 内存。奠定了双倍速率的基础。

DDR2: 进一步提高了时钟频率和带宽,降低了工作电压(1.8V),改进了封装和信号完整性。引入了 Prefetch 技术(通常是 4-bit)。

DDR3: 再次大幅提升频率和带宽,电压进一步降低到 1.5V(后期有 1.35V 低电压版 DDR3L)。Prefetch 增加到 8-bit。成为长期的主流标准。

DDR4: 频率、带宽和容量(单条可达 32GB+)再次飞跃,工作电压降至 1.2V(也有 DDR4L)。改进了内部架构和可靠性。引入了 Bank Group 设计提升效率。

DDR5: 当前最新一代主流标准。

核心电压进一步降至 1.1V。

带宽再次翻倍(甚至更高): 通过将每个内存模块(DIMM)的通道拆分成两个独立的 32-bit 子通道(相当于每个 DIMM 有 2 个 32-bit 通道),并显著提升基础频率。

容量巨大提升: 单条容量可达 128GB 甚至更高。

集成电源管理芯片: 将原本主板上的电压调节模块移到内存条本身,提高稳定性和供电效率。

更强的纠错能力: 支持片内 ECC(并非所有消费级条都有,但架构支持)。

更高的密度和能效比。

GDDR (Graphics DDR): 专为显卡设计的 DDR 内存变种,更侧重于极高的带宽(通过更宽的接口和更高频率实现),延迟相对较高。也有 GDDR5, GDDR6, GDDR6X, GDDR7 等迭代。

2. DDR的引脚定义(以DDR3L为例)

DDR引脚按功能可分为电源和地线、时钟信号、命令和地址总线、数据总线、系统管理总线及其他控制信号。

电源和地线:

VDD / VDDQ (Power Supply): 这是核心逻辑和输出缓冲区的供电引脚。对于 DDR3L,标准电压是 1.35V,但通常设计为兼容 1.5V (标准 DDR3 电压)。模块上会有多个 VDD/VDDQ 引脚分布以提供稳定的电流和降低噪声。

VSS / VSSQ (Ground): 对应的地线引脚。同样有多个分布,提供电流回路并降低噪声。VSSQ 是输出缓冲区专用的地。

VREFCA (Reference Voltage for CA bus): 提供给 命令/地址总线 接收器的参考电压。这个电压非常重要,通常设定为 VDDQ 的一半 (对于 1.35V VDDQ,VREFCA ≈ 0.675V;对于 1.5V VDDQ,VREFCA ≈ 0.75V)。接收器用它来判断 CA 总线上的信号是逻辑高还是低。

VREFDQ (Reference Voltage for DQ bus): 提供给 数据总线 接收器的参考电压。其设定方式与 VREFCA 相同 (VDDQ/2)。在 DDR3/DDR3L 中,VREFDQ 通常由内存控制器提供,并且可以是可编程的。

SPD_VCC / SPD_VSS: 提供给串行存在检测 EEPROM 的电源和地。

时钟信号:

CK / CK# (Differential Clock Inputs): 最重要的同步信号。这是一对差分时钟信号 (CK 是正相,CK# 是反相)。所有命令和地址的输入,以及数据的输入/输出,都以这对时钟的交叉点为参考点进行采样。 时钟频率决定了内存的运行速度 (如 DDR3L-1600 的核心时钟频率是 800MHz,但由于是 DDR,数据传输率是 1600 MT/s)。

CKE (Clock Enable): 时钟使能信号。当 CKE 为低时,DRAM 进入低功耗状态(如自刷新)。高电平时,时钟正常工作。

命令和地址总线:

CS# (Chip Select): 片选信号(低电平有效)。当 CS# 为低时,该 DRAM 模块才会响应命令总线上的命令。

RAS# / CAS# / WE# (Command Pins): 行地址选通、列地址选通、写使能(均为低电平有效)。这三个信号与 CS# 一起组合,在时钟的有效边沿 定义具体的操作命令(如激活 ACT,读 READ,写 WRITE,预充电 PRE,刷新 REF 等)。内存控制器通过改变这些信号的状态来发出指令。

A0-A16 (Address Inputs): 地址输入引脚。用于传输 行地址 (Row Address) 和 **列地址 (Column Address)**。具体传输的是行还是列地址,由当前发出的命令决定(如 ACT 命令后面跟的是行地址,READ/WRITE 命令后面跟的是列地址)。A10 在特定命令(如 PRE)中有特殊用途(如控制预充电是单 Bank 还是所有 Bank)。A12 在 DDR3 中用于 Bank 地址(BA0-BA2)的扩展或特定功能(如设置 BC4 或 BL8 突发长度)。

BA0-BA2 (Bank Address Inputs): Bank 地址输入。DDR3/DDR3L 芯片内部被划分为多个独立的存储体(Bank)。BA0-BA2 用于选择当前操作针对哪个 Bank(通常 8 个 Bank,需要 3 位地址)。地址命令会同时指定 Bank 和行/列地址。

ODT (On-Die Termination): 片内终端电阻使能。用于控制数据总线上的终端电阻是否启用。当写操作时,目标 DRAM 芯片的 ODT 会被使能,以匹配传输线阻抗,减少信号反射,提高信号完整性。读操作时,通常由内存控制器端的终端电阻工作。

数据总线:

DQ0-DQ63 (Data Input/Output): 64 位双向数据总线。这是实际读写数据通过的通道。每个引脚对应数据的一位。在读写操作期间传输数据。

DM / DBI (Data Mask / Data Bus Inversion):

DM (Data Mask): (通常标记为 DM0-DM7 或 DM0-DM9,取决于模块 ECC 与否) 写操作的字节掩码(低电平有效)。在写操作时,如果某个 DM 信号为低,则对应的字节(8 位 DQ)数据会被屏蔽,不会被写入 DRAM。用于部分写入。

DBI (Data Bus Inversion): (在部分 DDR3/DDR3L 模块中使用,特别是 LPDDR3,但在标准 DDR3L DIMM 中不普遍) 数据总线翻转。用于指示当前传输的数据是否被翻转,目的是减少同时切换的输出数量,从而降低功耗和噪声。

DQS / DQS# (Data Strobe): 数据选通信号(差分对)。这是数据采样的关键同步信号。

每个数据字节组(通常是 8 位 DQ)对应一对 DQS/DQS#。

读操作时:由 DRAM 发出。数据总线 DQ 上的数据在 DQS/DQS# 的交叉点(上升沿和下降沿)被内存控制器采样。DDR 特性体现在上升沿和下降沿都采样数据。

写操作时:由内存控制器发出。数据总线 DQ 上的数据需要在 DQS/DQS# 的交叉点(上升沿和下降沿)被 DRAM 采样。内存控制器需要精确控制 DQS 与 DQ 之间的时序关系(写均衡)。

TDQS / TDQS# (Termination Data Strobe): (在 x8 配置下替代 DM 功能) 主要用于在 x8 组织的 DRAM 中提供可选的终端电阻功能。在标准 DIMM 模块中较少直接关注。

系统管理总线:

SDA / SCL (Serial Data / Serial Clock): I²C 串行总线信号。连接到 DIMM 上的 SPD (Serial Presence Detect) EEPROM 芯片。主板 BIOS/UEFI 通过这个总线读取 SPD EEPROM 中存储的关于该内存模块的关键信息(如容量、速度、时序参数、制造商、电压要求等),以便自动配置内存控制器。

其他控制信号:

RESET# (Reset): 复位信号(低电平有效)。强制 DRAM 进入已知的初始化状态。

PAR (Command/Address Parity): (可选) 命令/地址总线奇偶校验位。用于检测命令/地址传输过程中的错误。

3. DDR的组成架构

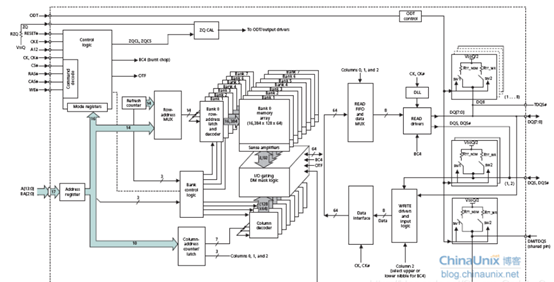

如图所示是存储器的顶层架构形式,这里以DDR3的架构为例,我们主要通过其中的Bank、Row和Column来说明其工作原理。

Bank (BK)

基础单元:每个 Bank 是独立的存储矩阵(由电容+晶体管组成的 DRAM 单元阵列)。

独立性:不同 Bank 可并行操作(如 Bank0 读数据时,Bank1 可预充电)。

数量:DDR4 通常 4 Bank/Group × 4 Group = 16 Banks;DDR5 可达 8 Bank/Group × 8 Group = 64 Banks。

Row (行)

物理结构:一行是存储矩阵中的 水平单元序列(所有 Column 的集合)。

激活操作:访问数据前需先激活(Activate)整行,将其内容读入 Bank 的 行缓冲器(Row Buffer)。

Column (列)

最小访问单元:一列是行中的 单个存储单元(实际访问以 Burst Length 为单位,如 BL=8 即连续 8 个列)。

访问方式:通过 列地址选通(CAS) 从行缓冲器读取/写入数据。

DDR的工作原理分为以下几个步骤(以读为例):

步骤1:选择目标地址。 内存控制器发送地址信号:Bank地址|Row地址|Column地址。

步骤2:激活行。 先根据Bank地址选中目标Bank,然后根据Row地址选中目标行,目标行的数据被读取到该Bank的行缓冲器。耗时tRCD,约10-20ns。

步骤3:读取列。 发送READ命令和Column地址,从行缓冲器中定位目标列。数据通过DQ总线以双倍速率(时钟上升/下降沿)输出。

步骤4:预充电,发送PRE命令。 将行缓冲器数据写回原行(刷新电容电荷),最后关闭当前行,为访问新行做准备。耗时tRP,约10-20ns。

关键时序约束 tRC(ROW Cycle Time) = tRAS(行激活时间) + tRP。需要注意防止Bank冲突,即同一Bank未预充电时访问新行会触发等待(严重降低性能)。

4. DDR内存大小的计算公式

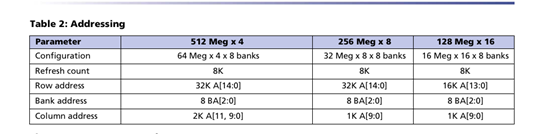

以一种DDR型号的芯片手册中的说明为例,计算DDR的内存大小,以256Meg x8这片DDR3为例,它的行地址位宽为[14:0],列地址位宽为[9:0],Bank位宽为[2:0],数据位8位,那么此片DDR3内存大小:2¹⁵ × 2¹⁰ × 2³ × 8 = 2Gb = 256MB

其中每个Bank的内存大小为: 2¹⁵ × 2¹⁰ × 8 = 0.25Gb = 32MB

本期分享结束,感谢大家看完,私信我可获取相关资料