高速缓冲存储器cache

目录

概述

读写流程

地址映射

直接映射

全相连映射

组相连映射

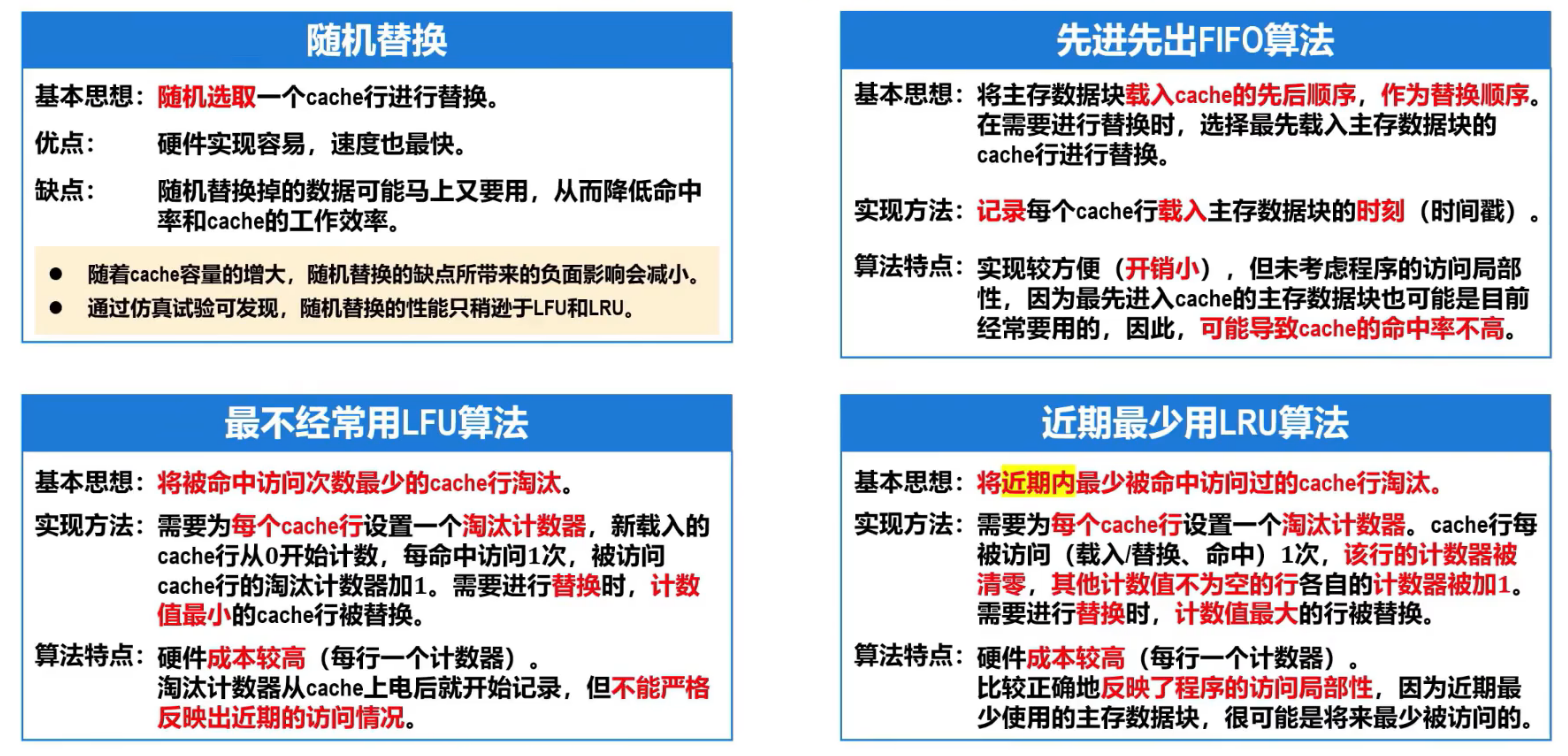

替换算法

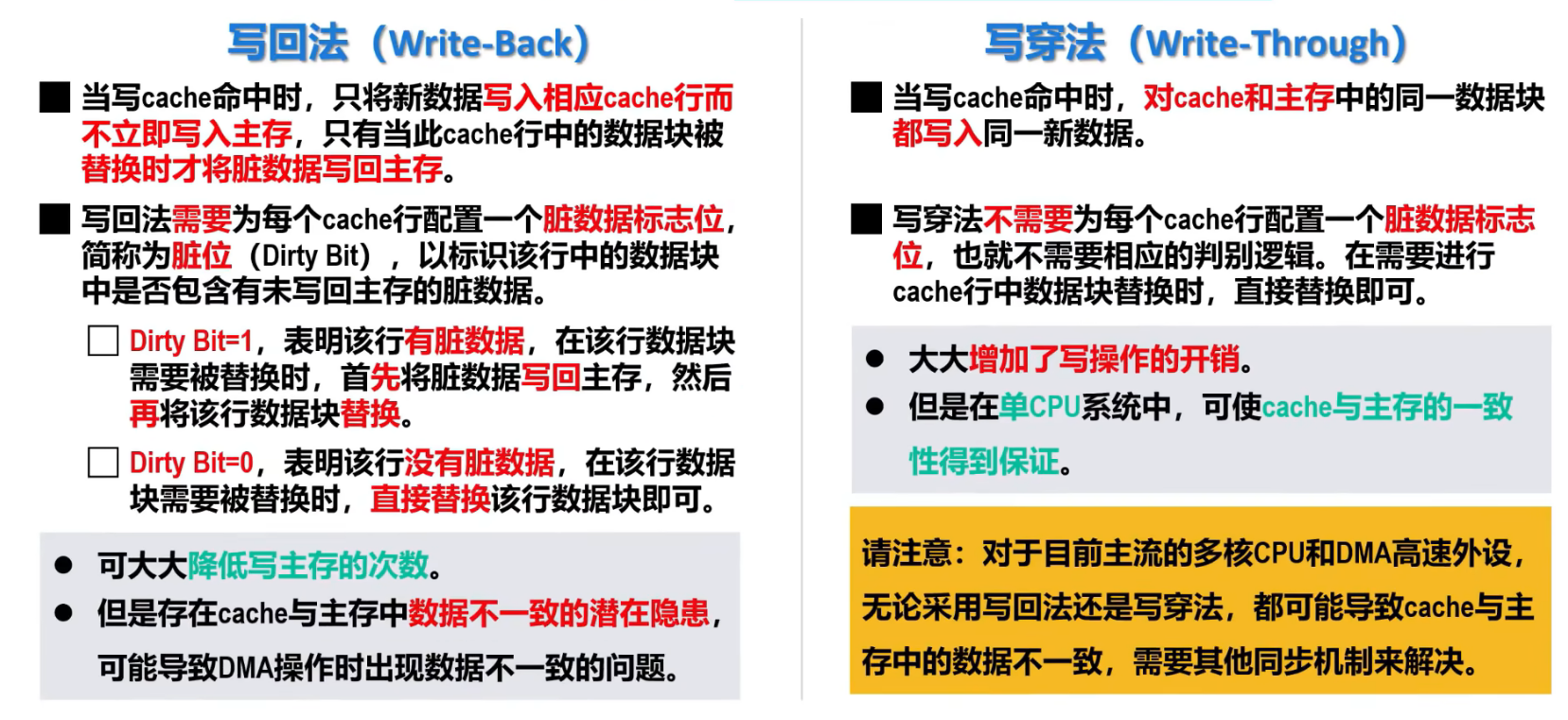

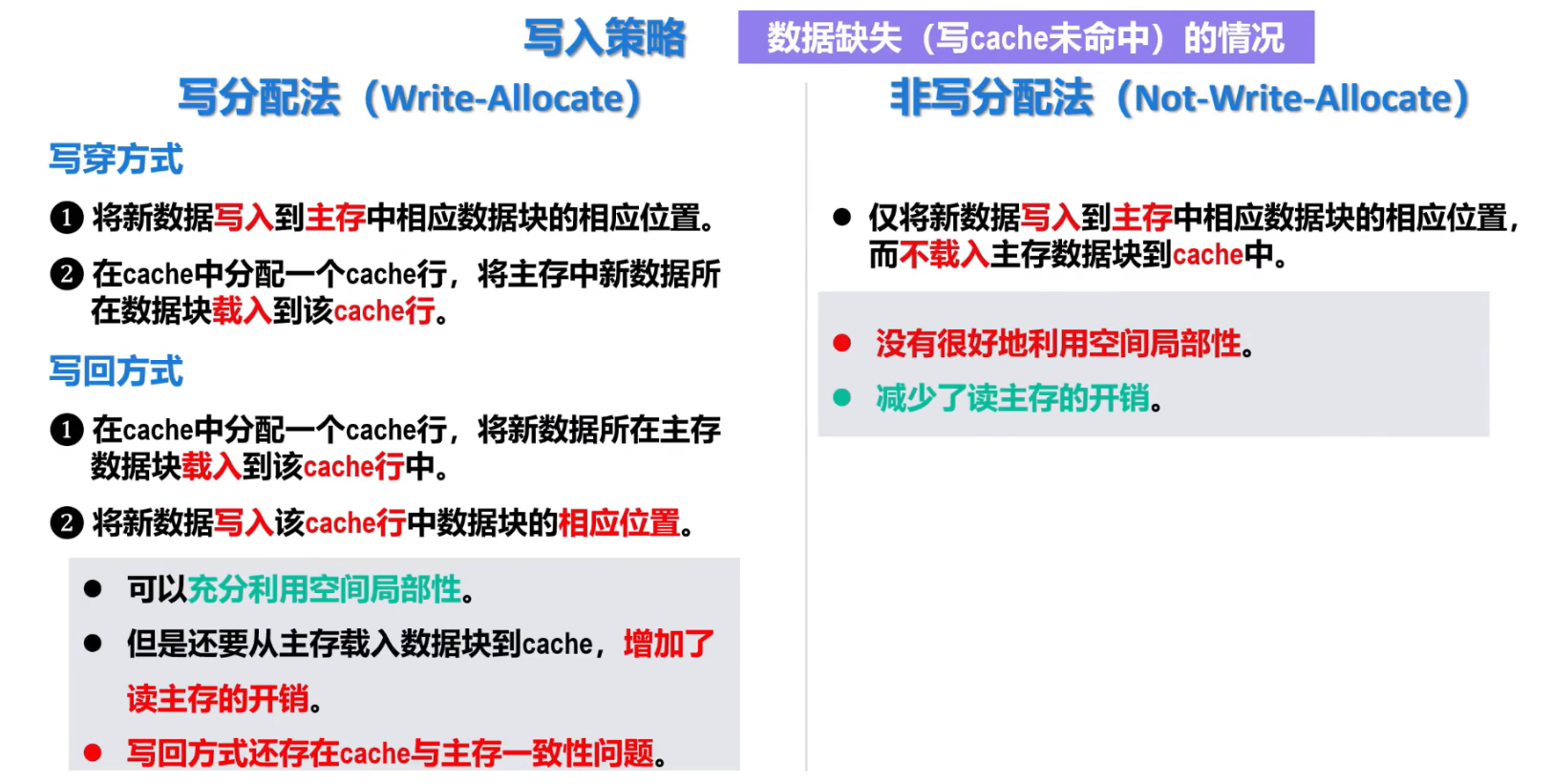

写入策略

概述

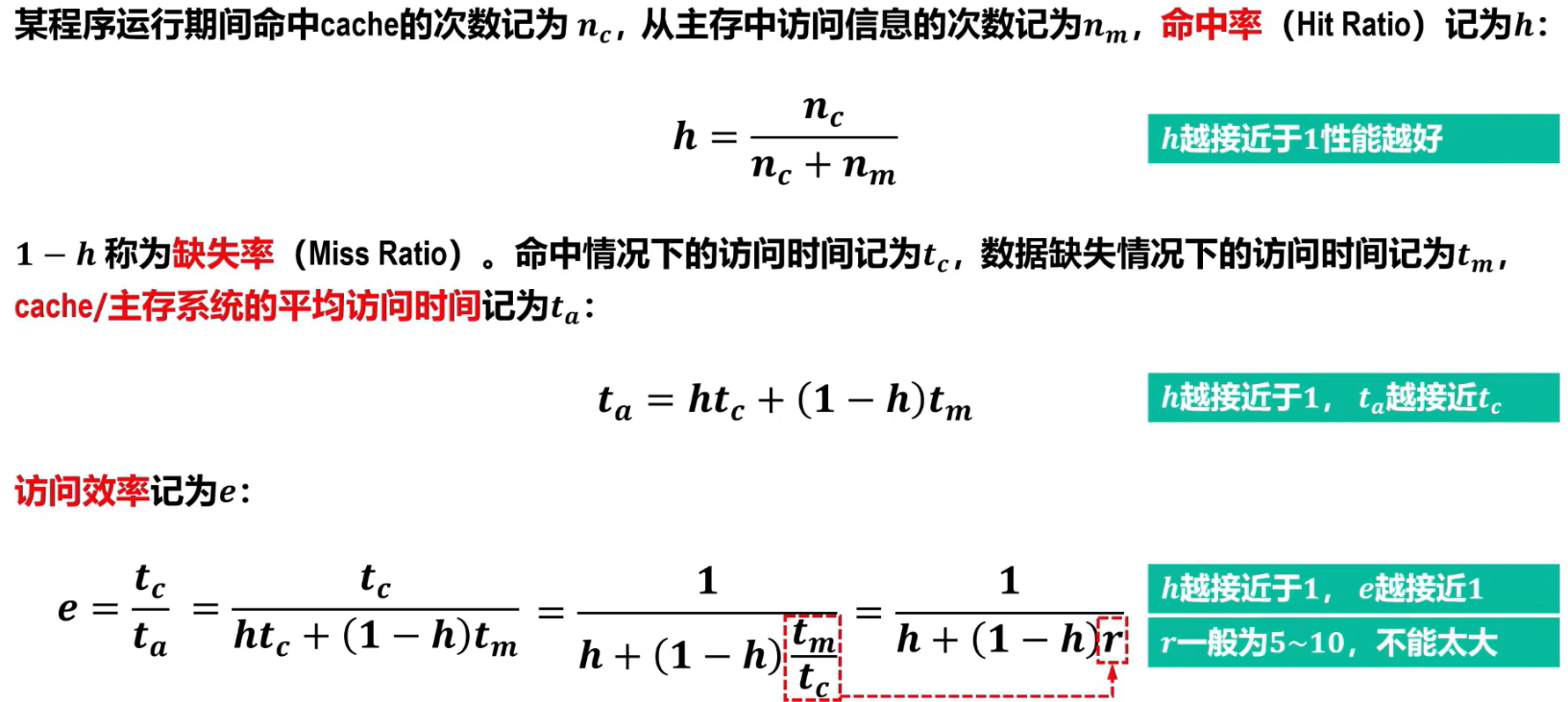

高速缓冲存储器是现代计算机系统中位于 CPU 和主存之间的高速小容量存储器,其诞生是为了解决 CPU 运算速度与主存读写速度不匹配的问题。

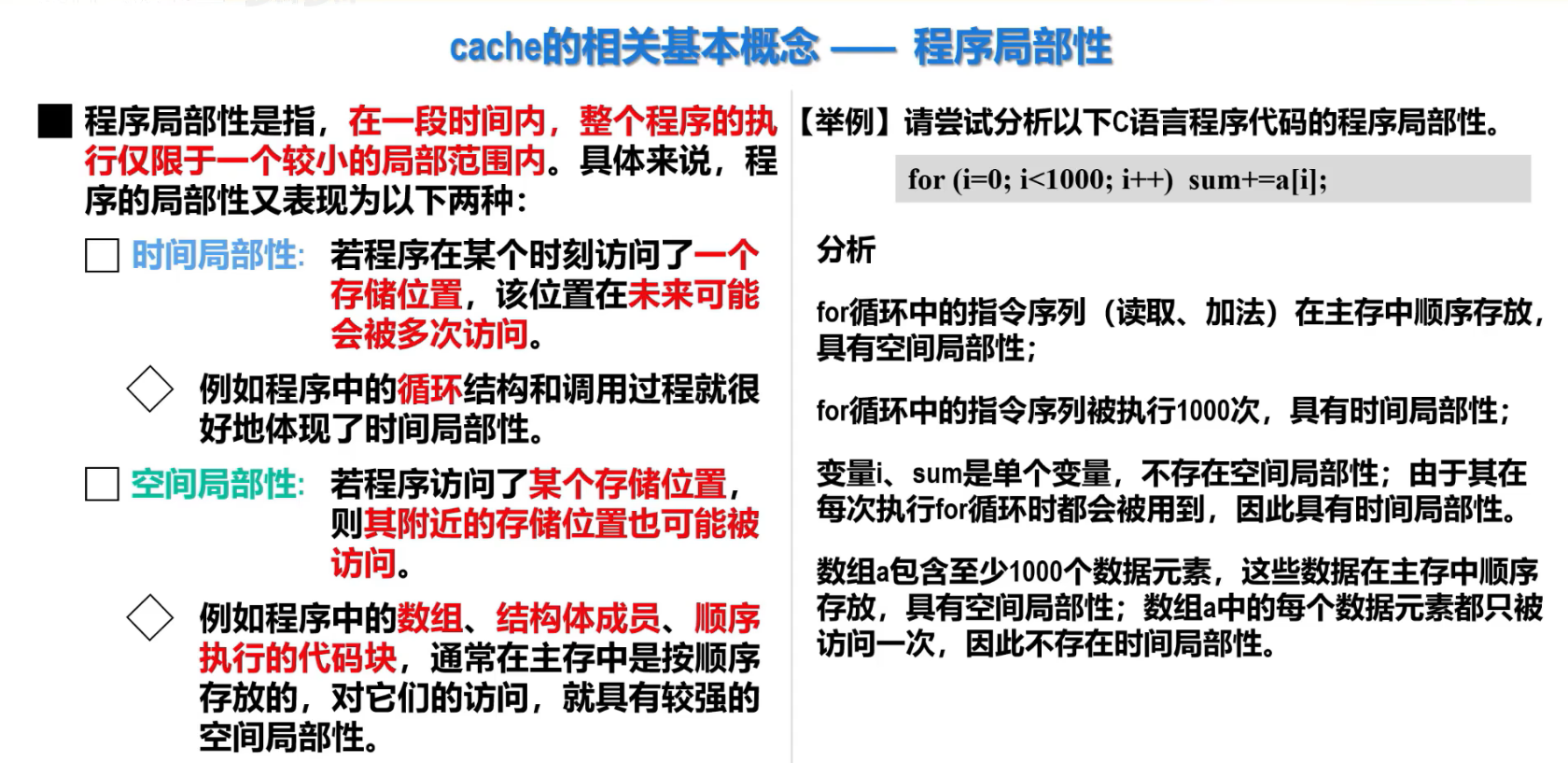

Cache 的工作原理基于程序访问的局部性原理,其核心思想是:程序在执行过程中,对内存的访问并不是随机的,而是呈现出高度的集中性,包括时间局部性和空间局部性。

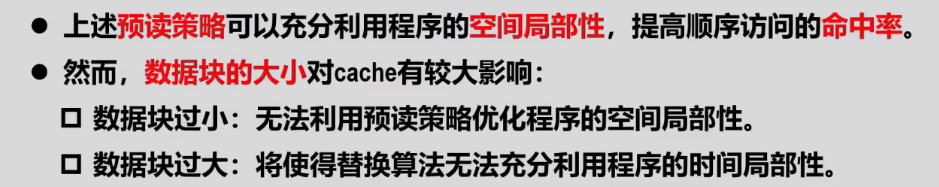

Cache 的存储单元通常以块(Block) 为单位,当访问某个数据时,Cache 会将该数据所在的整个块一起从内存加载到 Cache 中。这样,后续访问相邻数据时,可直接从 Cache 读取,无需再次访问内存。

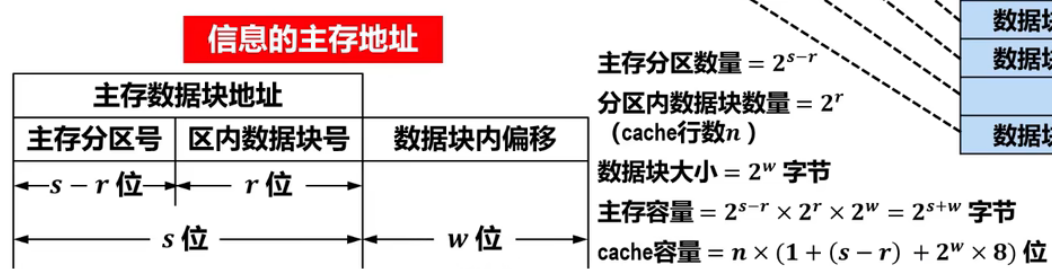

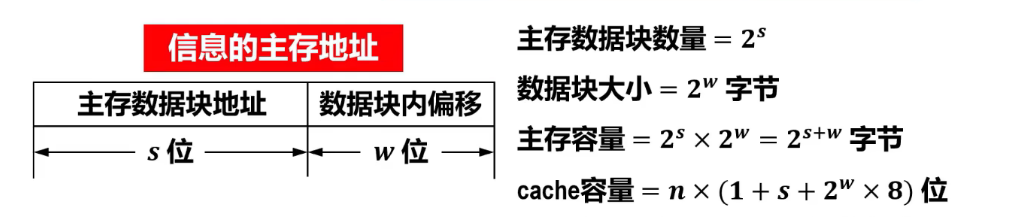

为了配合 Cache 按 “块” 加载数据的机制,主存地址通常会被划分为两个关键部分:高m位块地址和低b位块内偏移,2^m=M则表示主存的块数。同样,缓存地址也分为两段,高c位的缓存块号,低b位的块内地址,2^c=C表示缓存块数。

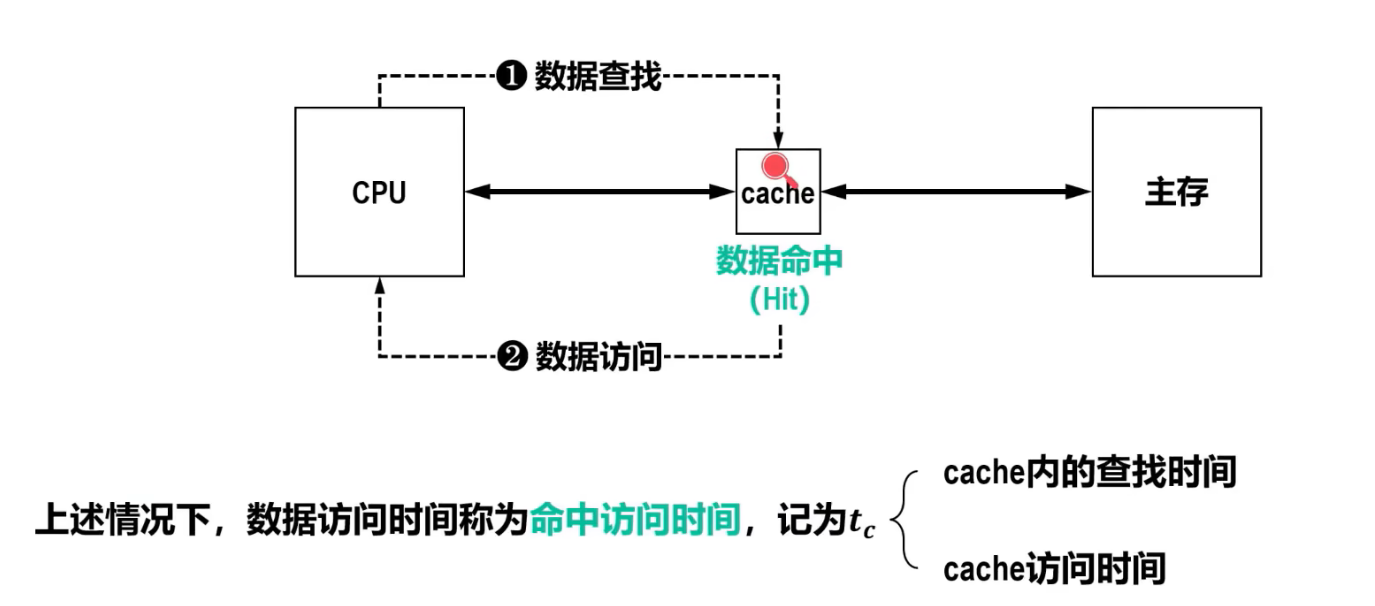

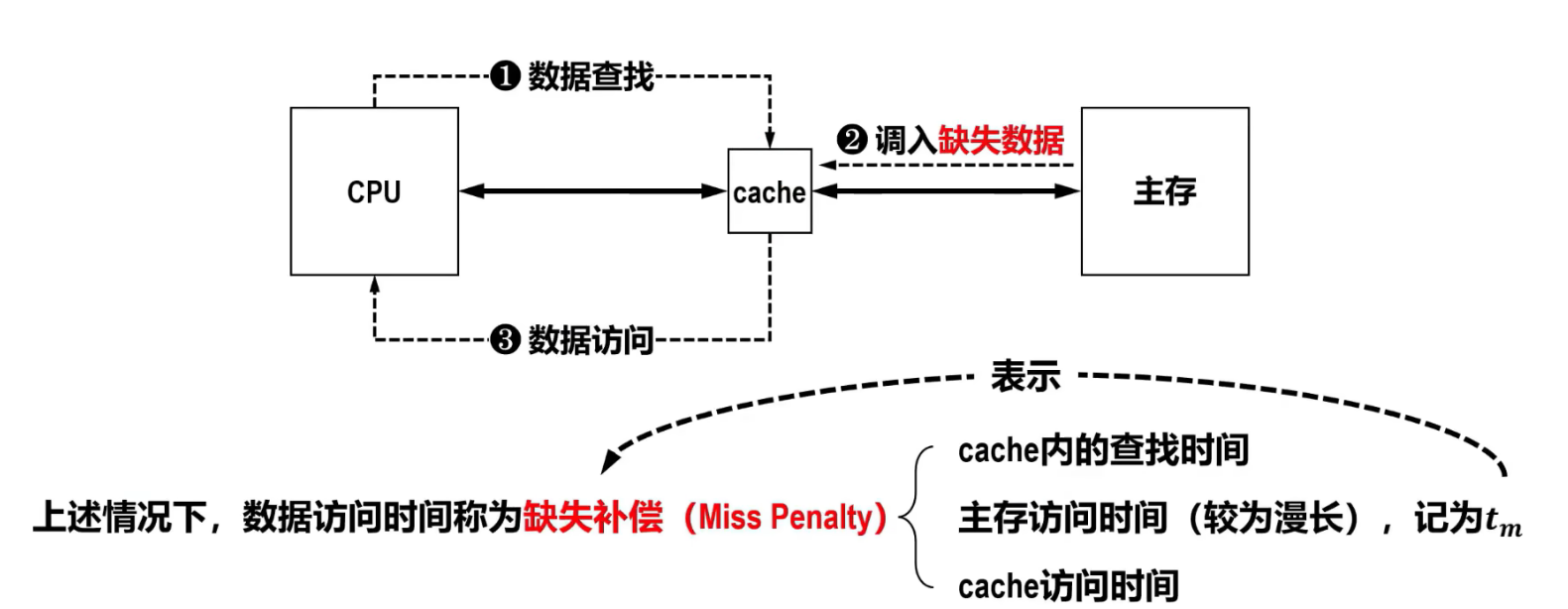

CPU 从主存读取数据时,核心差异在于是否能在 Cache 中命中目标数据,主要可分为“Cache 命中” 和 “Cache 未命中”。

读写流程

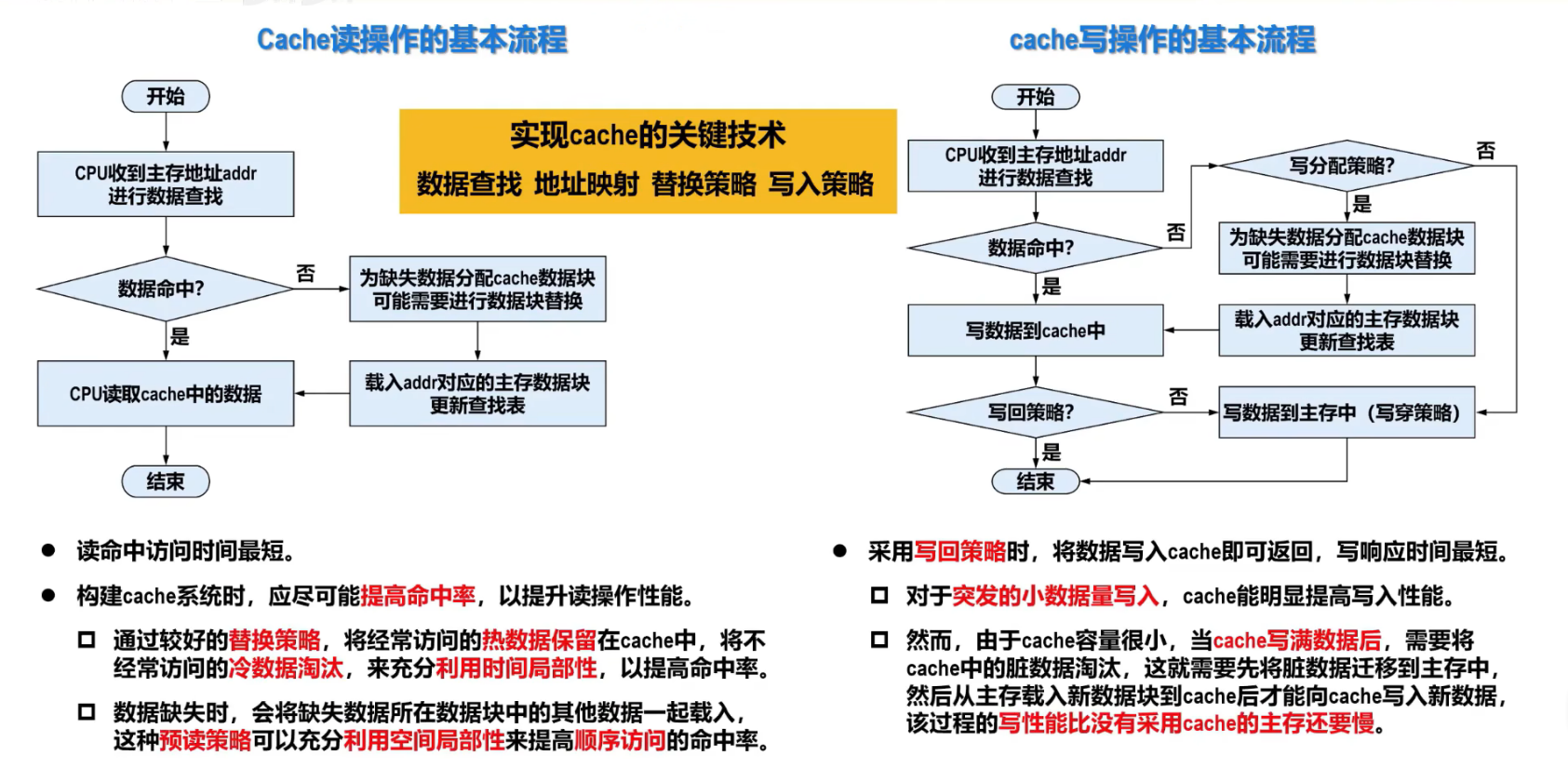

读操作

“数据查找 + 地址映射”:

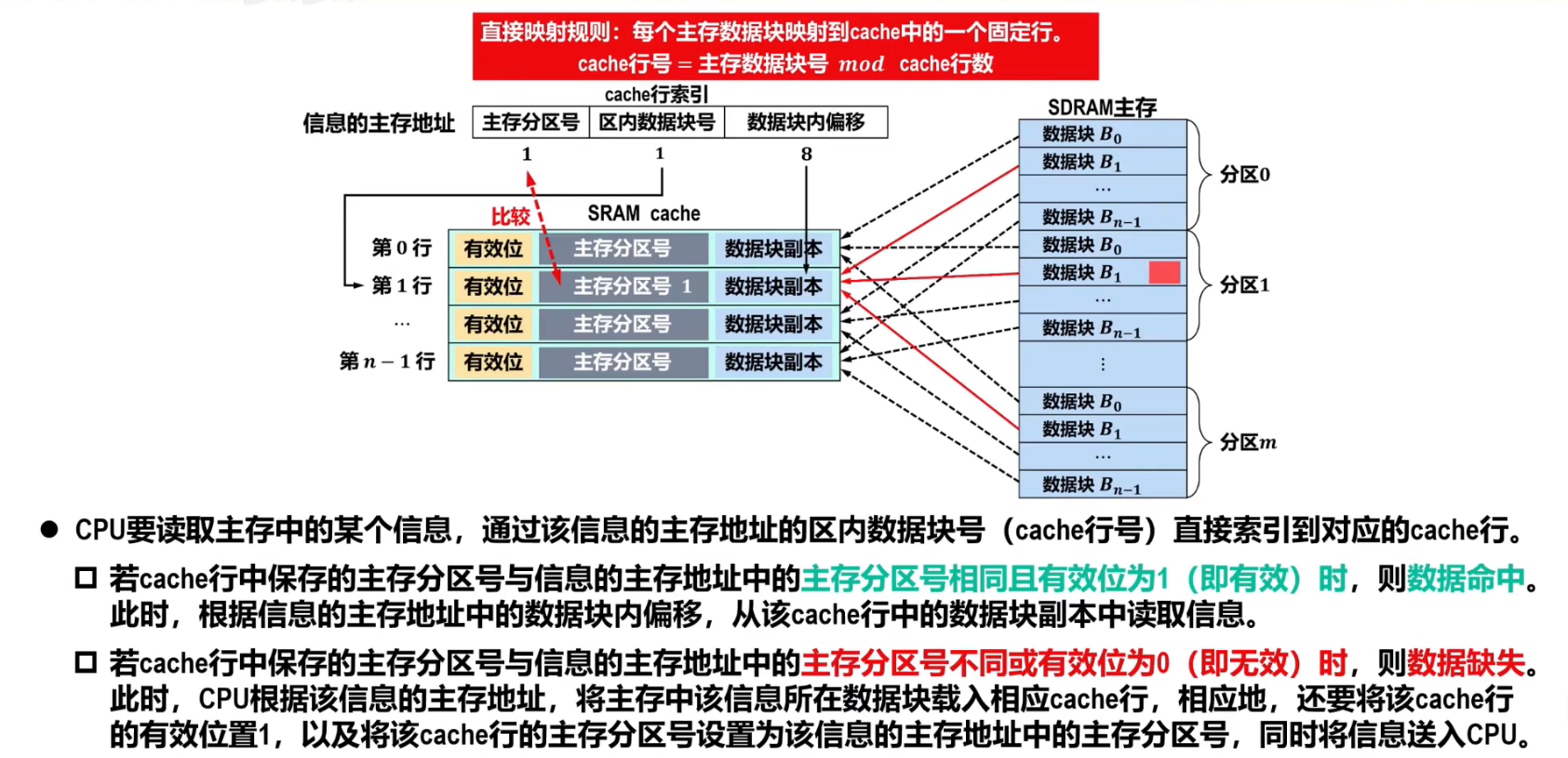

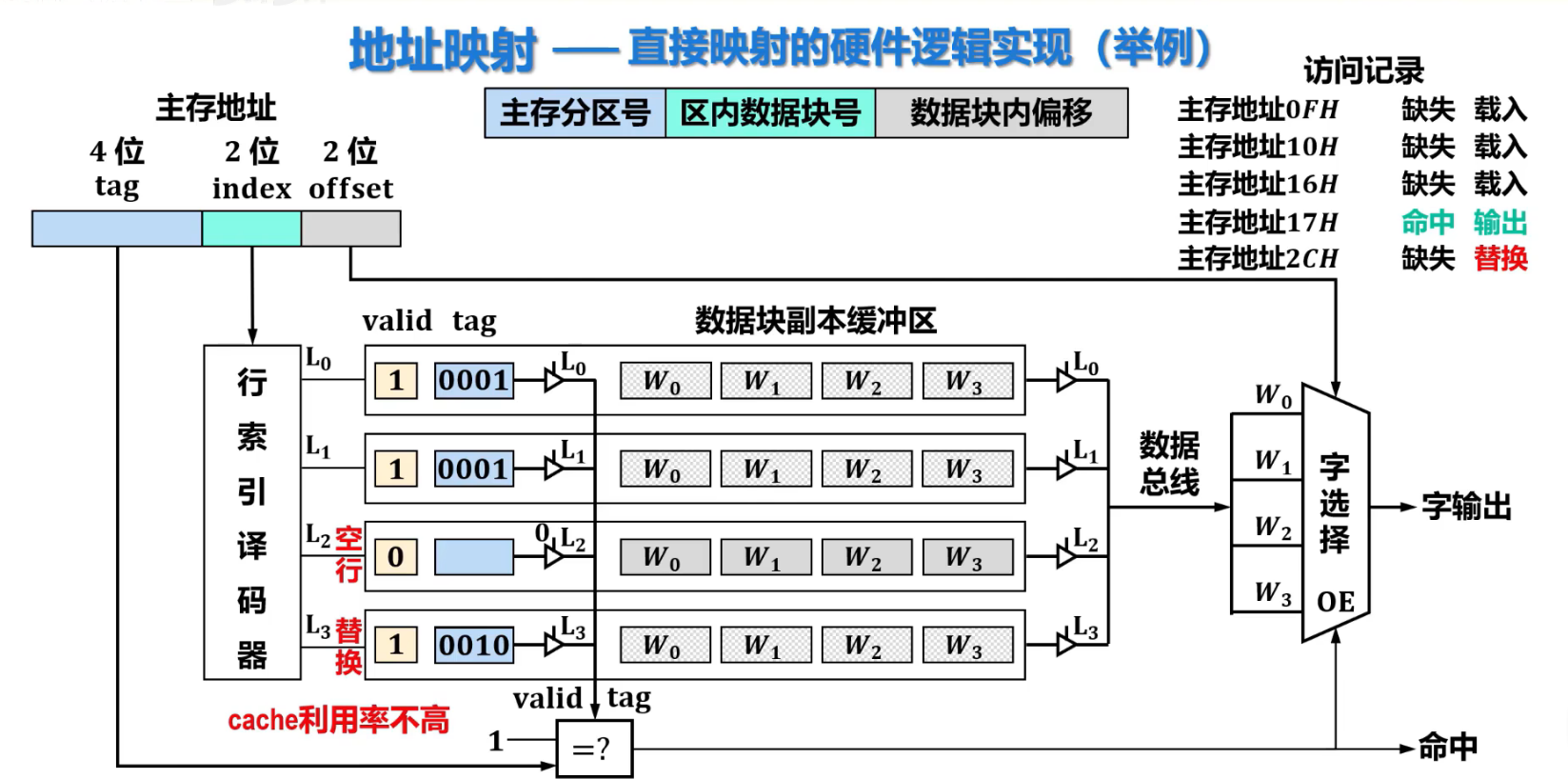

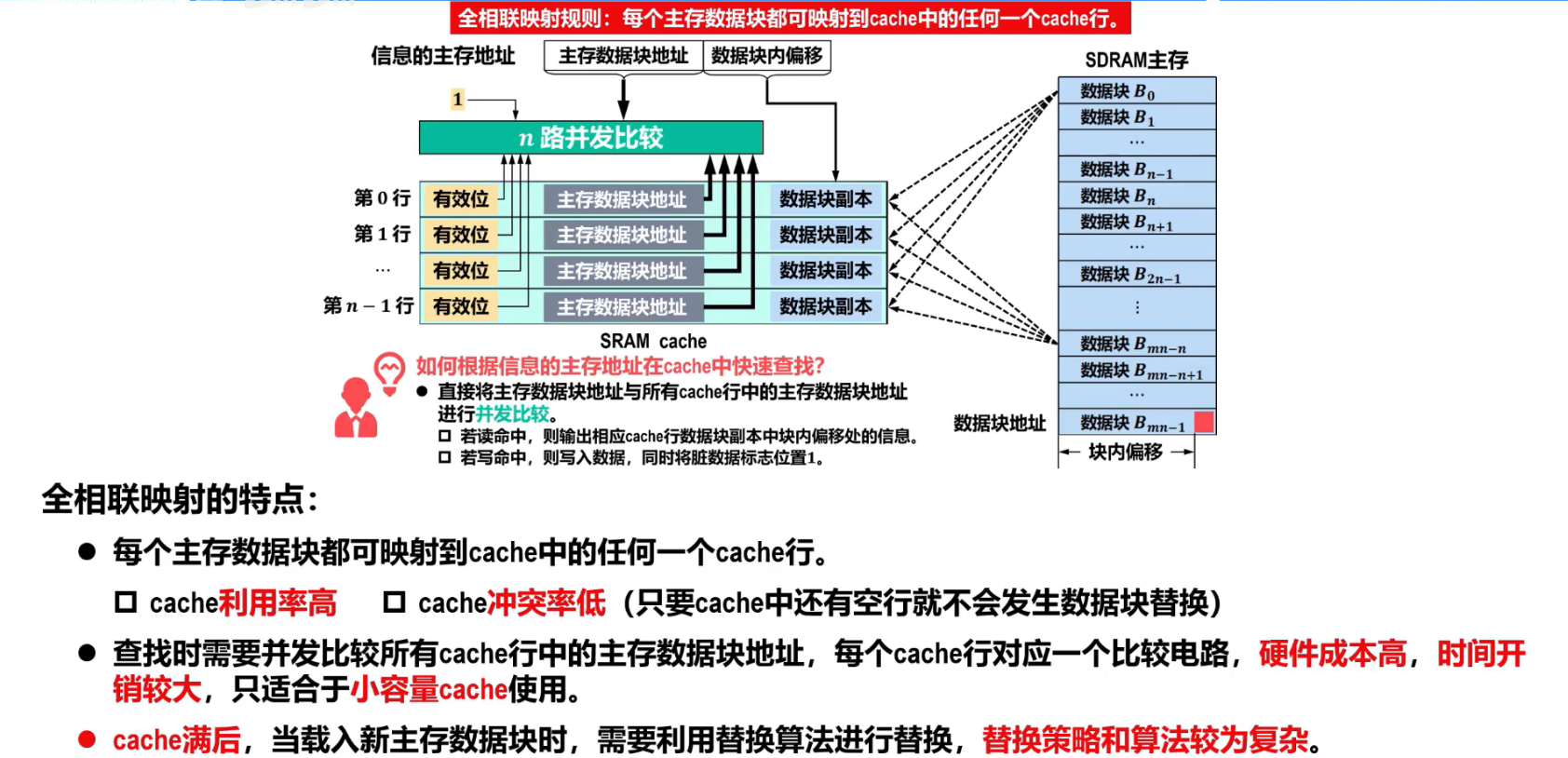

CPU 访问主存地址 addr 时,Cache 通过地址映射算法,快速判断 addr 对应的数据是否在 Cache 中。核心是将主存地址拆分为 标记(Tag)、索引(Index)、块内偏移(Offset),通过索引定位 Cache 行,通过标记确认数据归属。

“数据命中”:

Cache 行中存在 addr 对应的数据,且有效位为 1(数据未被淘汰)。此时 CPU 直接从 Cache 读取,延迟极低。

“数据缺失”:

Cache 中无 addr 对应的数据,需执行 “块替换 + 预读”:若 Cache 未满,直接分配新行;若已满,通过替换策略淘汰旧行。从主存加载 addr 所在的整个数据块,更新 Cache 行和查找表。

写操作

“写入策略”:

决定写入 Cache 后,数据何时同步回主存:

- 写回:仅写入 Cache,标记为 “脏数据”;当数据被淘汰时,再同步回主存。优点是减少主存写操作,缺点是主存与 Cache 可能出现数据不一致(需依赖脏位标记)。

- 写穿:写入 Cache 的同时,立即同步到主存。优点是主存数据始终与 Cache 一致,缺点是增加主存写操作,延迟高。

“写分配策略”:

数据缺失时,是否为写入操作分配 Cache 行:

- 写分配:分配 Cache 行,加载主存块后写入(如写回策略常用)。

- 非写分配:不分配 Cache 行,直接写入主存(如写穿策略常用)。

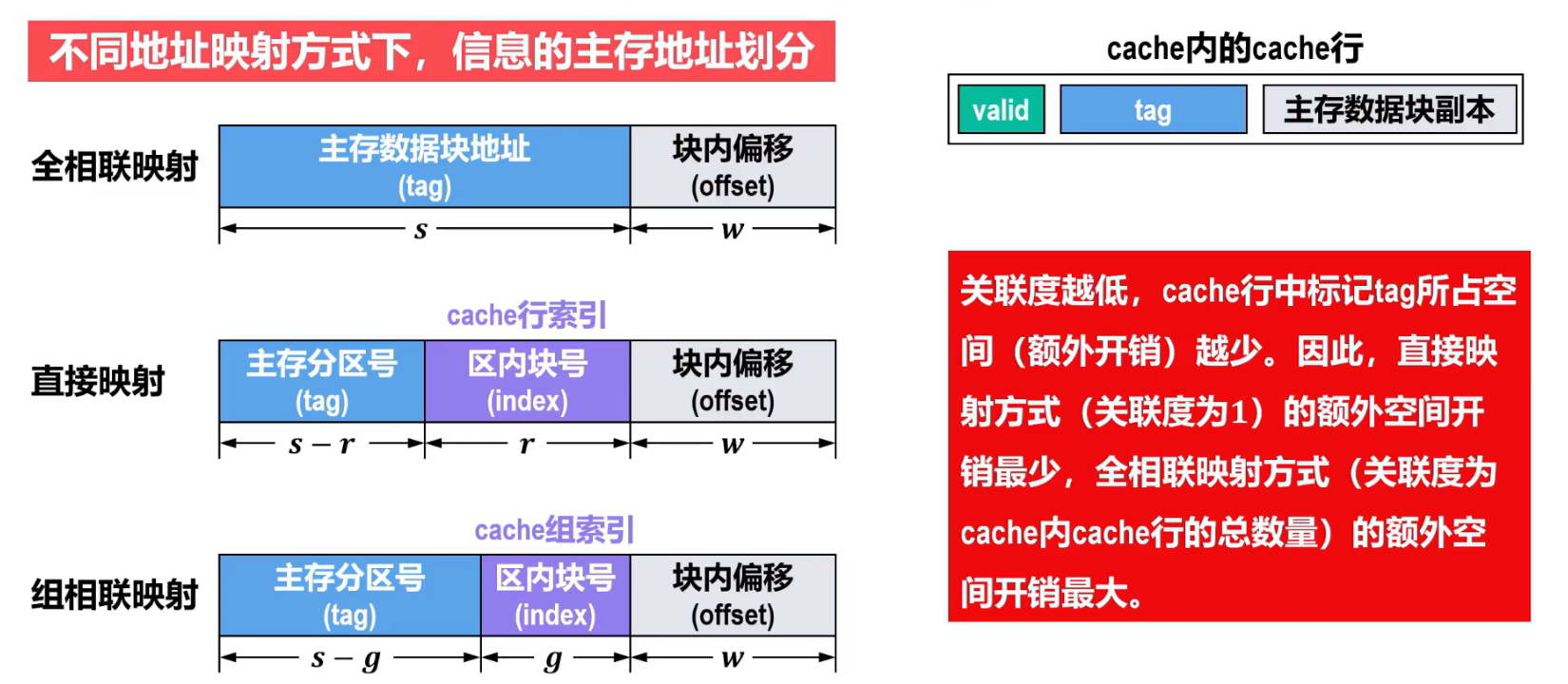

地址映射

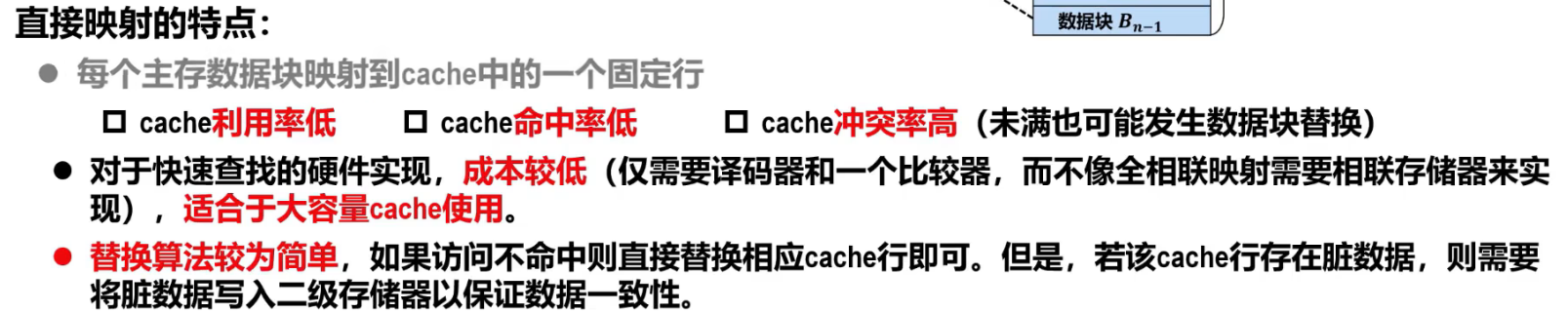

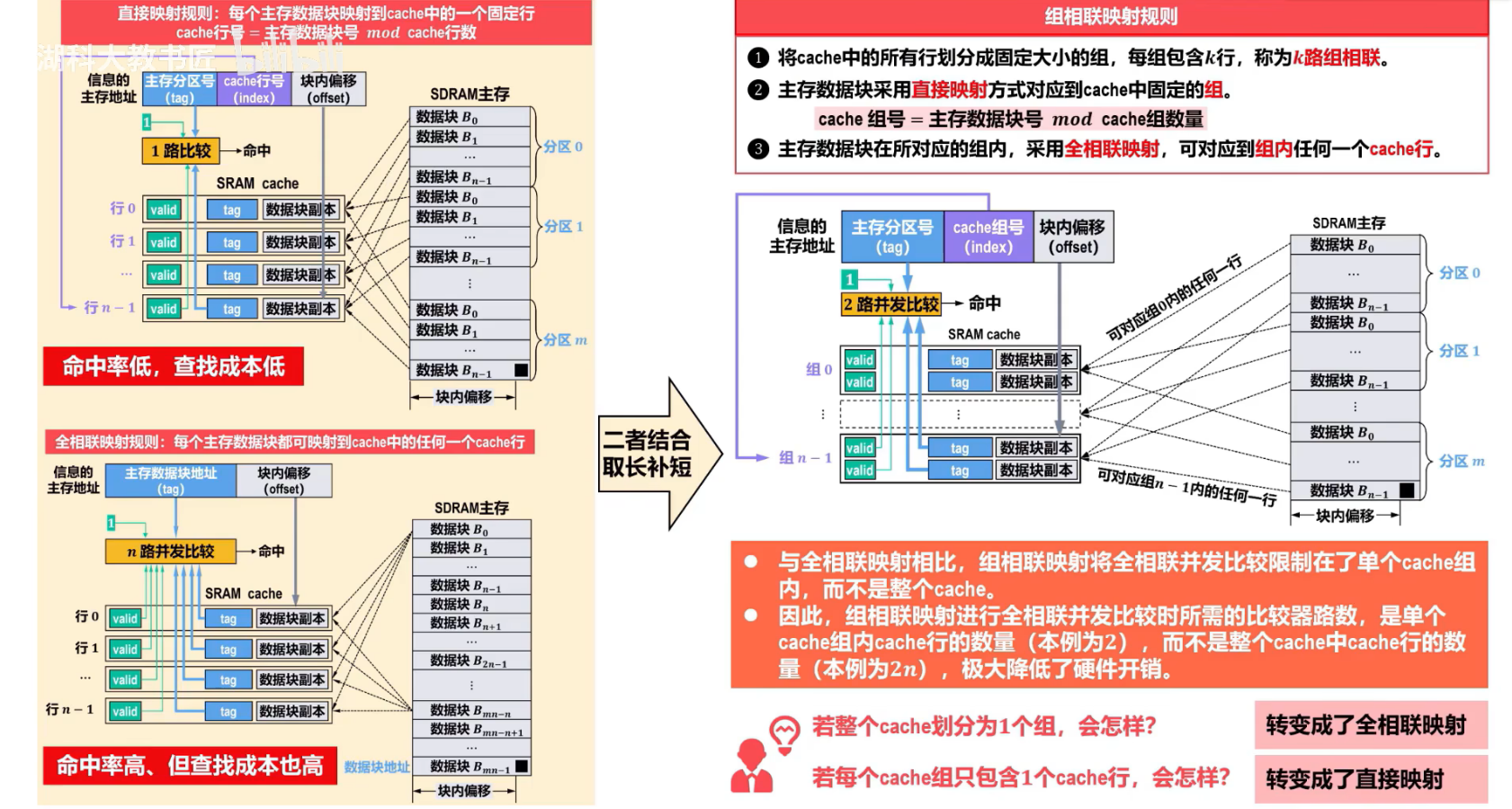

直接映射

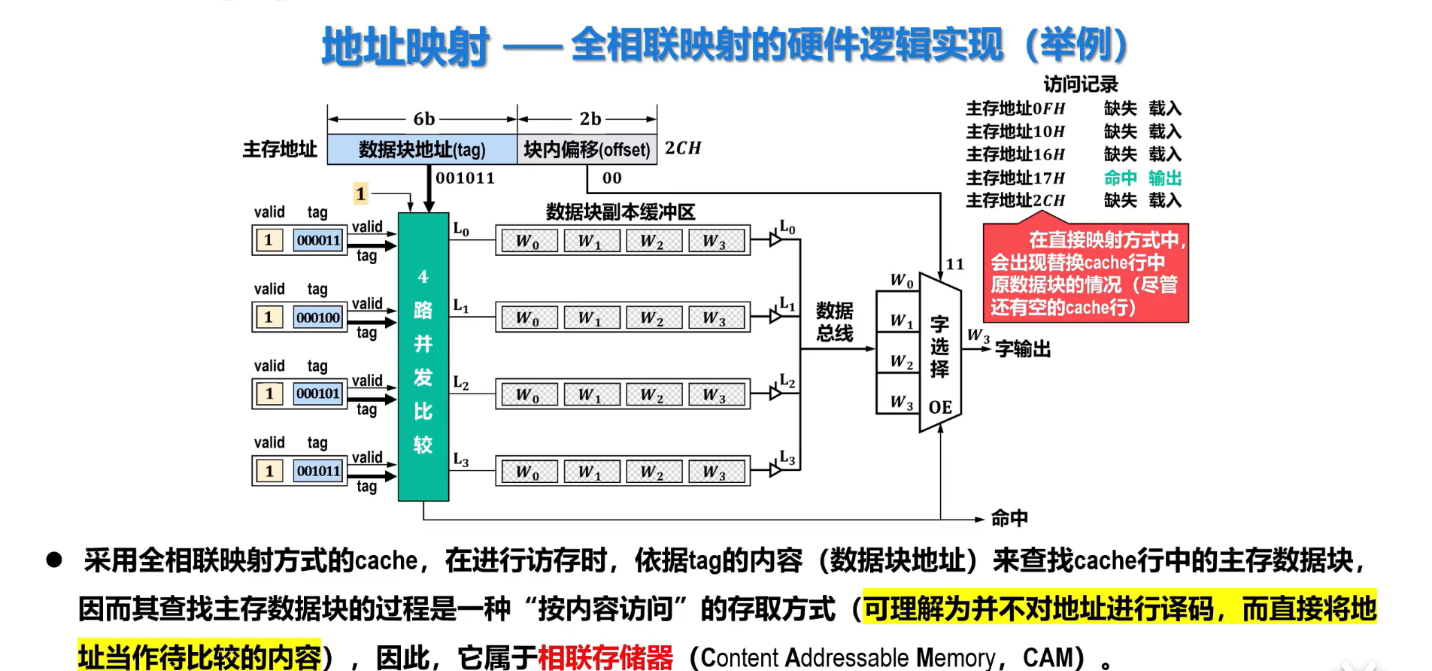

全相连映射

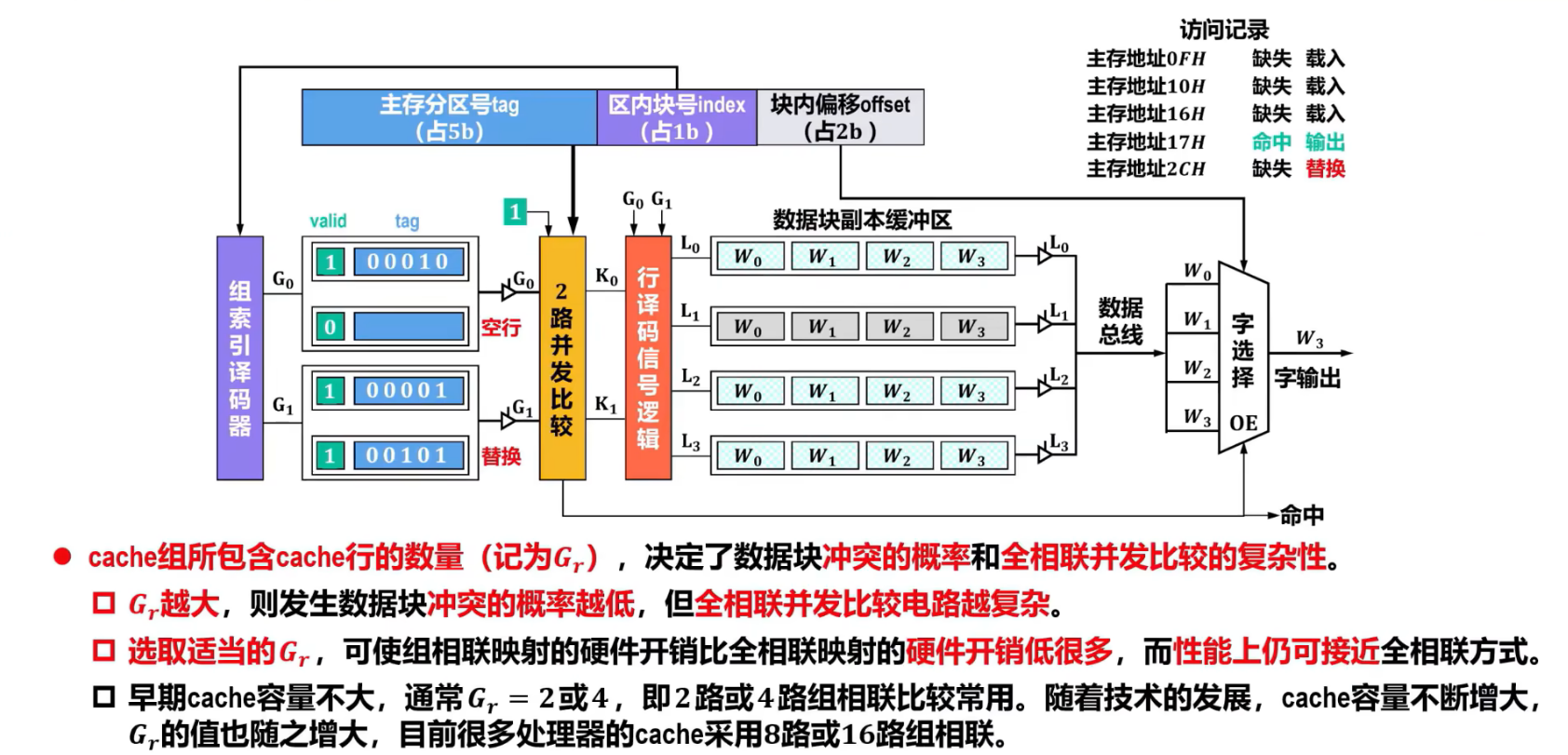

组相连映射

替换算法

写入策略

🕊️🕊️🕊️.